- •Схемотехника билеты.

- •5. Статические параметры имс.

- •6. Динамические параметры имс.

- •7. Характеристики имс.

- •13. Лэ с повышенной помехоустойчивостью.

- •14. Триггеры. Классификация.

- •16. Синхронные r-s триггеры.

- •21. Параллельные регистры.

- •22. Дешифратор. Уго дешифраторов. Принцип действия.

- •25. Мультиплексоры. Уго мультиплексоров. Принцип действия.

- •26. Демультиплексоры. Уго демультиплексоров. Принцип действия.

- •28. Накапливающий сумматор.

- •Три особенности накапливающего сумматора.

- •29. Последовательный сумматор.

- •30. Схемы сравнения параллельного типа.

- •31. Умножители двоичных чисел.

- •32. Матричная реализация булевых функций.

- •33. Программируемые логические матрицы.

- •34. Плис.

26. Демультиплексоры. Уго демультиплексоров. Принцип действия.

Демультиплексор – устройство, выполняющее функцию обратную мультиплексору. Демультиплексор имеет один информационный вход, k управляющих входов и n информационных выходов.

Так же, как и для мультиплексора, для демультиплексора справедливо выражение 2k=n. Функцию демультиплексора можно записать Fi= EKi(v), где Fi – i-ый выход, E – информационный вход, Ki(v) – комбинация на управляющих входах. Работу демультиплексора можно описать логическими уравнениями:

Функциональная схема демультиплексора 1®®4 и его таблица состояний представлены на рис. 63.

V2 |

V1 |

F0 |

F1 |

F2 |

F3 |

0 |

0 |

E |

0 |

0 |

0 |

0 |

1 |

0 |

E |

0 |

0 |

1 |

0 |

0 |

0 |

E |

0 |

1 |

1 |

0 |

0 |

0 |

E |

Рис. 63

Для дешифраторов вход E является стробирующим, а демультиплексоров – информационным. Схема демультиплексора аналогична схеме дешифратора со стробированием, поэтому в интегральном исполнении демультиплексоры рассматриваются аналогами дешифраторов.

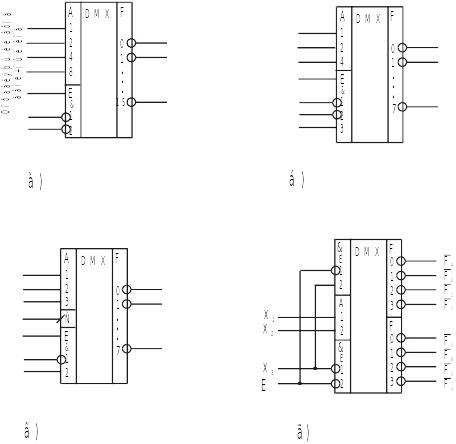

Функциональное обозначение демультиплексоров DMX. Обозначения DMX или DC на УГО ИМС используются, исходя из реализуемой функции. Для дешифраторов выполняется преобразование kn, а для демультиплексора 1n.

Рис. 64

В качестве примера на рис. 64 приведены УГО ИМС демультиплексоров.

ИД3 – демультиплексор 1®®16 (а).

ИД7 – демультиплексор 1®®8 (б).

74ALS131 – демультиплексор 1®®8 с адресными регистрами (в).

Аналогично дешифраторам осуществляется каскадирование демультиплексоров. На рис. 64, г представлена схема демультиплексора 1®®8 реализованного на ИМС ИД4 (сдвоенный демультиплексор 1®®4).

27. Сумматоры. Типы сумматоров. УГО сумматоров.

Сумматоры предназначены для выполнения операций сложения и вычитания как двоичных, так и десятичных чисел, а также используются для построения различных решающих цифровых устройств.

Сумматор (двоичный) – комбинационная схема, выполняющая сложение двух двоичных чисел x и y.

Сложение разрядов осуществляется по единым правилам, т.е. в каждом i-том разряде осуществляется сложение – xi и yi и Ci-1 – перенос от сложения предыдущих разрядов. Результат сложения представлен суммой Si и переносом Сi в старший i+1 разряд.

Сумматоры подразделяются на полусумматоры, имеющие два входа (отсутствует вход переноса), полные сумматоры, имеющие три входа.

Полусумматоры описываются следующими функциями:

.

.

Полные сумматоры описываются выражениями следующего вида:

,

,

.

.

Используя аксиомы алгебры логики, можно по-разному преобразовать приведенные выражения, исходя из базиса используемых ИМС.

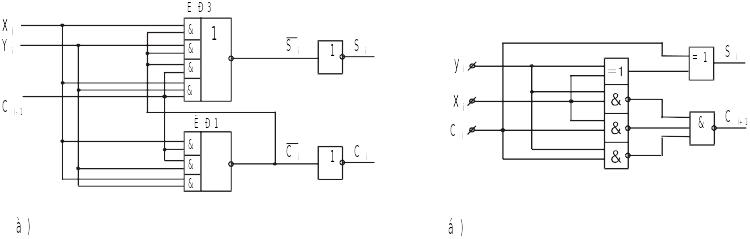

Для указанных выражений наиболее удобны логические ИМС типа ЛР, которые оптимальным образом позволяют реализовать функции для S и С (рис. 65,а).

Рис. 65

После преобразования приведенных выражений можно получить:

;

;

.

.

Исходя из этих выражений, схема полного сумматора примет вид, изображенный на рис. 65,б. В данной схеме удобно использовать ЛЭ ‘’Исключающее ИЛИ’’.

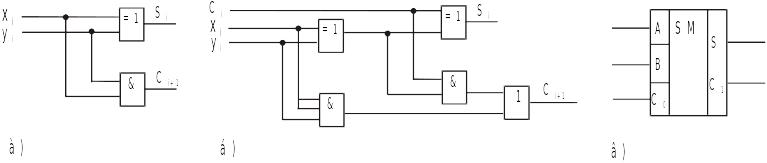

Схема полусумматора может быть реализована на двух логических элементах (рис. 66,а), а используя две схемы полусумматоров, можно реализовать полный сумматор (рис. 66,б). УГО сумматора представлено на рис. 66,в.

Рис. 66