- •Схемотехника билеты.

- •5. Статические параметры имс.

- •6. Динамические параметры имс.

- •7. Характеристики имс.

- •13. Лэ с повышенной помехоустойчивостью.

- •14. Триггеры. Классификация.

- •16. Синхронные r-s триггеры.

- •21. Параллельные регистры.

- •22. Дешифратор. Уго дешифраторов. Принцип действия.

- •25. Мультиплексоры. Уго мультиплексоров. Принцип действия.

- •26. Демультиплексоры. Уго демультиплексоров. Принцип действия.

- •28. Накапливающий сумматор.

- •Три особенности накапливающего сумматора.

- •29. Последовательный сумматор.

- •30. Схемы сравнения параллельного типа.

- •31. Умножители двоичных чисел.

- •32. Матричная реализация булевых функций.

- •33. Программируемые логические матрицы.

- •34. Плис.

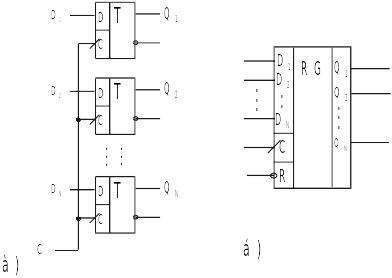

21. Параллельные регистры.

Регистрами называются устройства, выполняющие функции приема, хранения и передачи информации. Параллельные регистры выполняют указанные операции одновременно для N-разрядов числа. Функционально параллельный регистр представляет собой совокупность синхронных триггеров (как правило D-триггеров) с общим тактовым входом (входом синхронизации или загрузки регистра) [6].

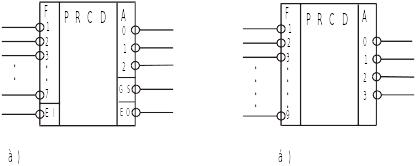

Условно регистры обозначаются RG (иногда допускается обозначение триггера – Т). На рис. 40 представлены функциональная схема (а) и УГО регистра (б).

Рис. 40

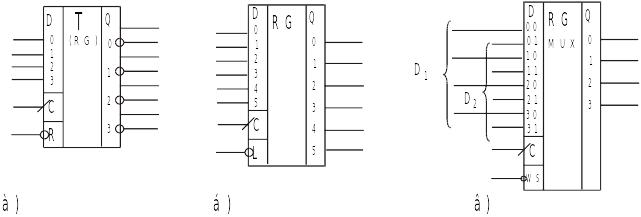

Промышленность выпускает ряд ИМС, выполняющих функции параллельного регистра [2,3,19]. ТМ8 4 D-триггера с общими управляющими сигналами C и R (рис. 41, а). Такой набор триггеров можно рассматривать как 4-х разрядный параллельный регистр. ТМ9 – 6-разрядный регистр (D-триггеры). ИР35 – 8-разрядный параллельный регистр. ИР18 – 6-разрядный регистр, имеющий вход разрешения загрузки L (рис. 41, б).

Рис. 41

Данные регистры осуществляют загрузку данных через D-входы при разрешении загрузки L=0 и при поступлении переднего фронта синхроимпульса С.

Для расширения возможностей параллельных регистров в некоторые из них вводят дополнительную функцию выбора входных данных при записи. Эта функция управляется сигналом WS (Word Select - выбор слова).

ИР20 – 4-х разрядный параллельный регистр с выбором данных (рис. 41, в).

DO – выходные данные, DI – входные данные

Рис. 42

При WS =1 в регистр по фронту С записываются данные D2, при WS = 0 данные D1.

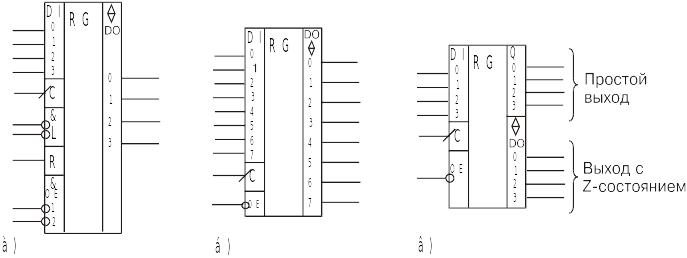

Для работы на шины выпускаются параллельные регистры с Z-состоянием по выходу. Такие регистры имеют управляющий вход ОЕ.

ИР15, ИР14 – 4-х разрядные регистры, с Z-состоянием (рис. 42,а). ИР23, ИР37,.ИР41, ИР2 – 8-разрядные регистры с Z-состоянием (рис. 42, б). 1804ИР1 – 4-х разрядный регистр с двойным выходом (рис. 42,в).

22. Дешифратор. Уго дешифраторов. Принцип действия.

Дешифратор – это комбинационная логическая схема, преобразующая цифровой код, поступающий на вход, в управляющий сигнал только на одном из выходов. На вход классического дешифратора поступает двоичный код разрядностью N. Количество выходов в этом случае равно 2N, т.е. дешифратор преобразует двоичный код в унитарный. Дешифратор реализует 2N функций [6].

Данная система функций характеризует так называемый полный дешифратор. На практике возможны неполные дешифраторы, реализующие только часть вышеуказанных функций.

В зависимости от разрядности входного кода и архитектуры логических элементов дешифратор может быть реализован на основе одноступенчатой (или линейной) и многоступенчатой схемы.

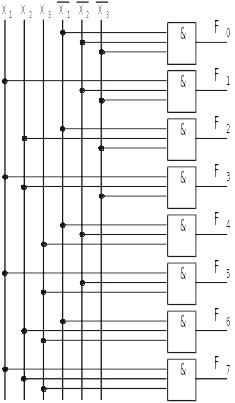

В интегральном исполнении распространение получили линейные дешифраторы. В них каждая функция Fi реализуется на отдельном конъюнкторе, имеющем N входов и один выход.

Линейный дешифратор на 3 входа и 23=8 выходов представлен на рис. 43.

Рис. 43

Для формирования функций F требуется парофазный код входных величин. Функционально дешифратор обозначают DC (decoder). Иногда дешифраторы характеризуют количеством входов и выходов, например: 3´ґ8 (полный), 4´ґ10 (не полный), 4´ґ16 (полный).

Реальные ИМС дешифраторов имеют инверсные выходы – т.е. активный выход имеет уровень лог. «0», а неактивные – лог. «1». Это позволяет значительно снизить потребление энергии ИМС, т.к. лог. «0» на выходе означает открытый выход ИМС.

Многоступенчатые дешифраторы – матричные прямоугольные и пирамидальные не нашли широкого применения в ИМС по причине увеличения задержки распространения сигнала от входа к выходу из-за увеличения количества каскадов.

Для реализации дешифраторов по специальным алгоритмам используются программируемые ПЗУ, которые в этом случае называются преобразователями кодов.

23. Каскадирование дешифраторов.

Дешифраторы, имеющие входы разрешения дешифрации, можно соединять для увеличения числа комбинаций. Например, из ИД4, сдвоенного дешифратора 2´ґ4, введением дополнительных связей можно получить дешифратор 3´ґ8 (рис. 47, а).

Объединением двух дешифраторов ИД7 (3´ґ8) реализуется дешифратор 4´ґ16 (рис. 47, б).

24. Шифраторы.

Шифраторы выполняют обратное дешифраторам преобразование, т.е. на вход шифратора подается унитарный код, а на выходе формируется соответствующий двоичный код. Приведенная таблица описывает шифратор 4´ґ2.

-

F3

F2

F1

F0

A1

A0

0

0

0

1

0

0

0

0

1

0

1

0

1

1

0

1

1

1

Для шифратора должно выполняться условие Fi Fj=0, при i¹№j. Если сигналы Fi поступают от независимых источников, то это условие невыполнимо. В этом случае каждому входу необходимо назначить свой приоритет. Принято считать, что чем больше номер входа i, тем выше его приоритет. Шифратор выдает двоичный код числа i, если Fi=1, а на все входы Fj, имеющие больший приоритет, поданы «нули». Такие шифраторы называются приоритетными. Функциональное обозначение шифраторов ИВ ( на УГО ИМС – PRCD – приоритетный шифратор).

В качестве примера ниже приведены некоторые типы ИМС шифраторов.

ИВ1 – шифратор 8´ґ3 (рис. 49, а). ИВ2 аналогичен ИВ1, но имеет выходы с Z-состоянием. EI – выключение шифратора. GS (Group Signal) – выходной сигнал, говорящий о наличии хотя бы одного входного Fi, при включенном шифраторе, т.е. при EI=1 и Fi=1, хотя бы для одного i, GS=1. ЕО – выключение выхода, указывающий на отсутствие сигналов на входе при включенном шифраторе, т.е. при EO=1 и EI=1 Fi=0 для всех i. Выходной двоичный код можно считывать с шифратора только при GS=1. ИВ3 – приоритетный шифратор 10´ґ4 (десятая комбинация - на все входы поданы лог. «0», на выходе – активный выход АО)(рис. 49, б).

Рис. 49

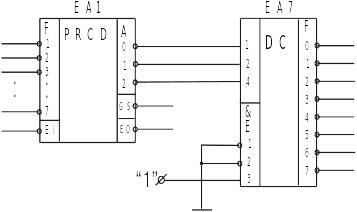

Одним из важных приложений шифраторов является построение преобразователей произвольного n-разрядного кода в N-разрядный унитарный код. Например: преобразование 8-разрядного кода, для разрядов которого установлены определенные приоритеты, в 8-разрядный унитарный код (рис. 50). В данной схеме преобразователя

Рис. 50

шифратор преобразует произвольный код в двоичный 3-х разрядный, а дешифратор 3´ґ8 преобразует этот код в инверсный унитарный.