3.4Ядра процесора

Як відомо, процес обробки даних процесором включає кілька етапів. У простому випадку можна виділити чотири етапи обробки команди: - вибірка з кешу; - декодування; - виконання; - запис результатів.

Рис.2.7 ядро процесора Спочатку інструкції і дані забираються з кеша L1, який розділений на кеш даних D-cache і кеш інструкцій I-cache, - цей процес називається вибіркою. Потім вибрані з кешу інструкції декодуються в зрозумілі для даного процесора примітиви (машинні команди) - такий процес називається декодуванням. Далі декодовані команди надходять на виконавчі блоки процесора, виконуються, а результат записується в оперативну пам'ять. Процес вибірки інструкцій з кеша, їх декодування і просування до виконавчих блокам здійснюються в предпроцесорі (Front End), а процес виконання декодований команд - в постпроцесорі, званому також блоком

виконання команд (Execution Engine). Стадії обробки команд прийнято називати конвеєром обробки команд, а розглянутий нами конвеєр є чотириступінчастим. Зауважте, що кожну з цих щаблів команда проходить за один процесорний такт. Відповідно для примітивного чотириступінчастою конвеєра на виконання однієї команди відводиться чотири такти. Звичайно, розглянутий нами процесор є гіпотетичним. У реальних процесорах конвеєр обробки команд складніше і включає більшу кількість ступенів. Причина збільшення довжини конвеєра полягає в тому, що багато команд є досить складними і не можуть бути виконані за один такт процесора, особливо при високих тактових частотах. Тому кожна з чотирьох стадій обробки команд (вибірка, декодування, виконання і запис) може складатися з декількох ступенів конвеєра.Власне, довжина конвеєра - це одна з найбільш значущих характеристик будь-якого процесора.

Кеш першого рівня (L1): 64 КБ + 64 КБ (дані + інструкції).

Кеш другого рівня (L2): 512 КБ.

Кеш третього рівня (L3): 6 МБ.

Флаги: MMX, Extended 3D Now, SSE, SSE2, SSE3, AMD64, Cool’n’Quiet 2.0, NX-Bit, AMD Virtualization.

Роз'єм: Socket F.

Напруга ядра: 1,2 - 1375 В, потужність: 68 Вт - 120 Вт (TDP) 55 Вт - 105 ВТ (ACP),технологія: 45 нм (SOI).

Тактові частоти: 2,5 ГГц - 2,7 ГГц Модель SE (ACP 95 Вт):8384 2.7Ггц, 2.6ГГц 8382, 8380 2.5Ггц.

Cool'n'Quiet - технологія зниження швидкості і енергоспоживання центрального процесора Її дія полягає в зниженні частоти і напруги при неповній завантаженості ЦП. Мета даної технології - знизити загальне енергоспоживання і тепловиділення, дозволяючи тим самим зменшити швидкість обертання вентилятора.

BIOS в ході початкового завантаження створює для процесора опис можливих його станів (P-States, стану продуктивності), якi характеризуються комбінацією частоти і робочої напруги. Ці описи відповідно до інтерфейсом ACPI зчитуються операційною системою при запуску. В ході роботи операційна система стежить за завантаженням процесора, і якщо вона не максимальна, робить спробу перевести процесор в один з молодших станів. Для цього система звертається до драйвера процесора. Драйвер програмує регістри процесора, запускаючи процедуру переходу в запрошений стан. Знизивши частоту і напругу, процесор буде споживати менше енергії (приблизно в два-три рази), а значить, буде менше нагріватися. Шум теж знизиться, якщо кулер має термоконтроль.

3.5 Кеш-пам’ять

900-та серія: флагманська серія з повним комплектом ядер і включеним кешем-пам'яті L3.

800-та серія: Ці чіпи з дефектом у кеш-пам'яті L3; 2 MB відключені, в результаті чого чіп отримує 4 МБ кеш-пам'яті L3 та всі ядра в повному обсязі

700-та серія: Ці чіпи мають одне відключене ядро, залишається три (продаються як «X3») і забезпечені повною кеш-пам'яттю L3.

500-та серія: Ці чіпи мають два браковані ядра, залишаються два робочі (продаються як «X2») і забезпечені повною кеш-пам'яттю L3.

В багатопроцесорних системах ЦПУ взаємодіють між собою з використанням архітектури Direct Connect Architecture за допомогою високошвидкісної шини HyperTransport. Кожен процесор може дістати доступ до пам'яті іншого процесора прозоро для програміста. На відміну від звичайного симетричного мультипроцесора, в Opteron використовується технологія NUMA (Non-Uniform Memory Access), коли замість виділення одного банку пам'яті для всіх ЦПУ, кожен процесор має «свою» пам'ять. Процесори Opteron безпосередньо підтримують 8-ми процесорні конфігурації, зазвичай вживані в серверах середнього рівня. Могутніші сервера використовують додаткові дорогі чипи маршрутизації для підтримки більше 8 ЦПУ на плату.

3.6 Шина HyperTransport (HT)

Шина HyperTransport (HT), раніше відома як блискавка Data Transport (LDT), - це двонаправлена послідовно / паралельна комп'ютерна шина з високою пропускною здатністю і малими затримками. Для розробки і просування даної шини бувутворений консорціум HyperTransport Technology. Технологія використовується AMD і Transmeta в x86-процесорах, PMC-Sierra, Broadcom і Raza Microelectronics - в процесорах MIPS, NVIDIA, VIA, SiS, ULi / ALi, AMD, Apple Computer і HP - в наборах системної логіки для ПК, HP, Sun Microsystems, IBM і IWill- в серверах, Cray, Newisys і PathScale - в суперкомп'ютерах, а також компанією Cisco Systems - в маршрутизаторах.

3.7 Платформа Maranellо

Maranello - це одна з перших платформ AMD за останні 10 років вона заснована на чіпсетісамоїї компані

Чіпсет 5600-серії має функцію введення / виводу, технологію HyperTransport 3.0, а також PCI Express 2.0. Нова платформа AMD Opteron сумісна з 2P і 4P, а також буде сумісна з запланованими процесорами, заснованими на ядрі серверного процесора нового покоління, з кодовою назвою«Bulldozer».

Процесори AMD Opteron «Magny-Cours» з 8 і 12 ядрами розроблені для платформи AMD G34 «Maranello» для процесорів Opteron 60xx серії, з чотирьох канальним інтерфейсом пам'яті DDR3, 2 або 4 процесорні роз'єми, до 12 модулів пам'яті на 1 роз'єм. Платформа Maranello замінює 4P, так як ті ж процесори можуть бути використані в обох 2-х і 4-х смугових конструкціях

4 ТЕОРЕТИЧНІ АСПЕКТИ ВИКОРИСТАННЯ КОМП’ЮТЕРНОЇ СИСТЕМИ AMD Opteron

4.1 Різниця між серверними і десктопними процессорами

При виробництві серверних процесорів використовуються ті ж технології та обладнання що ,і для десктопних. Материнські плати серверного сегмента відрізняються формфактором, для тогощоб підходити під специфічні корпусу і наявністю можливості швидкої заміникомплектуючих.

На багатьох серверних материнських платах встановлені модулі віддаленогоуправління живленням, консолі і т.п.

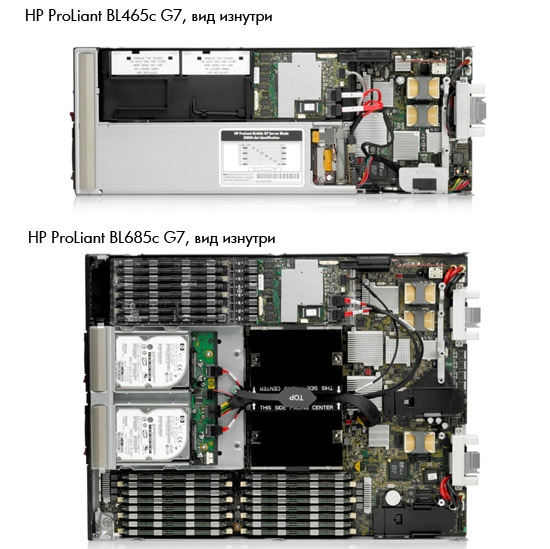

HP почала постачання двох моделей серверів-лез HP ProLiant на основіновітнього процесора AMD Opteron. Четирехсокетний повнорозмірний HP ProLiant BL685c G7 використовують восьми або дванадцяти ядерні Opteron 6100.

Модель обладнана 32 слотами для модулів пам'яті DDD3 і підтримує ОЗУ обсягом512 Гбайт.

Рис.3.1 - HP ProLiant BL685c G7

Комплектуються замінними в гарячому режимі двома 2,5-дюймовими дисками SAS / SATA або двома твердотільними дисками SSD і вбудованим RAID-контролером Smart Array P410 я з однігігабайтним кешем, для якого передбачено збереження даних в енергонезалежній флеш-пам'яті при відключенні живлення сервера.

Нововведення цих лез в порівнянні з їх попередниками шостого покоління - вбудована в системну плату сервера двопортова карта конверговані мереж HP NC551i FlexFabric 10 Gb Ethernet адаптер для конвергентних мереж, що забезпечує підтримку як 10-гігабітного Ethernet, так і протоколів для доступу до систем зберігання Fibre Channel через Ethernet (FCoE) і ISCSI.

В даний час у більшості ЦОДів для передачі трафіку систем зберігання використовується виділена мережа зберігання SAN, оскільки звичайна локальна гігабітна мережу Ethernet не володіє достатньою пропускною здатністю для таких великих обсягів трафіку, а протокол TCP / IP не забезпечує доставку трафіку без втрати частини пакетів. Зазвичай мережі SAN будуються на основі технологій Fibre Channel, хоча застосування 10-гігабітного Ethernet дозволяє забезпечити достатньо високу пропускну здатність і при використанні ISCSI.

Нещодавно отримав статус промислового стандарту протокол FCoE дає можливість передавати трафік Fibre Channel по мережі на основі технології 10 Gigabit Ethernet і в результаті використовувати одну й ту ж мережеву інфраструктуру для передачі пакетів TCP / IP і Fibre Channel, відмовившись від виділеної мережі зберігання даних.

Заміна мереж LAN і SAN на одну конверговані мережу на основі технології 10 Gigabit Ethernet, за якою йде як трафік обміну даними між клієнтськими комп'ютерами і серверами, так і між серверами і системами зберігання, дає відчутні переваги - значно скорочується число кабелів, спрощується обслуговування мережевої інфраструктури ЦОДа і більше не треба використовувати комутатори та кабелі Fibre Channel.

Застосування конвертованих мереж удвічі скорочує число мережних адаптерів машини - якщо раніше сервер обладнався адаптером Ethernet для підключення локальної мережі та адаптером Fibre Channel для SAN, то тепер потрібен лише один мережевий адаптер і в результаті скорочується вартість конфігурації сервера і його енергоспоживання.

NC551i забезпечує обробку трафіку TCP / IP та протоколу ISCSI, звільняючи обчислювальні потужності центральних процесорів сервера від виконання цих функцій, і підтримує технологію Virtual Connect Flex-10, що дозволяє розділити кожен 10-гігабітний порт на чотири мережевих каналу