- •Структуры, допускаемые стандартом камак.

- •2. Интерфейс вертикальной магистрали камак.

- •3. Интерфейс горизонтальной магистрали камак

- •4. Структура командного сообщения кольцевой магистрали камак.

- •5. Магистраль приборного интерфейса для интеллектуальных средств измерений, испытаний и контроля.

- •6. Признаки децентрализованных систем

- •7. Двухуровневые системы. Задачи, решаемые периферийными и центральной эвм.

- •8. Слабое взаимодействие процессоров в распределенных системах.

- •9. Сильное взаимодействие процессоров в распределенных системах.

- •10. Среднее взаимодействие процессоров в распределенных системах.

- •11.Типичная структура процессора в стандарте р-896.

- •Пример системы в стандарте р-896. Основные шины.

- •Основные циклы шины pci.

- •14.Организация и порядок работы шины pci.

- •15.Системные выводы. Линии адреса и команд шины pci.

- •16)Линии управления интерфейсом шины pci,их назначение

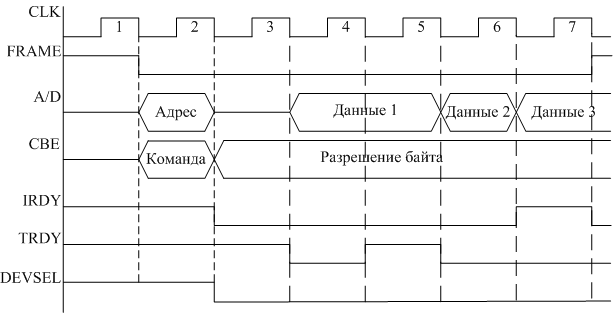

- •17) Временная диаграмма записей устройства ввода-вывода шины pci.

- •18)Временная диаграмма чтения записей устройства ввода-вывода шины pci.

- •19)Понятие системы технической диагностики .Кодирование состояний и проверок.

- •20)Правила перехода системы из одного состояния в другое при поиске неисправности.

17) Временная диаграмма записей устройства ввода-вывода шины pci.

18)Временная диаграмма чтения записей устройства ввода-вывода шины pci.

Все операции по передаче данных происходят по переднему фронту CLK. Цикл обмена начинается с установки сигнала FRAME=0. После этого начинается фаза адреса. На выходе A/D – адрес, на выходе CBE – команда. Адрес и команда могут быть зафиксированы по переднему фронту второго импульса. После фазы адреса на линиях CBE устанавливается сигнал разрешения передачи байта и сигнал готовности мастера IRDY. После этого устанавливается сигнал готовности приемника TRDY, а на шине A/D устанавливаются данные. Передний фронт третьего импульса – фаза ожидания, так как нет готовности адреса TRDY=1.

4-ый импульс – передний фронт – осуществляется обмен данными, т.к. оба сигнала готовности в нуле. Во время 5-го импульса обмена нет, TRDY=IRDY=0. Во время 7-го импульса – обмена нет, т.к. IRDY=1. В конце 7-о импульса снимается сигнал FRAME. Обмен данными переходит в стадию завершения. По переднему фронту 8-го импульса осуществляется последний обмен данными.TRDY =1. Во время 6-го импульса – вторая фаза данных, т.е сигнал готовность в нуле. IRDY = 1. В конце 7 импульса снимается сигнал FRAME и обмен переходов в стадию завершения. По переднему фронту 8 импульса происходит 3 фаза данных и обмен завершен.

19)Понятие системы технической диагностики .Кодирование состояний и проверок.

ИСИ и К является сложными системами, и часто выход из строя даже одного блока приводит к отказу всей системы. В связи с этим необходимо проводить периодический контроль работоспособности системы. Для этих целей исп-ют СТД.

Классификационный признак СТД:

СТД различают по полноте проводимой проверки ( всю систему проверяем или отдельные блоки или блоки и элементы блоков);

По целевому назначению (диагностические, прогнозирующие);

По виду входного сигнала (аналоговые, цифровые);

По степени автоматизации ( автоматические, полуавтоматические);

По конструктивному исполнению ( автономные (универсальные), встроенные).

Для реализации алгоритма, система делиться на блоки. Эти блоки нумеруются и системе ставится в соответствие двоичный код, число разрядов которого равно числу блоков. Алгоритм является полностью формализованным и поэтому легко реализуется на ЭВМ.

При составлении программы вводится понятие системы S и проверки системы пи. При составлении программы вводится ограничение, что неисправен только один блок. Состояние S кодируется следующим образом: 0 ставится в тех разрядах, которые составляют проверенным и исправным блокам. 1 – на месте неисправных или непроверенных боков.

Исходное состояние системы все единицы.

Проверки координируются так:

-0 – в тех разрядах, соответствующие которым блоки проверяются;

-1 – в остальных разрядах

Проверки Пи:

О ставится в тех разрядах соответствующие которым блоки проверяются 1 в остальных разрядах.

20)Правила перехода системы из одного состояния в другое при поиске неисправности.

В результате каждой очередной проверки система переходит из одного состояния в другое.

Код последующего состояния определяется по следующим правилам:

-При положительной проверке (проверяемые блоки работают правильно) код последующего состояния получают из операции поразрядного & над кодом текущего состояния и кодом проверки.

-При отрицательной проверке код нового состояния будет результат операции & над кодом текущего состояния и инверсного кода проверки.

Критерии оптимизации программы отыскания неисправностей:

1.критерий мини-макса

Если известно время проверки каждого блока, то можно составить полный перебор вариантов проверок для каждого блока. Для каждого варианта определяется максимальное время реализации среди максимальных выбирается минимальное.

2. критерий время-вероятность. Если известно, время проверки ti каждого блока и вероятность выхода из строя PI программа строится таким образом, чтобы следующий блок выбирался непроизвольно, а тот у которого ti/Pi минимум

3. метод половинного деления. Для линейно соединенных блоков. Первая проверка проверяется на выходе приблизительно половины блоков. Вторая производится при половинном делении блоков, в котором находится неисправный блок. Если известна вероятность отказов каждого блока то разбивка осуществляется так, чтобы суммарные вероятности выхода из строя блоков каждой части были приблизительно равны.