- •Понятия эвм и вс. Понятие архитектуры вс

- •Архитектура как набор взаимодействующих компонентов. Архитектура как интерфейс между уровнями физической системы

- •Теория эволюции компьютеров. Закон Мура. Дуализм в развитии техники Теория эволюции компьютеров

- •Дуализм в развитии техники

- •Механическая эра вычислений

- •Счетно-аналитические машины

- •Общее описание и анализ вычислительной машины eniac

- •Общее описание и анализ вычислительной машины edvac Анализ eniac

- •Принципы фон-Неймана. Поколения эвм

- •Многоуровневая компьютерная организация. Уровни для прикладных и системных программистов

- •Многоуровневая компьютерная организация

- •Архитектура системы команд

- •Cisc и risc архитектуры процессоров Архитектура системы команд

- •Cisc и risc архитектуры процессоров

- •Организация risc мп dec Alpha 21x64 Организация risc мп dec Alpha 21x64

- •Развитие архитектур современных мп. Расширение архитектуры x86 Развитие архитектур современных мп

- •Архитектура vliw

- •Архитектура epic

- •Технология ia-64

- •Предпосылки развития вс. Закон Гроша для вс

- •Модель вычислителя

- •Возможности совершенствования эвм

- •Модель коллектива вычислителей

- •Структура коллектива вычислителей

- •Алгоритм работы коллектива вычислителей

- •Принципы технической реализации модели коллектива вычислителей

- •Архитектурные свойства вс Архитектурные свойства вычислительных систем

- •Системы (языки) параллельного программирования Системы (языки) параллельного программирования

- •Параллельные модели программирования. Модель передачи сообщений. Реализация на основе mpi.

- •Параллельные модели программирования. Модель общей памяти. Реализация на основе OpenMp Системы (языки) параллельного программирования

- •1. По назначению (универсальные и специализированные)

- •2. По типу (многомашинные и многопроцессорные) (ниже)

- •3. По типу эвм или процессоров (однородные и неоднородные)

- •4. По степени территориальной разобщенности (сосредоточенные и распределенные)

- •6. По режиму работы вс (оперативные и неоперативные)

- •Многомашинные вс. Режимы работы. Отличия от многопроцессорных вс

- •Классификация Флинна архитектур

- •Основные классы вычислительных систем

- •Параллельные алгоритмы. Параллельная программа. Локальное и глобальное распараллеливание

- •Модель вычислений в виде графа "операции-операнды"

- •Показатели эффективности параллельных вычислений: ускорение, эффективность, масштабируемость

- •Оценка максимально достижимого параллелизма. Закон Амдала. Парадокс параллелизма

- •Многомашинные вс. Режимы работы. Отличия от многопроцессорных вс

- •Уровни комплексирования в вычислительных системах Многомашинные вс. Режимы работы. Отличия от многопроцессорных вс

- •Уровни комплексирования в вс

- •Алгоритмы маршрутизации. Методы передачи данных. Латентность и пропускная способность сети

- •Передача данных между двумя процессорами и широковещательная передача. Реализация точечных методов передачи и широковещательной рассылки в mpi

- •Сложные задачи. Масштабируемость параллельных вычислений. Функция изоэффективности

- •Системы с общей и распределенной памятью. Многоуровневая организация общей памяти

- •Память с чередованием адресов

- •Симметричные (smp) многопроцессорные вс. Архитектура типа uma, coma, numa

- •Мультипроцессор Sun Enterprise 10000

- •Мультипроцессоры numa

- •Векторные системы. Понятие вектора и размещение данных в памяти. Векторный процессор. Pvp-система

- •Структура векторного процессора Структуры типа "память-память" и "регистр-регистр". Ускорение вычислений в векторных системах

- •Вычислительная система star-100

- •Вычислительная система cray c-90

- •Матричные вычислительные системы. Обобщенная модель матричной вс. Интерфейсная вм. Контроллер массива процессоров

- •Вычислительная система illiac IV

- •Ассоциативная память. Ассоциативные вс Ассоциативная память

- •Систолические структуры Систолические структуры

- •Кластеры. Виды кластеров

- •Топологии кластеров. Кластер Beowulf

- •Топологии кластеров

- •Кластер Beowulf

- •Архитектура с массовой параллельной обработкой Системы с массовым параллелизмом (mpp-системы)

Архитектура системы команд

Cisc и risc архитектуры процессоров Архитектура системы команд

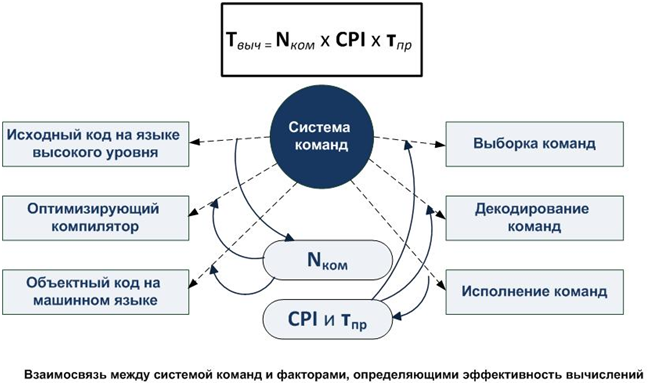

В упрощенной трактовке время выполнения программы (Tвыч) можно определить через число команд в программе (Nком) среднее количество тактов процессора, приходящихся на одну команду (CPI), и длительность тактового периода:

Твыч = NкомxCPIxτпр

Каждая из составляющих выражения зависит от одних аспектов архитектуры системы команд и, в свою очередь, влияет на другие, что свидетельствует о необходимости чрезвычайно ответственного подхода квыбору АСК.

Cisc и risc архитектуры процессоров

Уровень архитектуры команд включает набор машинных команд, которые выполняются микропрограммой-интерпретатором или аппаратным обеспечением.

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники, являются архитектуры CISC и RISC.

CISC

– Complete Instruction Set Computer (CISC-архитектура, компьютер на микропроцессоре с полным набором команд)

RISC

– Reduced Instruction Set Computer (RISC-архитектура, компьютер с сокращенным набором команд)

|

CISC |

RISC |

Основоположник, модель |

IBM, IBM/360 |

CDC6600 (Крэй) |

Лидер, сегодня |

x86 |

Alpha, PowerPC, SPARC |

Рынок |

Персональные ЭВМ (благодаря совместимости с программным обеспечением младших моделей, общая стоимость которого - в начале 90-х годов - составила несколько миллиардов долларов США) |

Высокопроизводительные компьютеры (стоимость ПО не настолько существенна) |

Реализация |

Микропрограммная (интерпретация) |

Аппаратная

|

Число регистров общего назначения |

небольшое |

большое

|

Формат команд |

большое количество форматов команд различной разрядности |

команды фиксированной длины и фиксированного формата |

Адресация |

большое количество методов адресации, преобладание двухадресного формата команд |

простые методы адресации, трехадресный формат команд |

Основоположник, модель

Организация первых моделей процессоров - i8086/8088 - была направлена, в частности, на сокращение объёма программ, критичного для систем того времени, отличавшихся малой оперативной памятью. Расширение спектра операций, реализуемых системой команд, позволило уменьшить размер программ, а также трудоёмкость их написания и отладки. Однако увеличение числа команд повысило трудоёмкость разработки их топологических и микропрограммных реализаций. Последнее проявилось в удлинении сроков разработки CISC-процессоров, а также в проявлении различных ошибок в их работе.

Эти недостатки обусловили необходимость разработки альтернативной архитектуры - RISC, нацеленной, прежде всего, на снижение нерегулярности потока команд уменьшением их общего количества.

Лидер, сегодня

Процессоры Intel, начиная с 486-го, содержат ядро RISC, которое выполняет самые простые (и обычно самые распространенные) команды за один цикл тракта данных, а по обычной технологии CISC интерпретируются более сложные команды. В результате обычные команды выполняются быстро, а более сложные и редкие — медленно. Хотя при таком «гибридном» подходе работа происходит не так быстро, как у RISC, данная архитектура имеет ряд преимуществ, поскольку позволяет использовать старое программное обеспечение без изменений.

Первая модель процессора Intel, которая вплотную приблизилась к архитектуре RISC – PentiumPRO (Precision RISC Organization - Полноценная RISC-архитектура).

Реализация

Устранение уровня интерпретации обеспечивает высокую скорость выполнения большинства команд. В компьютерах типа CISC более сложные команды могут разбиваться на несколько частей, которые затем выполняются как последовательность микрокоманд. Эта дополнительная операция снижает скорость работы машины, но она может быть применима для редко встречающихся команд.

Число регистров

Развитие архитектуры RISC в значительной степени определялось прогрессом в области создания оптимизирующих компиляторов. Именно современная техника компиляции позволяет эффективно использовать преимущества большего числа регистров, конвейерной организации и большей скорости выполнения команд.

Большое число регистров позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные.

Формат команд

Команды должны легко декодироваться. Предел количества вызываемых команд в секунду зависит от процесса декодирования отдельных команд. Декодирование команд осуществляется для того, чтобы определить, какие ресурсы им необходимы и какие действия нужно выполнить. Полезны любые средства, которые способствуют упрощению этого процесса. Например, используются регулярные команды с фиксированной длиной и с небольшим количеством полей. Чем меньше разных форматов команд, тем лучше.

Адресация

Простые методы адресации позволяют резко упростить декодирование команд. Организация регистровой структуры – основное достоинство и основная проблема RISC. Практически любая реализация RISC-архитектуры использует трехместные операции обработки, в которых результат и два операнда имеют самостоятельную адресацию – R1 := R2, R3. Это позволяет без существенных затрат времени выбрать операнды из адресуемых оперативных регистров и записать в регистр результат операции. Кроме того, трехместные операции дают компилятору большую гибкость по сравнению с типовыми двухместными операциями формата «регистр – память» архитектуры CISC. В сочетании с быстродействующей арифметикой RISC-операции типа «регистр – регистр» становятся очень мощным средством повышения производительности процессора.