- •Шифратори та дешифратори. За якими принципами вони будуються?

- •Які шифратори (дешифратори) називаються повними, а які – неповними?

- •Мультиплексори та демультиплексори.

- •4.Як забезпечується нарощування мультиплексорів?

- •5.Компаратор. Які функції можуть виконувати компаратори?

- •6.Що таке програмовані логічні матриці плм?

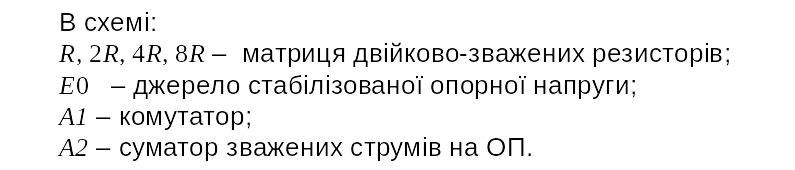

- •7.Цап на двійково-зважених резисторах.

- •8.Що таке дворівнева плм? Які функції виконує кожний її рівень?

- •9.Що таке перепрограмована логічна матриця пплм?

- •10.Як виконується програмування пплм?

- •11. Що таке озп? Які функції вони виконують?

- •12.Що таке пзп? Які функції вони виконують?

- •6.3. Запам’ятовувальні пристрої для зберігання постійної інформації (пзп)

- •Перевага матриці типу r – 2r у простоті її виготовлення, бо для неї досить тільки два номінали резисторів r і 2r.

4.Як забезпечується нарощування мультиплексорів?

5.Компаратор. Які функції можуть виконувати компаратори?

Цифрові компаратори – це пристрої, що призначені для порівняння двох чисел.

Розглянемо два цілих двійкових числа А і В. При їхньому порівнянні можуть статися три варіанти:

А = В; А >B і A < B.

Перший випадок (А=В) реалізується в найпростіших компараторах.

Такий компаратор виявляє лише факт рівності або нерівності двох поданих на його вхід чисел А і В і формує на виході сигнал рівності (логічну одиницю), або нерівності – логічний нуль.

Функцію, яку реалізує компаратор у цьому випадку можна визначити формулою:

Найпростіший компаратор рівності реалізується за допомогою логічних схем “Виняткове АБО” (елементи D1 і D2) та багатовхідного кон’юнктора D3.

У другому випадку компаратори можуть відрізняти не тільки рівність чисел А і В, але й нерівність, коли А >B або А < B. Такі компаратори будуються за більш складною схемою.

Вони

визначають стани нерівностей і описуються

системою нерівностей:

Вони

визначають стани нерівностей і описуються

системою нерівностей:

Нерівнісні компаратори мають два виходи: у1 та у2. Рівень логічної одиниці з’являється на виході у1 при A < B, а на виході у2 – при А > B. Промисловість випускає цифрові повні багато-розрядні компаратори, які мають і вихід рівності

А = В, і виходи нерівностей A < B та А > B.

6.Що таке програмовані логічні матриці плм?

Матрична схема або логічна матриця являє собою сітку ортогональних провідників, у перетинах яких можуть бути установлені напівпровідникові елементи: діоди або транзистори, що ввімкненні через легкоплавкі перемички до відповідних провідників матриці. Під час програмування ці перемички або перепалюють, або залишають в залежності від схеми, яку треба реалізувати за допомогою матриці.

З матричної структури шляхом її програмування одержують заданий комбінаційний пристрій. Тому такі структури називаються “комбінаційні програмовані логічні матриці” (ПЛМ).

ПЛМ, як правило, мають два схемотехнічних рівні: на одному з них утворюються потрібні кон’юнкції, а на другому – диз’юнкції. Іноді одна з матриць може бути фіксованою. Обидві матриці з’єднуються каскадно.

Існують і послідовнісні ПЛМ, які у своєму складі містять певне число вбудованих елементів пам’яті. Такі ПЛМ характеризуються розрядністю регістра пам’яті.

7.Цап на двійково-зважених резисторах.

5.2.2.1 Схема цифро-аналогових перетворювачів на двійково-зважених резисторах

Схеми (цифро-аналогових перетворювачів) ЦАП у мікросхемному виконанні є резистивними матрицями.

Номінали резисторів, які для них використовуються, визначаються з ряду

20R, 21R, 22R, …, 2n–1R ,

де n – число двійкових розрядів.

8.Що таке дворівнева плм? Які функції виконує кожний її рівень?

Матриця М1 має S входів і q виходів. Вона дозволяє реалізувати q елементарних кон’юнкцій Р1, ..., Рq змінних х1, ... хS, які надходять на її входи.

Матриця М2 має q входів і t виходів. Вона дозволяє реалізувати t елементарних диз’юнкцій у1, ..., уt змінних Р1, ..., Рq, які надходять на її входи з виходів матриці М1.

Виходи матриці М1 з’єднані з входами матриці М2 й утворюють проміжні шини 1– q ПЛМ. ПЛМ, що має S входів, t та q проміжних шин називається ПЛМ (S, t, q).

Різновидом ПЛМ (S, t, q) є їхня удосконалена модель: ПЛМ (Z, q). В ПЛМ (Z, q) фіксується лише два параметри: підсумоване число входів і виходів Z = S + t та число проміжних шин q. Параметри S і t можуть набувати будь-яких конкретних значень при програмуванні.