10 Практична робота № 8

Тема: Вивчення роботи лічильників.

Мета: Синтез 4-хрозрядного віднімаючого та складаючого лічильників на базі Т-тригерів та моделювання його функціонування в середовищі Electronics Workbench.

Теоретичні відомості:

Лічильником називається послідовний пристрій, призначений для рахунку вхідних імпульсів та фіксації їх числа в двійковому коді.

Основним статичним параметром лічильника є модуль рахунку М.

Для визначення структури двійкового лічильника можна розглянути послідовність двійкових чисел, обмежуючись, для спрощення, 3-х розрядним кодом (табл. 1)

Таблиця 1 – Таблиця істинності лічильника 3-х розрядних двійкових кодів

N |

С |

Q2 |

Q1 |

Q0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

2 |

1 |

0 |

1 |

0 |

3 |

1 |

0 |

1 |

1 |

4 |

1 |

1 |

0 |

0 |

5 |

1 |

1 |

0 |

1 |

6 |

1 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

Для реалізації лічильника з модулем рахунку М=8 необхідно, як мінімум, три тригери. З табл. 1 видно, що значення Q0, яке відповідає молодшому розряду, змінюється з надходженням кожного імпульсу синхронізації, Q1 – з надходженням кожного другого імпульсу синхронізації, а Q2 – з надходженням кожного четвертого імпульсу. Такий алгоритм можна легко реалізувати за допомогою асинхронних Т-тригерів, причому синхронізацію кожного наступного тригера здійснюють вихідні сигнали попереднього, а перемикання першого тригера, що формує значення Q0 – безпосередньо послідовність синхроімпульсів.

Т-тригер повинен змінювати свій стан на протилежний по кожному активному логічному сигналу, діючому на інформаційному вході Т.

Даному алгоритму роботи відповідає таблиця переходів, в якій активним вважається сигнал логічної 1 (табл.2).

Реалізація такого режиму роботи забезпечується введенням в D- тригер кола додаткового зворотного зв’язку. Отримана таким чином структура відповідає алгоритму роботи Т-тригера.

Таблиця 2 – Таблиця переходів Т-тригера

Qn |

Qn+1 |

T |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Для отримання сумуючого лічильника, який виконує мікрооперацію інкремента, послідовно підключені синхронні Т-тригери повинні мати інверсні динамічні входи. Якщо асинхронні тригери мають прямі динамічні входи, то лічильник перетворюється у віднімаючий та виконує мікрооперцію декремента.

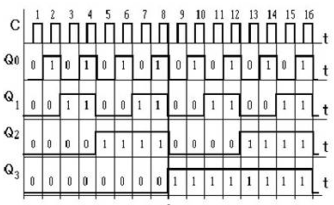

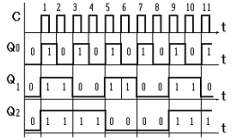

Часові діаграми складаючого та віднімаючого лічильників наведені на рисунку 1,2.

Рисунок 1 – Часова діаграма роботи асинхронного складаю чого лічильника.

Рисунок 2 – Часова діаграма роботи трьох розрядного віднімаючого лічильника на D-тригерах

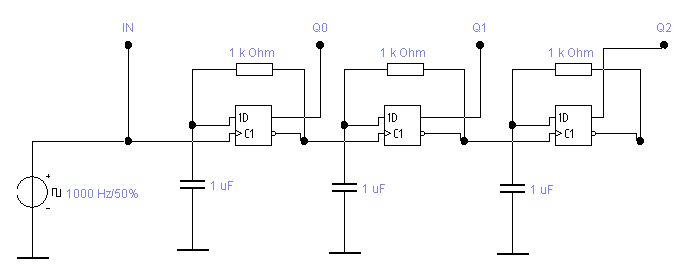

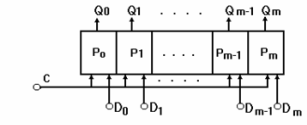

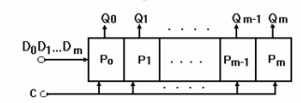

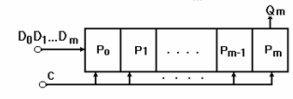

Схеми 3-хрозрядного віднімаючого та сумуючого лічильників, зображені на рисунку 3 та 4 відповідно.

Рисунок 3 – Схема віднімаючого лічильника.

Рисунок 4 – Схема сумуючого лічильника.

Хід роботи

1 В середовищі Electronics Workbench побудувати 3-хрозрядні складаючий та віднімаючий лічильники з модулем рахунку М=8, зображені на рисунках 3,4.

2 За допомогою логічного аналізатора отримати часові діаграми роботи лічильників.

3 Створити таблицю 4-хрозрядних двійкових кодів.

4 Виконати індивідуальне завдання згідно номеру варіанта.

5 Побудувати часову діаграму роботи отриманого лічильника.

6 Визначити модуль рахунку М побудованого лічильника.

Зміст звіту:

1. Тема та мета роботи.

2. Короткі теоретичні відомості.

3. Хід роботи.

4. Схема лічильника, побудованого за індивідуальним завданням та часова діаграма його роботи.

5. Відповіді на контрольні запитання.

Контрольні питання

1. Назвіть основні параметри та ознаки класифікації лічильників.

2. Яким чином здійснюється підвищення швидкодії лічильників?

3. Як відбувається перемикання в складаючому та віднімаючому лічильниках?

4. Чим обумовлюється напрямок рахунку послідовних лічильників?

Варіанти індивідуальних завдань:

Номер варіанту |

Завдання |

Непарний (1,3,5,…,27,29) |

Побудувати 4-розрядний сумуючий лічильник з частотою вхідних імпульсів Nв*100 |

Парний (2,4,6,8,…,28,30)

|

Побудувати 4-розрядний віднімаючий лічильник з частотою вхідних імпульсів Nв*100 |

11 ПРАКТИЧНА РОБОТА № 9

Тема: Вивчення роботи елементарної комірки ОЗП.

Мета: 1) отримання практичних навиків роботи в електронній лабораторії Electronics Workbench;

2) моделювання роботи елементарної запам’ятовуючої комірки ОЗП в середовищі Electronics Workbench;

3) дослідження режимів запису та зчитування з елемента пам’яті.

Теоретичні відомості:

Оперативні запам’ятовуючі пристрої поділяються на два класи: статичні та динамічні. В статичних ОЗП запам’ятовування інформації здійснюється за допомогою тригерів, а в динамічних – на конденсаторах. Тривалість зберігання інформації в статичних ОЗП не обмежена, тоді як в динамічних вона обмежується часом саморозрядки конденсатора.

Конструктивно будь – який ОЗП складається з двох блоків – матриці запам’ятовуючих елементів та дешифратора адреси. Кожна комірка пам’яті адресується за входами, шляхом вибору дешифраторами адресних ліній та подачею на обрані лінії логічної одиниці. При цьому у вибраній комірці спрацьовує двовхідний елемент І

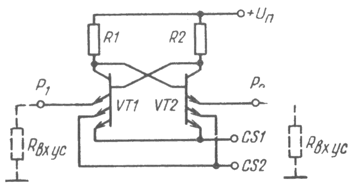

Статичні ОЗП на біполярних транзисторах. Статичні елементарні запам’ятовуючі комірки, що використовують біполярні транзистори, це досить дорогі пристрої, виконані на основі різноманітних тригерних елементів.

На сьогоднішній день даний клас схем має найбільшу швидкодію. Розглянемо більш детально схемотехнічне рішення ЕЗК на біполярних транзисторах.

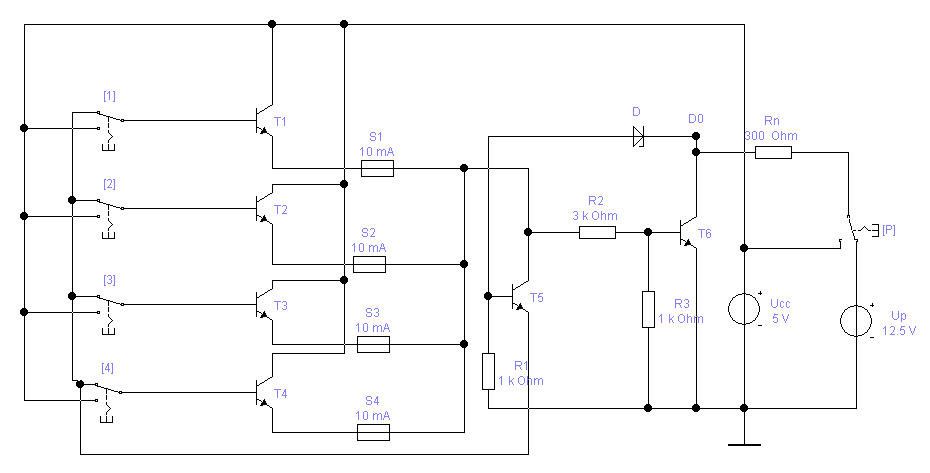

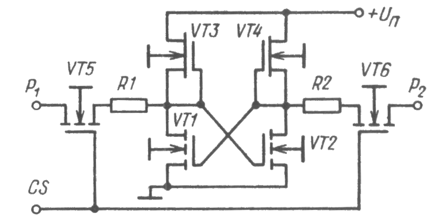

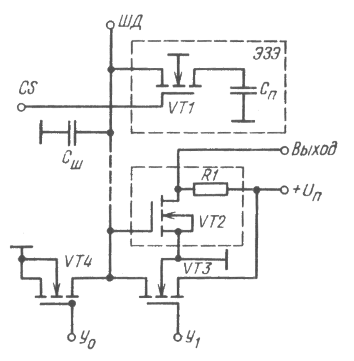

Рисунок 1 – Принципова електрична схема ЕЗК на біполярних транзисторах.

На рисунку 1 наведена принципова електрична схема ЕЗК на біполярних транзисторах. Даний елемент використовує технологію ТТЛ і призначений для застосування в ЗП з двовимірною адресацією. Його основу складають два інвертора, виконаних на трьохемітерних транзисторах VT1, VT2. Інвертори підключені послідовно та охоплені глибоким додатнім зворотнім зв’язком. Дві пари попарно об’єднаних емітерів транзисторів утворюють виводи вибірки елемента CS1 і CS2. Третя пара емітерів транзисторів утворює прямий Р1 та інверсний Р2 виходи елемента, які через вхідні опори підсилювача зчитування підключені до загальної шини.

В режимі зберігання на один або обидва виводи вибірки (CS1, CS2) ЕЗК подано напругу низького рівня, при цьому тригер, утворений інверторами, знаходиться в одному із стійких станів. Припустимо, що транзистор VT2 насичений, а VT1 зачинений. Весь струм насиченого транзистора VT1 замикається через один із виводів вибірки елемента на загальну шину. Тому в колі вихідного вивода Р1 струм відсутній і інформація з ЕЗК не надходить на вхід підсилювача зчитування (URвх.ус.= 0).

Для зчитування інформації на обидва входи вибірки елемента необхідно подати напругу високого рівня. При цьому єдиним шляхом протікання струму насичення транзистора залишається вихідний вивод Р1 ЕЗК. Цей струм утворює на вхідному опорі підсилювача зчитування напругу URвх.ус., полярність якої відповідає записаній в елемент інформації. Слід відмітити, що при зчитування з елемента інформації, вона губиться. При подачі на один або обидва входи вибірки напруги низького рівня тригер продовжує залишатися в тому ж стані.

При необхідності записати в елемент нову інформацію на нього також спочатку подаються сигнали вибірки. Після чого на зовнішніх шинах встановлюється полярність напруги, що відповідає новій інформації. Для випадку, що розглядається, на вхід Р1 подається напруга високого рівня, а на Р2 – низького рівня. При цьому так як всі кола протікання емітерного струму транзистора VT1 є розірваними, на його колекторі формується напруга високого рівня. Ця напруга насичує транзистор VT2, який формуючи на своєму колекторі напругу низького рівня, підтверджує зачинений стан транзистора VT1. В ЕЗК записується нова інформація. Після знімання з елемента сигналів вибірки нова інформація буде зберігатися в тригері до моменту наступного запису.

Якщо з багатоемітерних транзисторів елемента виключити по одному емітеру, то отримаємо елемент для ЗП з одномірною адресацією.

Хід роботи

1. В середовищі Electronics Workbench побудувати схему елементарної комірки пам’яті ОЗП (рис. 2)

Рисунок 2 – Схема елементарної запам’ятовуючої комірки ОЗП в середовищі Electronics Workbench

2. За допомогою ключів [1], [2], [3], [4] на відповідних входах встановити логічні сигнали, необхідні для роботи комірки.

При запису в комірку на вході (розрядній шині) D_in встановлюється логічний 0 або 1. Якщо на вході WR\RD встановлено логічну одиницю, то комірка пам’яті знаходиться в режимі запису, якщо логічний 0 – в режимі зчитування. На входах Adr_X та Adr_Y повинні бути встановлені логічні одиниці.

3. Дослідити режими запису та зчитування:

- Записати в комірку пам’яті логічну одиницю та зчитати її;

- Потім записати логічний нуль та зчитати його.

- При зчитуванні одиниці на виході D_out буде загоратися червоне світло індикатора

4. Записати свій номер варіанту в чотирьохрозрядному двійковому коді занести цей код в комірку пам’яті.

Зміст звіту:

1. Тема та мета роботи.

2. Короткі теоретичні відомості.

3. Хід роботи.

4. Схема елементарної запам’ятовуючої комірки.

5. Відповіді на контрольні запитання.

Варіанти індивідуальних завдань:

Записати свій номер варіанту в чотирьохрозрядному двійковому коді занести цей код в комірку пам’яті.

Контрольні питання

1. Класифікація ЗП.

2. Основні параметри ЗП.

3. Описати режими роботи ОЗП на біполярних транзисторах.

4. Пояснити різницю між динамічними та статичними ОЗП. Переваги та недоліки таких ОЗП.

12 ПРАКТИЧНА РОБОТА № 10

Тема: Вмвчення роботи елементарної комірки ПЗП.

Мета:

1) отримання практичних навиків роботи в електронній лабораторії Electronics Workbench;

2) моделювання роботи елементарної запам’ятовуючої комірки ПЗП в середовищі Electronics Workbench;

3) дослідження режимів зберігання та запису з елемента пам’яті.

Теоретичні відомості:

Процес програмування ПЗП розглянемо на прикладі програмованого ПЗП, схема якого, в загальному випадку, складається з дешифратора адреси n × 2n (n – кількість розрядів) з додатковими входами дозволу та підключених до його входів n 2n- вхідних схем АБО з плавкими перетинками.

Оскільки елементи АБО однакові для всіх розрядів, то достатньо розглянути комірку пам’яті для одного розряду.

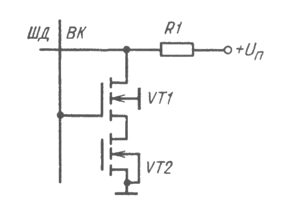

Схема такої комірки зображена на рисунку 1, де дешифратор імітується ключами 1 – 4, схема АБО – емітерними повторювачами на транзисторах Т1 – Т4, а плавкі перетинки – запобіжниками S1 – S4.

Опитування стану перетинок в робочому стані та керування їх проживанням здійснюється формувачем на транзисторах Т5, Т6 та стабілітроні D. Транзистор Т5 та стабілітрон D використовуються лише в режимі програмування та не впливають на роботу вихідного каскаду на транзисторі Т6, оскільки транзистор Т5 закритий низьким потенціалом на його базі.

В робочому режимі комірка ПЗП працює наступним чином. В початковому стані транзистори Т1 – Т4 та Т6 зачинені, а при підключеному до Т6 навантаженні на його виході D0 формується сигнал логічної одиниці (≈ + 5В).

При подачі на входи дешифратора заданої кодової комбінації та дозволяю чого сигналу на базу одного з транзисторів Т1 – Т4 буде подано сигнал близько +5В. якщо в якості такого транзистора, наприклад, опиниться транзистор Т4, то сигнал логічної одиниці з його емітера через перетинку S4 надійде до подільника на резисторах R2, R3, транзистор Т6 відчиниться, на його виході сформується сигнал логічного нуля.

В режимі програмування ключем Р до формувача підключається джерело Up напругою + 12,5В, в результаті чого пробивається стабілітрон D і відчиняється транзистор Т5. Якщо, наприклад, дешифратором вибраний ключ 1 (переводиться в нижній стан), то струм, що надходить с транзистора Т1, протікатиме через перетинку S1 і відчинений Т5, в результаті чого перетинка буде зруйнована.

Після цієї операції джерело живлення 12В відключається (ключ Р переводиться в початковий стан) і здійснюється перевірка програмованої комірки. При від’ємному результаті здійснюється повторне програмування при більшій тривалості дозволяю чого сигналу на вході дешифратора, що визначає час замкненого на +5В одного з ключем 1 – 4, вибраного у відповідності з адресою комірки. Керування часом спрацьовування цих ключів здійснюється автоматично програма тором за заданим алгоритмом. Такий процес здійснюється індивідуально для кожної комірки.

Рисунок 1 – Схема комірки пам’яті чотирьох розрядного ПЗП.

Хід роботи

1. В середовищі Electronics Workbench побудувати схему елементарної комірки пам’яті ПЗП (рис. 10.1.)

2. За допомогою ключів [1], [2], [3], [4] на відповідних входах встановити логічні сигнали, необхідні для роботи комірки.

3. Записати свій номер варіанту в чотирьохрозрядному двійковому коді занести цей код в комірку пам’яті.

4. Дослідити процес записування інформації в комірку пам’яті ПЗП

Зміст звіту:

1. Тема та мета роботи.

2. Короткі теоретичні відомості.

3. Хід роботи.

4. Схема елементарної запам’ятовуючої комірки.

5. Відповіді на контрольні запитання.

Варіанти індивідуальних завдань:

Записати свій номер варіанту в чотирьохрозрядному двійковому коді занести цей код в комірку пам’яті.

Контрольні питання:

Типи ПЗП.

Основні параметри ПЗП.

Яким чином програмуються програмовані ПЗП?

Яка технологія виготовлення масочних ПЗП?

13 ПРАКТИЧНА РОБОТА № 11

Тема: Дослідження роботи перетворювачів сигналів

Мета: 1) отримання практичних навиків роботи в електронній лабораторії Electronics Workbench;

2) моделювання роботи анолого цифрового перетворювача в середовищі Electronics Workbench;

3) дослідження перетворення аналогового сигналу у цифровий.

4) моделювання роботи цифро-анологового перетворювача в середовищі Electronics Workbench;

5) дослідження перетворення цифрового сигналу в аналоговий.

Теоретичні відомості:

Аналого-цифрові перетворювачі (АЦП) призначені для перетворення аналогових (безперервних) сигналів у цифрову форму. Перетворення аналогового сигналу відбувається в певні моменти часу, які називаються точками відліку. Кількість відділів за одиницю часу визначає частоту дискретизації (перетворення), що, в свою чергу, визначається швидкодією та умовами використання АЦП. Інтервал часу між відліком Тотс і частотою дискретизації fпр пов'язані співвідношенням:

Тотс = 1/fпр. (1)

У вимірювальній техніці для перетворення повільно мінливих процесів частота перетворення може бути встановлена невеликою - одиниці Герців і менше. У пристроях, де потрібно перетворювати сигнали в масштабі реального часу, частота перетворення вибирається з умови досягнення максимальної точності відновлення цифрового сигналу в аналогову форму.

Наприклад, перетворення мовного сигналу в дискретну форму. При цьому частота дискретизації визначається як fпр = 2Fмах, де Fмах - максимальна частота мовного сигналу.

Для забезпечення перетворення без перешкод потрібне виконання умови:

tпр < Тотс, (2)

де tпр - час перетворення АЦП одного відліку.

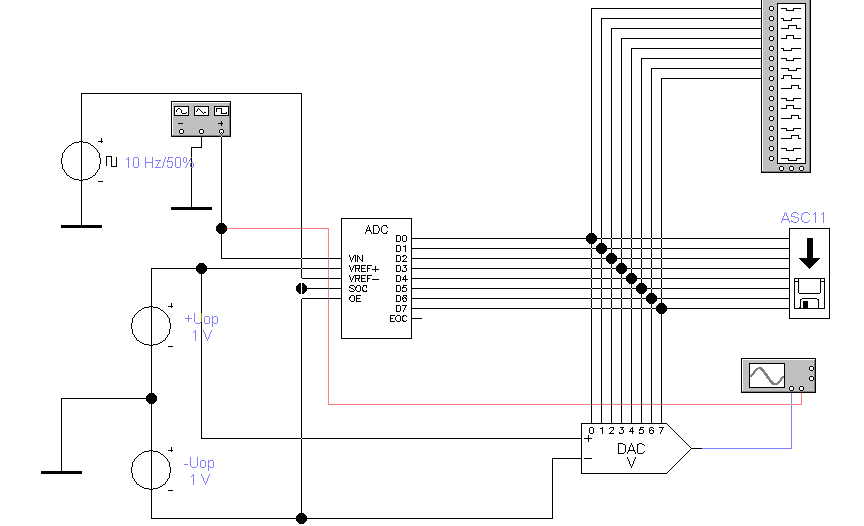

Бібліотека програми EWB містить 8-розрядний АЦП, схема включення якого наведена на рисунку 1

Вона містить генератор однополярних прямокутних імпульсів для синхронізації та керування виходом АЦП, функціональний генератор в якості джерела вхідного сигналу Ui, логічний аналізатор, перетворювач у двійковий код ASC 1, осцилограф та джерела опорної напруги.

Призначення виводів АЦП:

VIN – підключення джерела аналогового сигналу;

VREF+, VREF- - підключення джерел опорної напруги;

SOC – вхід синхронізації;

OE – дозвіл на видачу двійкової комбінації на виходах D0-D7;

EOC – сигнал готовності даних.

Рисунок 1 – Схема включення бібліотечного АЦП.

Цифро-аналоговий перетворювач – це пристрій, призначений для перетворення вхідної величини, представленою послідовністю цифрових кодів, в еквівалентні їм значення заданої фізичної величини.

Суть операції цифро-аналогового перетворення полягає у формуванні аналогових сигналів, що відповідають кодовим словам дискретного сигналу. Звичайно це формування технічно здійснюється за допомогою спеціального пристрою, який називається цифро-аналоговим перетворювачем (ЦАП).

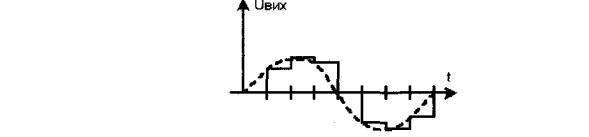

Часова діаграма класичного процесу цифро-аналогового перетворення має вигляд, наведений на рис.2.

Рисунок 2 – Часова діаграма класичного процесу цифро-аналогового перетворення

Рисунок 3 – Схема включення бібліотечного ЦАП.

Хід роботи:

1. В середовищі Electronics Workbench побудувати схему підключення АЦП (рис. 1.).

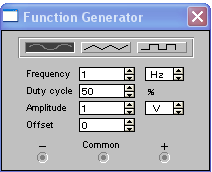

2. Встановити наступні параметри вимірюючих пристроїв:

![]()

![]()

3. Дослідити перетворення аналогового сигналу в цифровий за допомогою логічного аналізатора та осцилографа.

4. Синтезувати в середовищі Electronics Workbench схему для дослідження роботи цифро-аналогового перетворювача (рис. 3).

5. Дослідити процес цифро аналогового перетворення.

6. За допомогою логічного аналізатора визначити вхідний сигнал цифро-аналогового перетворювача.

7. За допомогою осцилографа визначити період перетворення

Зміст звіту:

1. Тема та мета роботи.

2. Короткі теоретичні відомості.

3. Хід роботи.

4. Схема підключення бібліотечного АЦП.

5. Схема підключення бібліотечного ЦАП.

6. Зовнішній вигляд вхідного та вихідного сигналів схеми.

7. Відповіді на контрольні запитання.

Варіанти індивідуальних завдань:

* Амплітуда та частота вхідних сигналів відповідає номеру варіанта.

Контрольні питання:

1. Призначення АЦП

2. Класифікація АЦП.

3. Принци аналого-цифрового перетворення

4. Призначення ЦАП

5. Класифікація ЦАП.

6. Принци цифро-аналогового перетворення

14 ТЕСТОВІ ЗАВДАННЯ ДЛЯ САМОПЕРЕВІРКИ ЗНАНЬ СТУДЕНТІВ ПРИ ПІДГОТОВЦІ ДО ПОПЕРЕДНЬОГО КОНТВОЛЮ З ПРАКТИЧНИХ РОБІТ.

14.1 Тестові завдання до практичної роботи за темою: «Переклад чисел з однієї системи числення в іншу»

1. Під системою числення розуміють спосіб подання будь-якого числа за допомогою:

а) алфавіту символів, названих цифрами;

б) цифр, названих алфавітом;

в) алфавіту кодів;

г) алфавіту букв.

2. Система числення в якій значення конкретної цифри постійне і не залежить від її розташування в запису числа називається:

а) непозиційною; б) позиційною; в) логарифмічною; г) кодованою.

3. Система числення в якій сама цифра має різне значення, обумовлене позицією цифри в послідовності, що зображає число:

а) позиційною; б) непозиційною; в) кодовою; г) алфавітною.

4. Кількість різних цифр в алфавіті позиційної системи називають:

а) основою системи; б) основою алфавіту;

в) системою; г) розрядом.

5. Система в якій кількість цифр дорівнює десяти називається:

а) десятковою; б) вісімковою; в) двійковою; г) кодованою.

6. Будь-яке число в позиційній системі можна виразити сумою:

а) добутків коефіцієнтів на степені основи; б) діяльників добутків;

в) коефіцієнтів діяльників; г) степенів основи.

7. Позиції цифр в числах називають:

а) розрядами; б) кодами; в) ступенями; г) коефіцієнтами.

8. В комп’ютерах застосовуються системичислення:

а) десяткова і двійкова; б) шістнадцяткова та десяткова

в) ніяка з перелічених; г) всі перелічені в пунктах «а» і «б».

9. Мінімальна основна система числення має основу:

а) два; б) три; в) один; г) нуль.

10. Число сім в двійковій системі числення записується як:

а) 111; б) Д 7; в) 101; г) А 5.

11.Число 215 в десятковій системі в шістнадцятирічній можна записати як:

а) Д 7; б) 11111111; в) А 5; г) А В Б Г.

12. Число 11101 можна перекласти в десяткову систему як:

а) 29; б) 129; в) 354; г) 11101.

14.2 Тестові завдання до практичної роботи за темою: «Виконання арифметичних операцій над числами в різних системах числення»

1. Будь-яка інформація подається в комп’ютер у вигляді:

а) двійкових кодів; б) десяткових чисел

в) восьмирічних чисел; г) в іншій системі.

2. Окремі елементи двійкового коду, що називають, називають:

а) розрядами (бітами); б) кодами; в) числами; г) системою числення.

3. Мінімальною одиницею інформації в комп’ютері є:

а) біт; б) байт; в) число; г) код.

4. Байт складається з:

а) восьми двійкових розрядів; б) двох десяткових розрядів;

в) машинних кодів; г) немає правильної відповіді.

5. Один кілобайт складає:

а) 210 байти; б) 220 байти; в) 230 байти; г) 10 біт.

6. Групи байтів утворюють:

а) двійкові слова; б) десяткові слова;

в) десяткові коди; г) систему числення.

7. Формати даних можуть бути:

а) фіксованою довжиною; б) змінною довжиною;

в) як з фіксованою так і зі змінною довжиною; г) комбіновані.

8. В прямому коді найпростіше виконується операція:

а) додавання; б) віднімання; в) множення; г) ділення.

9. В оберненому та додатковому кодах найпростіше виконується операція:

а) додавання; б) віднімання; в) ділення; г) множення.

10. Результатом складання двійкових чисел 10101 та 1111 є число:

а) 100100; б) 1111; в) 10; г) 25.

11.Результатом складання шістнадцятковій системі чисел 1 А та С Д є число:

а) Е 7; б) Д 2; в) 1111 г) 125.

12. Результатом складання у вісімковій системі чисел 375 та 721 є:

а) 1316; б) 1010; в) Е 7; г) А 2.

14.3 Тестові завдання до практичної роботи за темою: «Мінімізація логічних функцій та їх синтез»

1. Метою мінімізації є:

а) Заміна операції складання операцією віднімання;

б) Заміна операції складання множенням;

в) Зменшення вартості технічної реалізації заданої функції;

г) Заміна аналогових елементів цифровими;

2. Сумісними називаються мінтерми:

а) Повністю протилежні; б) Однакові;

в) Які відрізняються лише однією змінною; г) Будь-які два мін терми;

3. Карта Карно для 2-х змінних має:

а) 2 комірки; б) 4 комірки; в) 8 комірок; г) 16 комірок;

4. Які з наведених мінтермів є сумісними:

а)

![]() і

і

![]() ;

б)

і

;

;

б)

і

;

в)

![]() і

і

![]() ;

г)

;

г)

![]() і

і

![]() ;

;

5.

Вираз

![]() відповідає:

відповідає:

а) Закону комутативності; б) Закону асоціативності;

в) Закону дистрибутивності; г) Закону дуальності;

6.Згідно

з законом поглинання вираз

![]() дорівнює:

дорівнює:

а)

![]() ;

б)

;

б)

![]() ;

в)

;

в)

![]() ;

г)

;

г)

![]() ;

;

7. Який з виразів не є аксіомою алгебри логіки:

а)

![]() ;

б)

;

б)

![]() ;

в)

;

в)

![]() ;

г)

;

г)

![]() ;

;

8. Мінтермом називається:

а) називається логічна сума елементарних логічних добутків, в кожен з яки аргумент або його інверсія входять один раз;

б) кон’юнкція всіх змінних, при чому змінна входить в мін терм у прямому вигляді, якщо її значення в наборі дорівнює 1, і в інверсному вигляді, якщо 0;

в) диз’юнкція всіх змінних з набору, при чому змінні входять в набір в інверсному вигляді, якщо вони дорівнюють 1, та в прямому вигляді, якщо дорівнюють 0;

г) логічний добуток елементарних логічних сум, в кожну із яких аргумент або його;

9. Макстермом називають:

а) називається логічна сума елементарних логічних добутків, в кожен з яки аргумент або його інверсія входять один раз;

б) кон’юнкція всіх змінних, при чому змінна входить в мін терм у прямому вигляді, якщо її значення в наборі дорівнює 1, і в інверсному вигляді, якщо 0;

в) диз’юнкція всіх змінних з набору, при чому змінні входять в набір в інверсному вигляді, якщо вони дорівнюють 1, та в прямому вигляді, якщо дорівнюють 0;

г) ;логічний добуток елементарних логічних сум, в кожну із яких аргумент або його інверсія входять один раз.

10.-Функція

![]() отримана

за допомогою карти Карно

отримана

за допомогою карти Карно

00 01 11 10

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

00

а)

01

11

10

00 01 11 10

1 |

1 |

|

|

|

1 |

|

|

|

1 |

|

|

1 |

1 |

1 |

1 |

00

б)

11

10

00 01 11 10

1 |

|

|

1 |

1 |

|

|

1 |

1 |

|

|

1 |

1 |

|

|

1 |

00

в)

11

10

00 01 11 10

|

|

|

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

00

г)

01

11

10

11. Мінімізувати функцію можна :

а) Лише за допомогою аксіом алгебри логіки;

б) Лише за допомогою законів алгебри логіки;

в) Лише за допомогою карт Карно;

г) Будь-яким з перелічених способів;

12. Карта Карно для функції чотирьох змінних має вигляд:

а)

![]() ; б)

; б)

![]() ;

;

в)

![]() г)

г)

![]()

14.4 Тестові завдання до практичної роботи за темою: «Дослідження роботи комбінаційних пристроїв»

1. Шифратори, мультиплексори, демультиплексори призначені для:

а) перетворення кодів; б) перекладання з англійської на французьку

в) зсуву сигналів; г) зберігання інформації.

2. Шифратор – пристрій, який використовується для перетворення:

а) вихідного кода на пристрій індикації;

б) вхідного кода на пристрій індикації;

в) переклад послідовних кодів в паралельні;

г) переклад паралельних кодів в послідовні.

3. Дешифратор – пристрій, який використовується для:

а) перетворення вихідного кода на пристрій індикації;

б) перекладу з української мови на російську;

в) зсуву сигналів;

г) зберігання інформації.

4. Мультиплексор – пристрій, який:

а) підсилює сигнал.

б) перетворює послідовні коди в паралельні;

в) зберігає інформацію;

г) перетворює паралельні коди в послідовні;

5. Демультиплексор – пристрій, який:

а) генерує сигнал;

б) трансформує сигнал;

в) перетворює послідовні коди в паралельні;

г) використовується виключно як пристрій індикації.

6. Які двійкові числа еквівалентні наступним десятковим відповідно?

а) 111, 0101, 0001, 11111. б) 010, 1111, 10101, 10111111;

в) 011, 1011, 11111, 1000000; г) 100, 1001, 1000, 10000;

7. Десяткові еквиваленти для чисел 0010, 1111, 0011, 1001 відповідно є:

а) 2, 15, 3, 9; б) 5,12, 7, 13; в) 1, 5, 12, 7; г) 121, 125, 2115, 30.

8. Який логічний сигнал буде на виходах шифратора, якщо подати сигнал високого рівню:

В хід№5

хід№5

а) 100; б) 101; в) 111; г) 110.

9. На яких виходах дешифратора буде сигнал високого рівня, якщо сигнал на вході буде відповідно:

а) на 7; б) на 5; в) на 3; г) на 2.

10. Таблиця, яка ставить відповідність кодам, які подаються на вхід, кодам, що знімаються з виходу називається:

а) таблиця істинності; б) таблиця кодів;

в) таблиця часових діаграм г) таблиця хибності.

11. Шифратор по іншому можна назвати:

а) акодом б) декодером; в) кодером; г) катодом.

12. Дешифратор по іншому можна назвати:

а) суматором. б) кодером; в) випрямнечем г) декодером;

14.5 Тестові завдання до практичної роботи за темою:«Синтез комбінаційних схем»

1. Базовий логічний пристрій складання називається:

а) суматором; б) напівсуматором; в) віднімачем; г) напівіднімачем.

2. Суматори являють собою комбіновані логічні схеми, які складаються з елементів:

а) диференційних. б) аналогових; в) інтегральних; г) логічних (цифрових);

3. Два напівсуматора в сполученні з логічним елементом або складають:

а) віднімач; б) повний суматор; в) процесор; г) АЦП.

4. Сума чисел 101+011, 110+101, 111+111 в двійновій системі відповідно дорівнює:

а) 1000, 1011, 1110; б) 1010, 1001, 1000;

в) 1100, 1010, 1010; г) 1110, 1100, 1011.

5. Вказати логічну схему напівсуматора:

а )

)

в)

г)

г)

6. Вказати графічне позначення повного суматора:

а ) б)

в) г)

7. Кількість входів однороз. суматора дорівнює:

а) 1; б) 2; в) 3; г) 10.

8. Якщо розрядність результату складання більша за розрядність складників, тоді старший розряд:

а) переноситься;

б) включається;

в) додається до шостого розряду;

г) розрядність суми не може перевищувати розрядність складників.

9. Кількість входів напівсуматора дорівнює:

а) 1; б) 2; в) 3; г) 4.

10. Напівсуматор призначений для складання:

а) двох чотирьохрозрядних чисел; б) двох однорозрядних чисел;

в) двох двурозрядних чисел; г) трьох десяткових чисел.

11. Кількість розрядів повного суматора визначається:

а) кількістю базових елементів; б) кількістю входів до базових елементів;

в) коефіцієнтом підсилення; г) кількістю виходів з одного базового елемента.

12. Суматор має виходи, на яких формуються:

а) результат складання та перенесення. б) лише результат перенесення;

в) відсутні будь-які сигнали; г) лише результат складання;

14.6 Тестові завдання до практичної роботи за темою: «Вивчення роботи тригерів»

1.Тригер це:

а) Пристрій, здатний переводити двійковий код в десятковий;

б) Пристрій, здатний виконувати арифметичні операції над двійковими числами;

в) Пристрій, здатний перетворювати паралельний сигнал у послідовний;

г) Пристрій, здатний формувати два стійких стани та зберігати інформацію.

2.Тригери призначені для:

а) Зберігання інформації;

б) Перекладання десяткових чисел у двійкові;

в) Складання двійкових кодів;

г) Перетворення послідовного коду в паралельний;

3.Вихідною структурною коміркою послідовнісних логічних схем є:

а) Діод; б) Транзистор; в) Резистор; г) Тригер.

4.За реалізацією тригери класифікуються на:

а) DT, RS, A, XC; б) RS, D, T, JK; в) RS, JK, A, B. г) D; JK; A; C;

5.Кількість входів тригера залежить від:

а) Кількості виходів; б) Розрядності двійкового коду;

в) Типу тригера; г) Не від чого не залежить і може бути довільною;

6.Тригер здатний змінювати свій стан

а) Плавно; б) Стрибкоподібно;

в) Як плавно, так і стрибкоподібно; г) Взагалі не змінює свій стан;

7.Тригером зі статичним керуванням називається тригер, що перемикається:

а) В момент часу, коли синхросигнал перетинає певний пороговий рівень;

б) При надходженні фронту чи спаду синхросигналу;

в) В будь-який момент часу;

г) Взагалі не перемикається;

8.Зміна стану синхронного тригеру відбувається:

а) При зміні вхідних сигналів; б) Тільки при надходженні синхросигналу;

в) В будь-який момент часу; г) Взагалі не відбувається;

9.Тригером з динамічним керуванням називається тригер, що перемикається:

а) В момент часу, коли синхросигнал перетинає певний пороговий рівень;

б) При надходженні фронту чи спаду синхросигналу;

в) В будь-який момент часу;

г) Зберігає свій стан незмінним;

10.Зміна стану асинхронного тригеру відбувається:

а) При зміні вхідних сигналів; б) Тільки при надходженні синхросигналу;

в) В будь-який момент часу; г) Взагалі не відбувається;

11.Забороненою комбінацією для RS-тригера є:

а) Подача на обидва входи логічного «0»;

б) Подача на вхід R лог. «1», а на S – лог. «0»;

в) Подача на вхід S лог. «1», а на R – лог. «0»;

г) Подача на обидва входи логічної «1»;

12.Режиму збереження RS- та JK-тригерів відповідає:

а) Подача на обидва входи логічного «0»;

б) Подача на вхід R лог. «1», а на S – лог. «0»;

в) Подача на вхід S лог. «1», а на R – лог. «0»;

г) Подача на обидва входи логічної «1»;

14.7 Тестові завдання до практичної роботи за темою:«Дослідження роботи регістрів»

1.Регістром називається:

а) Пристрій, призначений для складання двійкових кодів;

б) Пристрій, призначений для рахунку вхідних імпульсів;

в) Пристрій, призначений для перекладу двйкового коду в десятковий;

г) Пристрій, призначений для запису, зберігання та зсуву інформації, представленої двійковим кодом.

2.Базовим елементом регістру є:

а) Транзистор; б) Тригер;

в) Діод; г) Резистор;

3.Яку з перелічених мікрооперацій виконує регістр:

а) Запис вхідної інформації в паралельній формі;

б) Збільшення вхідного двійкового коду на одиницю;

в) Зменшення двійкового коду на одиницю;

г) Складання двох двійкових кодів;

4.Регістр зсуву може зсувати інформацію

а) Як вправо, так і вліво б) Лише вправо;

в) Ліше вліво; г) Немає правильної відповіді

5.Регістри не можуть

а) записувати та видавати інформацію в паралельній формі;

б) записувати та видавати інформацію в послідовній формі;

в) Записувати та видавати інформацію одночасно в паралельній і послідовній формах;

г) Зсувати інформацію;

6.Парафазними називаються регістри, в яких

а) Інформація записується і зчитується в прямому та зворотному кодах;

б) Інформаці записується і зчитується або в прямому, або в зворотному коді;

в) Інформація записується в прямому коді, а зчитується в зворотному;

г) Інформація лише записується;

7.Однотактними називаються регістри, що

а) Управляються декількома послідовностями керуючих імпульсів;

б) Управляються однією послідовністю керуючих імпульсів;

в) Взагалі не управляються послідовностями імпульсів;

г) Немає правильної відповіді.

8.Функціональна схема паралельного регістра має вигляд:

а)

;

б)

;

б)

;

;

в)

г)

г)

;

;

9.Функціональна схема послідовного регістра має вигляд:

а) ; б) ;

в) ; г)

10.Функціональна схема регістра з послідовним прийомом і паралельною видачею має вигляд:

а) ; б) ;

в) ; г)

11.Регістром пам’яті називають:

а) Послідовний регістр; б) Паралельний регістр;

в) Комбінований регістр; г) Не має правильної відповіді.

12.На функціональний схемі паралельного регістра інформаційними входами є:

а) D0, D1,…,Dm-1,Dm; б) Q0,Q1,…,Qm-1,Qm; в) C; г) немає правильної відповіді.

14.7 Тестові завдання до практичної роботи за темою: «Вивчення роботи лічильників»

1.Лічильник призначений:

а) Для рахунку вхідних імпульсів та фіксації їх числа в двійковому коді;

б) Переводу послідовних сигналів в паралельні;

в) Синхронізації сигналів;

г) Немає правильної відповіді.

2.Базовим елементом лічильника є:

а) Інвертор; б) Компаратор; в) Тригер; г) Немає правильної відповіді.

3.Лічильники можуть рахувати

а) В прямому та зворотному напрямках; б) Виключно в прямому напрямку;

в) Виключно в зворотному напрямку г) Немає правильної відповіді.

4.Лічильник, в якому запуск всіх тригерів здійснюється одночасно називають

а) Асинхронним; б) Синхронним;

в) Комбінованим; г) Немає правильної відповіді.

5.Лічильники, в яких перемикання всіх тригерів здійснюється послідовно один за іншим, називаються лічильниками:

а) З паралельним перенесенням; б) З послідовним перенесенням;

в) З комбінованим перенесенням. г) Немає правильної відповіді.

6.Лічильники, в яких перемикання всіх тригерів здійснюється одночасно за сигналом синхронізації, називаються лічильниками :

а) З паралельним перенесенням; б) З послідовним перенесенням;

в) З комбінованим перенесенням. г) Немає правильної відповіді.

7.Лічильники, в яких використовуються різноманітні комбінації способів перенесення називаються лічильниками :

а) З паралельним перенесенням; б) З послідовним перенесенням;

в) З послідовно-паралельним перенесенням. г) Немає правильної відповіді.

8.Яку з перелічених операцій може виконувати лічильник:

а) Складання двох чотирьохрозрядних двійкових кодів;

б) Збільшення кодового слова на одиницю;

в) Інвертування вхідного коду.

г) Немає правильної відповіді.

9. Лічильники з паралельним перенесенням це:

а) Лічильники, в яких перемикання тригерів здійснюється один за іншим;

б) Лічильники в яких перемикання тригерів здійснюється одночасно;

в) Лічильники, в яких перемикання тригерів не здійснюється.

г) Немає правильної відповіді.

10.Лічильники з послідовним перенесенням це:

а) Лічильники, в яких перемикання тригерів здійснюється один за іншим;

б) Лічильники в яких перемикання тригерів здійснюється одночасно;

в) Лічильники, в яких перемикання тригерів не здійснюється.

г) Немає правильної відповіді.

11.Лічильники бувають:

а) Складючими та помножуючими; б) Складаючими та віднімаючими;

в) Віднімаючими та поділяючими. г) Немає правильної відповіді.

12.Двійковими називаються лічильники:

а)

З модулем рахунку

![]() ;

б) Змодулем рахунку

;

б) Змодулем рахунку

![]() ;

;

в)

З модулем рахунку

![]() .

г) Немає правильної

відповіді.

.

г) Немає правильної

відповіді.

14.9 Тестові завдання до практичної роботи за темою: «Вивчення роботи елементарної комірки оперативного запам’ятовуючого пристрою»

1.Оперативні запам’ятовуючі пристрої поділяються на:

а) паралельні та послідовні;

б) складаючі та віднімаючі;

в) статичні та динамічні

г) синхронні та асинхронні;

2.В статичних ОЗП інформація

а) постійно циркулює в масиві, відведеному для зберігання;

б) інформація постійно зберігається у відведеному для неї місці;

в) перетворюється з однієї системи числення в іншу;

г) збільшується або зменшується на одиницю

3.В динамічних ОЗП інформація

а) постійно циркулює в масиві, відведеному для зберігання;

б) інформація постійно зберігається у відведеному для неї місці;

в) перетворюється з однієї системи числення в іншу;

г) збільшується або зменшується на одиницю;

4.На схемах електричних принципових ІС ОЗП позначаються:

а) REM; б) ROM; в) RAM; г) RIM;

5.Для оперативних запам’ятовуючих пристроїв характерним є:

а) Лише режим зчитування;

б) Лише режим запису;

в) Лише режим зберігання4

г) Режими запису, зберігання та зчитування;

6.Статичні елементарні запам’ятовуючі комірки можуть бути реалізовані:

а) Виключно на біполярних транзисторах;

б) Виключно на польових транзисторах;

в) Як на біполярних, так і на польових транзисторах;

г) На конденсаторах;

7.Фрагментом структурної схеми динамічного ОЗП є:

а)

;

б) ;

;

в) ;

г)

;

г) ;

;

8.Недоліком статичних ОЗП є:

а) Низька швидкодія;

б) Висока ступінь інтеграції;

в) Складна схемотехнічна реалізація;

г) Немає правильної відповіді;

9.Перевагою статичних ОЗП є:

а) Висока швидкодія;

б) Висока ступінь інтеграції;

в) Складна схемотехнічна реалізація;

г) Немає правильної відповіді;

10.Перевагою динамічних ОЗП є:

а) Висока швидкодія;

б) Проста та дешева схемотехнічна реалізація;

в) Низька ступінь інтеграції;

г) Немає правильної відповіді;

11.Недоліком динамічних ОЗП є:

а) Низька швидкодія;

б) Проста та дешева схемотехнічна реалізація;

в) Висока ступінь інтеграції;

г) Немає правильної відповіді;

12.Інформація в ОЗП представлена у вигляді:

а) Виключно наявності з’єднань між ША та ШД;

б) Виключно відсутності з’єднань між ША та ШД;

в) У вигляді заряду на конденсаторі;

г) Наявності або відсутності з’єднань між шинами адреси та даних;

14.10 Тестові завдання до практичної роботи за темою: «Вивчення роботи елементарної комірки постійного запам’ятовуючого пристрою»

На схемах електричних принципових ІС ПЗП позначаються:

REM; в. ROM; с. RAM; d. RIM

Постійні запам’ятовуючі пристрої призначені для:

для зберігання інформації, яка залишається незмінною протягом всього часу роботи пристрою;

для зберігання інформації, яка змінюється при її зчитуванні;

для зберігання інформації, яка зникає при припиненні роботи пристрою;

для короткочасного збереження двійкового коду;

Які з перелічених режимів роботи є характерними для ПЗП:

Запису та зберігання; b. Лише запису;

Зберігання та зчитування; d. Немає правильної відповіді;

Інформація, що зберігається в ПЗП:

Знищується при її зчитуванні;

Не змінюється при її зчитуванні;

Частково змінюється при її зчитуванні;

Не зчитується;

Інформація в ПЗП представлена у вигляді:

Виключно наявності з’єднань між ША та ШД;

Виключно відсутності з’єднань між ША та ШД;

Немає правильної відповіді;

Наявності або відсутності з’єднань між шинами адреси та даних;

Постійні запам’ятовуючі пристрої поділяються на:

Паралельні та послідовні;

Двійкові та двійководесяткові;

Масочні, програмовані та репрограмовані;

Синхронні та асинхронні;

Елементом пам’яті ПЗП може бути:

Діод або резистор;

Діод або транзистор;

Транзистор або резистор;

Резистор або конденсатор;

До масочних ПЗП відносяться:

ПЗП, в яких інформація не записується.

ПЗП, в яких інформація записується декілька разів;

ПЗП, в яких інформація записується один раз користувачем;

ПЗП, в яких інформація записується один раз при їх виготовленні;

До програмованих ПЗП відносять:

ПЗП, в яких інформація записується декілька разів;

ПЗП, в яких інформація не записується.

ПЗП, в яких інформація записується один раз користувачем;

ПЗП, в яких інформація записується один раз при їх виготовленні;

До репрограмованих ПЗП відносяться:

ПЗП, в яких інформація записується декілька разів;

ПЗП, в яких інформація записується один раз користувачем;

ПЗП, в яких інформація записується один раз при їх виготовленні;

ПЗП, в яких інформація не записується.

Безпосередньо при виготовленні програмуються

Масочні ПЗП; b. Програмовані ПЗП;

Репрограмовані ПЗП; d. Немає правильної відповіді

Масочні ПЗП позначаються:

ROM; b. PROM; c. EPROM; d. EEPROM.

14.11 Тестові завдання до практичної роботи за темою: «Дослідження роботи перетворювачів сигналів»

1. Аналогово-цифровий перетворювач (АЦП) призначений для перетворення сигналів:

а) цифрових в аналогові; б) аналогових в цифрові;

в) світлових в звукові; г) звукових в цифрові коди.

2. На вхід АЦП поступає сигнал:

а) цифровий; б) звуковий; в) аналоговий; г) світловий.

3. З виходу АЦП поступає сигнал:

а) цифровий; б) звуковий; в) аналоговий; г) світловий.

4. По виду вихідного коду АЦП розрізняють:

а) тільки двійкові; б) тільки десяткові;

в) тільки логарифмічні; г) бувають АЦП всіх видів.

5. Компаратор – це:

а) схема порівняння; б) буферний регістр;

в) генератор тактових сигналів; г) перетворювач напруги.

6. Перетворення сигналу – це процес:

а)дискретний; б)інтегральний; в)тактовий; г)немає правильної відповіді.

7. Цифрово-аналоговий перетворювач (ЦАП) призначений для перетворення сигналів:

а) цифрових в аналогові; б) аналогових в цифрові;

в) світлових в звукові; г) звукових в цифрові коди.

8. На вхід ЦАП поступає сигнал:

а) цифровий; б) звуковий; в) аналоговий; г) світловий.

9. З виходу ЦАП поступає сигнал:

а) цифровий; б) звуковий; в) аналоговий; г) світловий.

10. Обробку інформації в пристроях перетворення зручніше вести у формі:

а) світловій. б) аналоговій; в) звуковій; г) цифровій;

11. Фізичні величини та процеси (первинна інформація) як правило носять характер сигналу:

а) цифровий; б) аналоговий; в) диференціальний; г) інтегральний.

12. Суть операції цифрово-аналогового перетворення полягає у:

а) формуванні сигналів, що відповідають кодовим словам дискретного сигналу;

б) формуванні кодових слів дискретного сигналу, що відповідають аналоговим сигналам;

в) додаванні цифрових сигналів до аналогових;

г) немає правильної відповіді.

14.4 Ключ від тестових завдань до попереднього контролю знань студентів

питання

№

№ тесту |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

14.1 |

а |

а |

а |

а |

а |

а |

а |

г |

а |

а |

а |

а |

14.2 |

а |

а |

б |

а |

а |

а |

в |

а |

б |

а |

а |

а |

14.3 |

в |

в |

б |

г |

в |

а |

в |

б |

в |

а |

г |

г |

14.4 |

а |

б |

а |

г |

в |

г |

а |

б |

б |

а |

в |

г |

14.5 |

б |

г |

б |

а |

а |

а |

в |

а |

б |

б |

а |

г |

14.6 |

г |

а |

г |

б |

в |

б |

а |

б |

б |

а |

г |

а |

14.7 |

г |

б |

а |

а |

в |

а |

б |

а |

б |

б |

б |

а |

14.8 |

а |

в |

а |

б |

б |

а |

в |

а |

б |

а |

б |

б |

14.9 |

в |

б |

а |

в |

г |

в |

в |

в |

а |

б |

а |

в |

14.10 |

B |

D |

A |

C |

A |

B |

A |

A |

C |

C |

B |

D |

14.11 |

б |

в |

а |

г |

а |

а |

г |

б |

а |

в |

а |

в |

Оцінювання тестових завдань з самоперевірки здійснюється за чотирьохбальною шкалою - «незадовільно», «задовільно», «добре», «відмінно»:

Оцінка «незадовільно» виставляється, якщо студент відповів правильно тільки на три питання з дванадцяти можливих.

Оцінка «задовільно» виставляється, якщо студент відповів правильно на три-шість питань з дванадцяти можливих.

Оцінка «добре» виставляється, якщо студент відповів правильно на сім-дев’ять питань з дванадцяти можливих.

Оцінка «відмінно» виставляється, якщо студент відповів правильно на десять-дванадцять питань з дванадцяти можливих.

РЕКОМЕНДОВАНА ЛІТЕРАТУРА

1. Алексеенко А.Г., Шагурин И.И. Микросхемотехника: Учебное пособие для вузов. – М.: Радио и связь, 1982. – 416с.

2. Бабич М.П., Жуков І.А. Комп’ютерна схемотехніка: Навчальний посібник. – К.: «МК-Прес», 2004. – 412с.

3. Карлащук В.И. Электронная лаборатория на IBM PC. Лабораторный приктикум на базе Electronics Workbench и MATLAB. Издание 5-е. – М.: СОЛОН-Пресс, 2004. – 800с.

4. Колонтаєвський Ю.П., Сосков А.Г. Промислова електроніка та мікро схемотехніка: теорія і практикум – К.: Каравела, 2003. – 368с.

5. Опадчий Ю.Ф. Аналоговая и цыфровая электроника (Полный курс): Учебник для вузов. – М.: Горячая линия – Телеком, 2002. – 768.с.

6. Токхейм Р. Основы цифровой электроники: Пер. с англ.. – М.: Мир, 1988. – 392с.

7. Файл довідка Electronics workbench 5.0C

8. Баскаков С.И. Радиотехнические цепи и сигналы. – M. Высш. шк., 1988.

9. Петров Б.Е., Романюк В.А. Радиопередающие устройства на полупроволниковых приборах. - M.: Высш. шк., 1989.

10. Долин П.А. Основы техники безопасности в электроустановках. – М.: Энергоатомиздат, 1984.

11. Охрана труда на предприятиях связи и охрана окружающей среды. / Н.И. Баклашев, Н.Ж. Китаева, П.Д. Терехов. – М.: Радио и связь, 1989.