Логические функции

Логическая функция - это функция, которая устанавливает соответствие между одним или несколькими высказываниями, которые называются аргументами функции, и высказыванием которое называется значением функции.

Это определение почти не отличается от определения числовой функции. Разница лишь та, что аргументом и значением числовой функции являются числа, а аргументом логической функции - высказывания.

Как можно составить логическую функцию? Очень просто.

Приведем пример: Пусть дано высказывание А. Оно может быть либо истинно, либо ложно. Определим высказывание В следующим образом: пусть В истинно, когда А ложно, и ложно когда А истинно.

Мы только что установили соответствие между высказыванием А и высказыванием В. Другими словами мы составили логическую функцию, аргументом которой является высказывание А и результатом высказывание В.

Функция, определённая таким образом, называется отрицанием и записывается так: ¬A . Читается так: не А.

Шифраторы

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) - преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

![]() где

где

![]() —

число входов,

—

число входов,

![]() —

число выходных двоичных разрядов.

—

число выходных двоичных разрядов.

Троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного (одноединичного или однонулевого) кода в троичный. При подаче сигнала ("1" в одноединичном коде или "0" в однонулевом коде) на один из n входов на выходе появляется троичный код номера активного входа.

Число входов и выходов в полном троичном шифраторе связано соотношением:

![]() ,

где

-

число входов,

-

число выходных троичных разрядов.

,

где

-

число входов,

-

число выходных троичных разрядов.

Число входов и выходов в полном k-ичном шифраторе связано соотношением:

![]() ,

где

-

число входов,

-

число выходных k-ичных разрядов,

,

где

-

число входов,

-

число выходных k-ичных разрядов,

![]() -

основание системы

счисления.

-

основание системы

счисления.

Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

Правила алгебры и логики

Алгебра логики (алгебра высказываний) — раздел математической логики, в котором изучаются логические операции над высказываниями[1]. Чаще всего предполагается (т. н. бинарная или двоичная логика, в отличие от, например, троичной логики), что высказывания могут быть только истинными или ложными.

Базовыми

элементами, которыми оперирует алгебра

логики, являются высказывания.

Высказывания строятся над множеством {B, ![]() ,

, ![]() ,

, ![]() ,

0, 1}, где B — непустое множество, над

элементами которого определены

три операции:

,

0, 1}, где B — непустое множество, над

элементами которого определены

три операции:

отрицание (унарная операция),

конъюнкция (бинарная),

дизъюнкция (бинарная),

а также константы — логический ноль 0 и логическая единица 1.

Дизъю́нкт — пропозициональная

формула,

являющаяся дизъюнкцией одного

или более литералов (например ![]() ). Конъюнкт — пропозициональная

формула,

являющаяся конъюнкцией одного

или более литералов (например

). Конъюнкт — пропозициональная

формула,

являющаяся конъюнкцией одного

или более литералов (например ![]() ).

).

4.

Дешифратор

(декодер) — комбинационное

устройство,

преобразующее n-разрядный двоичный,

троичный или k-ичный код в ![]() -ичный

одноединичный код, где

-

основание системы

счисления.

Логический сигнал появляется на том

выходе, порядковый номер которого

соответствует двоичному, троичному или

k-ичному коду.

Дешифраторы являются

устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции (операции).

-ичный

одноединичный код, где

-

основание системы

счисления.

Логический сигнал появляется на том

выходе, порядковый номер которого

соответствует двоичному, троичному или

k-ичному коду.

Дешифраторы являются

устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции (операции).

Двоичный дешифратор работает по следующему принципу: пусть дешифратор имеет N входов, на них подано двоичное слово xN − 1xN − 2...x0, тогда на выходе будем иметь такой код, разрядности меньшей или равной 2N, что разряд, номер которого равен входному слову, принимает значение единицы, все остальные разряды равны нулю. Очевидно, что максимально возможная разрядность выходного слова равна 2N. Такой дешифратор называется полным. Если часть входных наборов не используется, то число выходов меньше 2N, и дешифратор является неполным.

Часто дешифраторы дополняются входом разрешения работы. Если на этот вход поступает единица, то дешифратор функционирует, в ином случае на выходе дешифратора вырабатывается логический ноль вне зависимости от входных сигналов.

Существуют дешифраторы с инверсными выходами, у такого дешифратора выбранный разряд показан нулём.

Синтез логических схем

Синтезом логической схемы называется процедура получения логической схемы реализующую зачанную логическую функцию.

При синтезе логических схем используют логические элементы.

Набор логических функций, с помощью которого можно представить любую переключаемую функцию называют функционально полной системой или базисом.

Функционально полными системами являются базисы 1) И, ИЛИ, НЕ, 2) И, НЕ, 3) ИЛИ, НЕ, 4) И-ИЛИ-НЕ, 5) И-НЕ, 6) ИЛИ-НЕ.

Основным является базис И, ИЛИ, НЕ так как с помощью него можно записать любую сложную функцию в виде СДНФ и СКНФ. Базис называется избыточным, если какую либо функцию из нее можно исключить. Например в И, ИЛИ, НЕ можно исключить функцию И или ИЛИ.

При синтезе комбинационной схемы с несколькими выходами, каждый выход рассматривается как функция входных значений. Полученные функции минимизируются, и затем строится логическая схема в одном из заданных базисов.

При синтезе цифровых автоматов, в таблицу функционирования кроме выходных значений необходимо указывать и внутреннее состояние устройсва.

6. Mультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Аналоговые[1] и цифровые[1][2][3] мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка единиц/десятков ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа. Аналоговые мультиплексоры иногда называют ключами[4] или коммутаторами[1].

Устройство, противоположное мультиплексору по своей функции, называется демультиплексором. В случае применения аналоговых мультиплексоров (с применением ключей на полевых транзисторах) не существует различия между мультиплексором и демультиплексором и такие устройства могут называться коммутаторами

7. RS-триггер асинхронный

S |

R |

Q(t) |

Q(t) |

Q(t+1) |

Q(t+1) |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

не определено |

не определено |

1 |

1 |

1 |

0 |

не определено |

не определено |

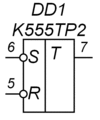

![]()

Асинхронный RS-триггер с инверсными входами

RS-триггер[10][11], или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

RS-триггеры иногда называют RS-фиксаторами[12].

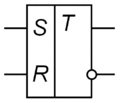

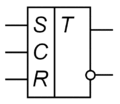

Условное

графическое обозначение асинхронного

RS-триггера

Условное

графическое обозначение асинхронного

RS-триггера

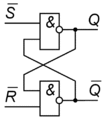

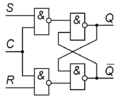

Логическая

схема асинхронного RS-триггера на

элементах 2И–НЕ

Логическая

схема асинхронного RS-триггера на

элементах 2И–НЕ

8. Демультиплексор — устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS. Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы - ИД.

Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

9. D-триггеры

D-триггеры также называют триггерами задержки(от англ. Delay).

D-триггер (D от англ. delay — задержка[13][14][15] либо от data[16] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсныесигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

D |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

10. Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.[1]

Сумматор - устройство, выполняющее операции арифметического сложения над двоичными числами.

В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.[1]

По способу реализации

механические

электромеханические

электронные

пневматические

По архитектуре

четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма по модулю;[5][неавторитетный источник?][6][неавторитетный источник?]

полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший разряд);

полные сумматоры — тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательныепозиционные системы счисления.[источник не указан 343 дня]

По способу действия

Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно, разряд за разрядом, на одном и том же одноразрядном оборудовании;

Параллельные (многоразрядные), в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование;

11. Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2.

Т-триггер асинхронный

Асинхронный Т-триггер не имеет входа синхронизации С.

Синхронный Т-триггер[17][18],

при единице на входе Т,

по каждому такту на входе С изменяет

своё логическое состояние на

противоположное, и не изменяет выходное

состояние при нуле на входе T.

Т-триггер может строиться на JK-триггере,

на двухступенчатом (Master-Slave, MS) D-триггере

и на двух одноступенчатых D-триггерах

и инверторе. Как можно видеть в таблице

истинности JK-триггера, он переходит в

инверсное состояние каждый раз при

одновременной подаче на входы J и Kлогической

1. Это свойство позволяет создать на

базе JK-триггера Т-триггер, объединяя

входы J и К.

Наличие в двухступенчатом (Master-Slave, MS)

D-триггере динамического входа С позволяет

получить на его основе T-триггер. При

этом инверсный выход Q соединяется

со входом D, а на вход С подаются

счётные импульсы. В результате триггер

при каждом счётном импульсе запоминает

значение ![]() ,

то есть будет переключаться в

противоположное состояние.

,

то есть будет переключаться в

противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

T |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

12. Сумматор параллельного действия оперирует параллельными кодами и представляет собой цепочку одноразрядных суммирующих схем, число которых соответствует разрядности суммируемых чисел. Их формируют как на базе комбинационных, так и накапливающих одноразрядных сумматоров. [1]

Сумматор параллельного действия характеризуется тем, что нее разряды числ. [2]

Сумматор параллельного действия выполняется многоразрядным, его каждый разряд образован одноразрядным сумматором. Каждый одноразрядный сумматор должен формировать сигнал суммы и сигнал переноса в старший разряд, если сумма, полученная при сложении двух чисел, превышав. [3]

Сумматор параллельного действия выполняется многоразрядным, его каждый разряд образован одноразрядным сумматором. [4]

Сумматоры параллельного действия, построенные на накопительных сумматорах SM, широко применялись в ЭВМ первого и второго поколений. [5]

Быстродействие сумматоров параллельного действия с последовательным переносом практически равно быстродействию сумматоров последовательного действия. Для повышения скорости работы в схему сумматора параллельного действия вводят дополнительные цепи для осуществления параллельного ( сквозного) переноса. [6]

Для сумматоров параллельного действия представление чисел дополнительном или обратном коде практически равноценно. [7]

13. JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний

14. Сумматоры последовательного действия уступают сумматорам параллельного действия по быстродействию, но зато они более экономичны по оборудованию и применяются только в некоторых ЦВМ с небольшим быстродействием. Наиболее распространенными являются сумматоры параллельного действия накапливающего типа.

Сумматор последовательного действия представляет собой счетчик, который осуществляет счет импульсов как в прямом ( обеспечивает сложение числа поступивших сигналов с числом, ранее записанном в счетчике), так и в обратном ( осуществляет вычитание числа поступивших на вход импульсов из числа, записанного в счетчике) направлениях.

Сумматор последовательного действия последовательно складывает разряды двух чисел с помощью одноразрядного сумматора.

Сумматор последовательного действия производит последовательное поразрядное сложение двух чисел с помощью одноразрядного сумматора.

В сумматоре последовательного действия применение обратных одов удваивает время суммирования, поскольку единица кругового ереноса возникает после окончания суммирования чисел.

В сумматорах последовательного действия сложение цифр одноименных разрядов обоих слагаемых осуществляется последовательно во времени, начиная с младшего разряда. При этом каждый раз учитывается перенос из предыдущего разряда.

15. Система счисле́ния — символический метод записи чисел, представление чисел с помощью письменных знаков.

Система счисления:

даёт представления множества чисел (целых и/или вещественных);

даёт каждому числу уникальное представление (или, по крайней мере, стандартное представление);

отражает алгебраическую и арифметическую структуру чисел.

Системы счисления подразделяются на позиционные, непозиционные и смешанные.

Чем больше основание системы счисления, тем меньшее количество разрядов (то есть записываемых цифр) требуется при записи числа в позиционных системах счисления.

Наиболее употребляемыми в настоящее время позиционными системами являются:

1 — единичная[1] (счёт на пальцах, зарубки, узелки «на память» и др.);

2 — двоичная (в дискретной математике, информатике, программировании);

3 — троичная;

8 — восьмеричная;

10 — десятичная (используется повсеместно);

12 — двенадцатеричная (счёт дюжинами);

16 — шестнадцатеричная (используется в программировании, информатике);

60 — шестидесятеричная (единицы измерения времени, измерение углов и, в частности, координат, долготы и широты).

16. Вычитание сводится к сложению дополнительного кода вычитаемого, т.е. отрицательного числа.

А - В = А + (-В)

Дополнительным кодом двоичного числа X в N-разрядной ячейке является число, дополняющее его до значения 2N/

Получить дополнительный код можно следующим путем

а) записать внутренне представление положительного числа X

б) инвертируется двоичный код числа (заменяем 0 на 1 и 1 на 0)

в) к полученному числу добавляем единицу

пример.

45-39 00101101 - 00100111 00000110 |

б) Инвертируем вычитаемое 11011000 в)Находим сумму вычитаемое + 1 11011000 + 1 11011001 Результат: 00101101 11011001 1 00000110 |

1 выходит за пределы 8-разрядной сетки и исчезает

"0" в старшем (8)разряде свидетельствует о знаке "+" числа:

"1" - соответствует знаку "минус"

Когда на управляющую шину подается логический 0 (Add/Ssub=0), схема производит сложение

Когда на управляющую шину подается логическая 1 (Add/Ssub=1), схема производит вычитание

17. 1. Для перевода двоичного числа в десятичное необходимо его записать в виде многочлена, состоящего из произведений цифр числа и соответствующей степени числа 2, и вычислить по правилам десятичной арифметики:

![]()

При переводе удобно пользоваться таблицей степеней двойки:

Таблица 4. Степени числа 2

n (степень) |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

1 |

2 |

4 |

8 |

16 |

32 |

64 |

128 |

256 |

512 |

1024 |

Пример

. Число ![]() перевести

в десятичную систему счисления.

перевести

в десятичную систему счисления.

![]()

Таблица 5. Степени числа 8

n (степень) |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

|

1 |

8 |

64 |

512 |

4096 |

32768 |

262144 |

Таблица 6. Степени числа 16

n (степень) |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

|

1 |

16 |

256 |

4096 |

65536 |

1048576 |

16777216 |

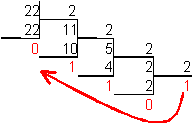

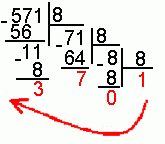

4. Для перевода десятичного числа в двоичную систему его необходимо последовательно делить на 2 до тех пор, пока не останется остаток, меньший или равный 1. Число в двоичной системе записывается как последовательность последнего результата деления и остатков от деления в обратном порядке.

Пример. Число ![]() перевести

в двоичную систему счисления.

перевести

в двоичную систему счисления.

5. Для перевода десятичного числа в восьмеричную систему его необходимо последовательно делить на 8 до тех пор, пока не останется остаток, меньший или равный 7. Число в восьмеричной системе записывается как последовательность цифр последнего результата деления и остатков от деления в обратном порядке.

Пример. Число ![]() перевести

в восьмеричную систему счисления.

перевести

в восьмеричную систему счисления.

![]()

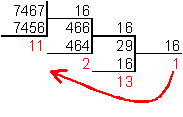

6. Для перевода десятичного числа в шестнадцатеричную систему его необходимо последовательно делить на 16 до тех пор, пока не останется остаток, меньший или равный 15. Число в шестнадцатеричной системе записывается как последовательность цифр последнего результата деления и остатков от деления в обратном порядке.

Пример. Число ![]() перевести

в шестнадцатеричную систему счисления.

перевести

в шестнадцатеричную систему счисления.

7. Чтобы перевести число из двоичной системы в восьмеричную, его нужно разбить на триады (тройки цифр), начиная с младшего разряда, в случае необходимости дополнив старшую триаду нулями, и каждую триаду заменить соответствующей восьмеричной цифрой (табл. 3).

Пример. Число ![]() перевести

в восьмеричную систему счисления.

перевести

в восьмеричную систему счисления.

![]()

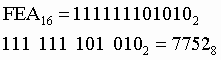

8. Чтобы перевести число из двоичной системы в шестнадцатеричную, его нужно разбить на тетрады (четверки цифр), начиная с младшего разряда, в случае необходимости дополнив старшую тетраду нулями, и каждую тетраду заменить соответствующей восьмеричной цифрой (табл. 3).

Пример. Число ![]() перевести

в шестнадцатеричную систему счисления.

перевести

в шестнадцатеричную систему счисления.

![]()

9. Для перевода восьмеричного числа в двоичное необходимо каждую цифру заменить эквивалентной ей двоичной триадой.

Пример. Число ![]() перевести

в двоичную систему счисления.

перевести

в двоичную систему счисления.

![]()

10. Для перевода шестнадцатеричного числа в двоичное необходимо каждую цифру заменить эквивалентной ей двоичной тетрадой.

Пример. Число ![]() перевести

в двоичную систему счисления.

перевести

в двоичную систему счисления.

![]()

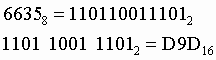

11. При переходе из восьмеричной системы счисления в шестнадцатеричную и обратно, необходим промежуточный перевод чисел в двоичную систему.

Пример

1. Число ![]() перевести

в восьмеричную систему счисления.

перевести

в восьмеричную систему счисления.

Пример

2. Число ![]() перевести

в шестнадцатеричную систему счисления.

перевести

в шестнадцатеричную систему счисления.

18. RS-триггер синхронный

C |

S |

R |

Q(t) |

Q(t+1) |

0 |

x |

x |

0 |

0 |

1 |

1 |

|||

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

не определено |

1 |

1 |

1 |

1 |

не определено |

Алгоритм функционирования синхронного RS-триггера можно представить формулой

![]()

где x — неопределённое состояние.

Условное

графическое обозначение синхронного

RS-триггера

Условное

графическое обозначение синхронного

RS-триггера

Схема

синхронного RS-триггера на элементах

2И-НЕ

Схема

синхронного RS-триггера на элементах

2И-НЕ

19. В случае десятичной системы счисления получим:

24,732 = 2·101+4·100+7·10-1+3·10-2

Перевод дробного числа из двоичной системы счисления в десятичную производится по следующей схеме:

101101,1012 = 1·25+0·24+1·23+1·22+0·21+1·20+1·2-1+0·2-2+1·2-3=45,625

Перевод дробного числа из десятичной системы счисления в двоичную осуществляется по следующему алгоритму:

Вначале переводится целая часть десятичной дроби в двоичную систему счисления;

Затем дробная часть десятичной дроби умножается на основание двоичной системы счисления;

В полученном произведении выделяется целая часть, которая принимается в качестве значения первого после запятой разряда числа в двоичной системе счисления;

Алгоритм завершается, если дробная часть полученного произведения равна нулю или если достигнута требуемая точность вычислений. В противном случае вычисления продолжаются с предыдущего шага.

Пример: Требуется перевести дробное десятичное число 206,116 в дробное двоичное число.

Перевод целой части дает 20610=110011102 по ранее описанным алгоритмам; дробную часть умножаем на основание 2, занося целые части произведения в разряды после запятой искомого дробного двоичного числа:

.116 • 2 = 0.232

.232 • 2 = 0.464

.464 • 2 = 0.928

.928 • 2 = 1.856

.856 • 2 = 1.712

.712 • 2 = 1.424

.424 • 2 = 0.848

.848 • 2 = 1.696

.696 • 2 = 1.392

.784 • 2 = 0.784

и т.д.

Получим: 20610=11001110,00011101102

20. JK-триггер[19][20] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[21].

Алгоритм функционирования JK-триггера можно представить формулой

![]()

J |

K |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

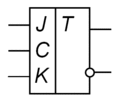

Условное

графическое обозначение JK-триггера со

статическим входом С

Условное

графическое обозначение JK-триггера со

статическим входом С

21. Правила выполнения арифметических действий над двоичными числами задаются таблицами двоичных сложения, вычитания и умножения.

Таблица двоичного сложения |

Таблица двоичного вычитания |

Таблица двоичного умножения |

0+0=0 0+1=1 1+0=1 1+1=10 |

0-0=0 1-0=1 1-1=0 10-1=1 |

0 |

При сложении двоичных чисел в каждом разряде производится сложение цифр слагаемых и переноса из соседнего младшего разряда, если он имеется. При этом необходимо учитывать, что 1+1 дают нуль в данном разряде и единицу переноса в следующий.

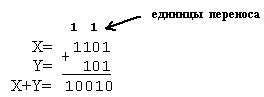

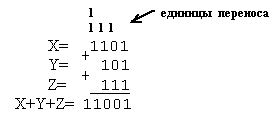

Пример. Выполнить сложение двоичных чисел: а) X=1101, Y=101;

Результат 1101+101=10010.

б) X=1101, Y=101, Z=111;

Результат 1101+101+111=11001.

При вычитании двоичных чисел в данном разряде при необходимости занимается 1 из старшего разряда. Эта занимаемая 1 равна двум 1 данного разряда.

Пример. Заданы двоичные числа X=10010 и Y=101. Вычислить X-Y.

Результат 10010 - 101=1101.

Умножение двоичных чисел производится по тем же правилам, что и для десятичных с помощью таблиц двоичного умножения и сложения.

Пример. 1001 101=?

Результат 1001 101=101101.

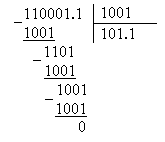

Деление двоичных чисел производится по тем же правилам, что и для десятичных. При этом используются таблицы двоичного умножения и вычитания.

Пример. 1100.011 : 10.01=?

Результат 1100.011 : 10.01=101.1.