- •Вопрос 1 - Основные свойства цифровых устройств (цу) обработки сигнала. Элементная база цу. Классификация цу.

- •Вопрос 2 - Функциональный преобразователь (фп) на программируемой логической матрице (плм). Структурная схема и работа фп. Реализация контерма и переключательной функции на плм.

- •Вопрос 3 - Функциональный преобразователь (фп) на программируемой матрице логики (пмл). Структурная схема и работа фп. Реализация системы уравнений в нормальной дизъюнктивной форме (ндф) на пмл.

- •Вопрос 4 - Функциональный преобразователь (фп) табличный lut. Структурная схема и работа фп. Реализация переключательных функций на пзу.

- •Вопрос 5 - Функциональный преобразователь (фп) на мультиплексоре. Структурная схема и работа фп фирмы Actel. Реализация переключательных функций на мультиплексоре.

- •Вопрос 6 - Функциональный преобразователь (фп) на программируемом логическом устройстве (плу). Структурная схема и работа плу. Реализация секции цифрового автомата на плу.

- •Вопрос 7 - Семейство плис max 7000. Общая характеристика семейства. Структурная схема плис max 7000. Назначение элементов структурной схемы.

- •Вопрос 8 - Структурная схема макроячейки плис max 7000. Основные характеристики ячейки. Назначение логического и параллельного расширителей.

- •Вопрос 9 - Семейство flex10k. Общая характеристика семейства. Структурная схема плис семейства flex10k. Назначение элементов структурной схемы.

- •Вопрос 10 - Структурная схема логического блока и логического элемента плис семейства flex10k. Назначение элементов структурной схемы.

- •Вопрос 12 - Организация процесса обработки информации. Основные характеристики последовательного и потокового (конвейерного) стилей обработки.

- •Вопрос 13 - Трехстабильный порт. Назначение, область применения. Использование примитивы tri для проектирования трехстабильного порта.

- •Вопрос 14 - Двунаправленный порт. Назначение, область применения. Использование мегафункции lpm_bustri для проектирования двунаправленного порта.

- •Вопрос 15 - Реализация звена нерекурсивного фильтра типа tdf II с использованием мегафункции lpm_mult. Организация конвейерной обработки.

- •Вопрос 16 - Реализация звена рекурсивного фильтра типа tdf II с использованием мегафункции lpm_mult. Организация конвейерной обработки.

- •Вопрос 19 - Разработка иерархических проектов. Способы подключения к проекту модулей нижнего уровня. Способы использования модулей.

- •Вопрос 20 - Программирование и конфигурирование плис. Способы программирования и конфигурирования (конфигурационная микросхема, пассивная последовательная (ps) и jtag).

- •Вопрос 21 - Языки описания аппаратуры. Язык ahdl. Структура проекта текстового описания модуля. Алфавит языка. Строчные и блочные комментарии (назначение, синтаксис, применение).

- •Вопрос 22 - Имена (символические, модуля, вывода) в языке ahdl. Назначение, синтаксис, применение.

- •Вопрос 23 - Константы (литеральные, именованные, параметры) в языке ahdl. Назначение, синтаксис, применение.

- •Порты модуля

- •Порты модулей нижнего уровня

- •Вопрос 25 - Арифметические, логические операторы и операторы сравнения языка ahdl. Назначение, синтаксис, область применения в текстовом проекте.

- •Вопрос 26 - Логические выражения и уравнения языка ahdl. Логические уравнения управления. Назначение, синтаксис, применение.

- •Вопрос 27 - Условный оператор If Then. Назначение, синтаксис и применение оператора.

- •Вопрос 28 - Условный оператор If Generate. Назначение, синтаксис и применение оператора.

- •Вопрос 29 - Оператор выбора Case. Назначение, синтаксис и применение оператора.

- •Вопрос 30 - Таблица истинности Truth Table. Назначение, синтаксис и применение оператора.

- •Вопрос 31 - Оператор цикла For Generate. Назначение, синтаксис и применение оператора.

- •Вопрос 32 - Оператор объявления значения по умолчанию Defaults. Назначение, синтаксис и применение оператора.

- •Вопрос 33 - Оператор контроля Assert. Назначение, синтаксис и применение оператора.

- •Вопрос 34 - Операторы заголовка Title и задания опции Options. Назначение, синтаксис и применение операторов.

- •Вопрос 36 - Оператор задания константы Constant. Назначение, синтаксис и применение оператора.

- •Вопрос 37 - Оператор обозначения Define. Назначение, синтаксис и применение оператора.

- •Вопрос 38 - Оператор объявления параметра Parameters. Назначение, синтаксис и применение оператора.

- •Вопрос 39 - Оператор описания прототипа Function Prototype. Назначение и синтаксис оператора.

- •Вопрос 40 - Оператор непосредственного обращения к прототипу In-Line Logic Function Reference. Назначение, синтаксис и применение оператора. Позиционное и именное присвоение.

Вопрос 20 - Программирование и конфигурирование плис. Способы программирования и конфигурирования (конфигурационная микросхема, пассивная последовательная (ps) и jtag).

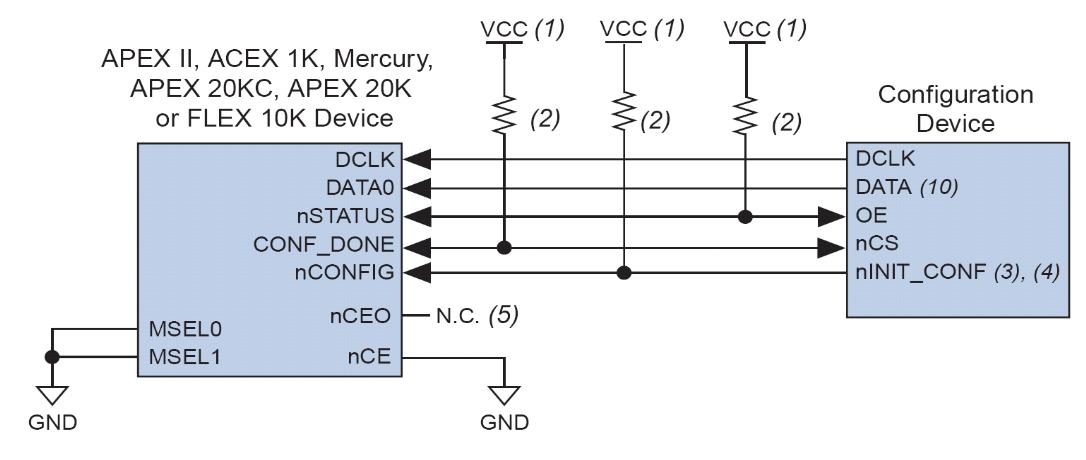

1. Configuration Device – Конфигурационная микросхема

2. PS – Пассивная последовательная (Passive Serial)

3. PPS – Синхронная пассивная параллельная (Passive Parallel Synchronous)

4. PPA – Асинхронная пассивная параллельная (Passive Parallel Asynchronous)

5. PSA – Асинхронная пассивная последовательная (Passive Serial Asynchronous)

6. JTAG – Конфигурирование по выводам JTAG Joint Test Action Group – Объединенная группа по вопросам тестирования )

Конфигурационная микросхема:

Примечания к рисунку:

1) Подтягивающий нагрузочный резистор подключен к напряжению питания

конфигурационной микросхемы.

2) Для микросхем APEX 20KE и APEX 20KC все подтягивающие нагрузочные

резисторы имеют номинал 1 кОм (или 10 кОм). Выводы OE и nCS микро-

схем EPC16, EPC8, и EPC2 имеют внутренние подтягивающие резисторы,

конфигурируемые пользователем. При использовании внутренних подтяги-

вающих резисторов, внешние резисторы не используются.

3) Вывод nINIT_CONF есть только у микросхем EPC2, EPC8, и EPC16. Если

вывод nINIT_CONF отсутствует (например, у микросхемы EPC1) или не ис-

пользуется, то вывод nCONFIG конфигурируемой микросхемы подключает-

ся к напряжению питания VCC (непосредственно или через резистор).

4) В микросхемах EPC16, EPC8, и EPC2 вывод nINIT_CONF имеет встроен-

ный подтягивающий резистор. При этом внешний резистор на выводе

nINIT_CONF не используется.

5) Вывод nCEO не подключается.

6) Для гарантии успешного конфигурирования при возможном разновременном

включении питания конфигурируемой (APEX 20KE) и конфигурирующей

микросхем, вывод nCONFIG необходимо подтянуть к напряжению VCCINT.

7) В микросхемах EPC16, EPC8, и EPC2 вывод nINIT_CONF имеет встроен-

ный подтягивающий резистор номиналом 10 кОм. Вывод nCONFIG конфи-

гурируемой микросхемы через резистор 10 кОм необходимо подключить к

напряжению питания VCCINT.

8) Для развязки источников напряжения 1,8 В и 3,3 В, при конфигурировании

микросхем APEX 20KE, между выводом nCONFIG микросхемы APEX

20KE и выводом nINIT_CONF конфигурирующей микросхемы необходимо

включить диод. Пороговое напряжение диода должно быть не более 0,7 В.

При этом вывод открытого стока nINIT_CONF может находится либо в со-

стоянии "0", либо в третьем состоянии.

9) Микросхемы EPC16, EPC8, и EPC2 не используются для конфигурирования

микросхем FLEX 6000.

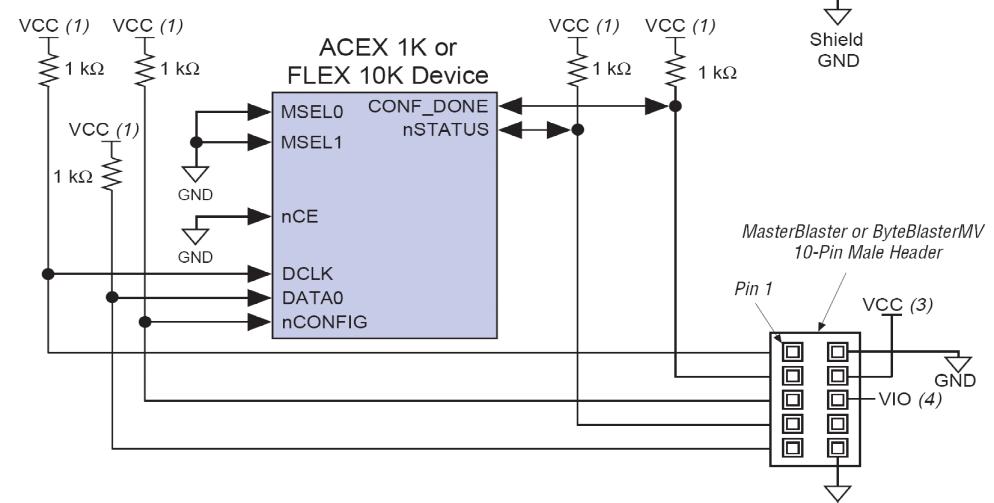

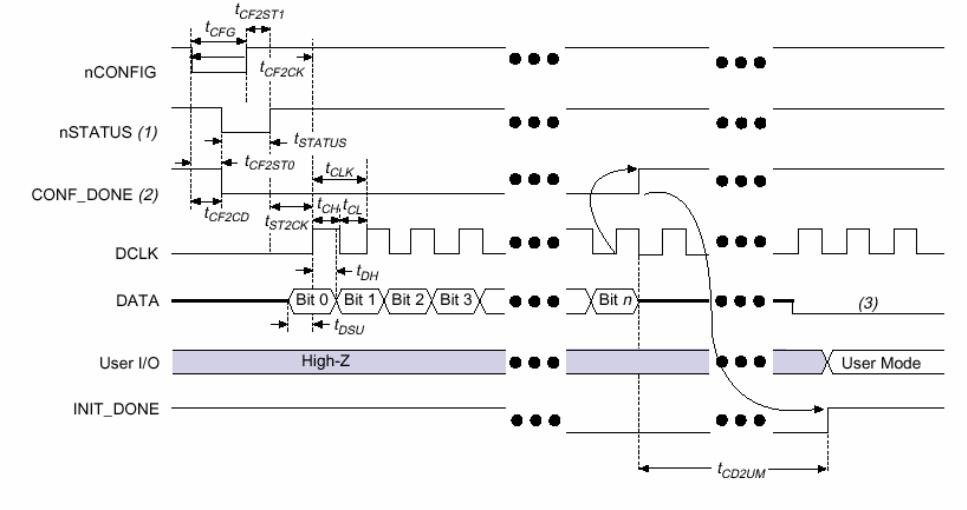

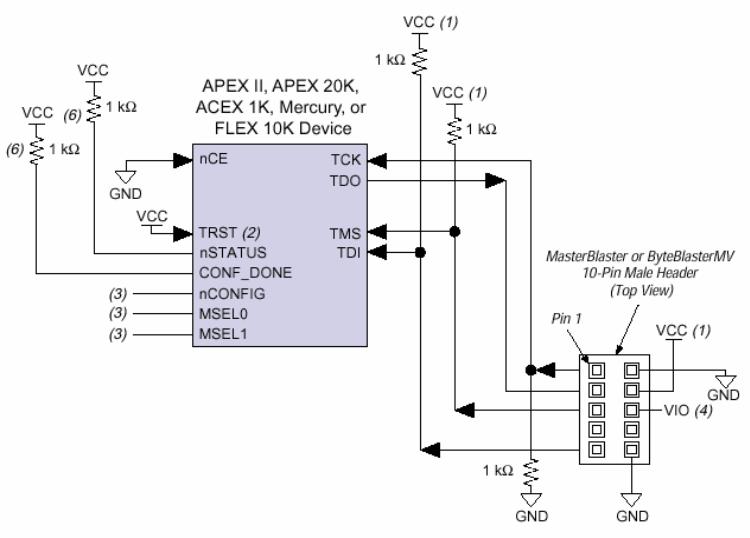

PS – Пассивная последовательная:

В пассивном последовательном режиме конфигурирования (Passive Serial)

(PS-конфигурировании) с помощью загрузочного кабеля главный контроллер за-

гружает данные из внешнего запоминающего устройства в микросхемы APEX

II, APEX 20K, Mercury, ACEX 1K, FLEX 10K, FLEX 6000 через кабель

MasterBlaster или ByteBlasterMV. Для начала конфигурирования в этом режи-

ме загрузочное устройство обеспечивает изменение уровня сигнала от "0" в "1"

на выводе nCONFIG. Программирующая аппаратура затем побитно передает

конфигурационные данные на вывод DATA микросхемы (в микросхемах APEX

II, APEX 20K, Mercury, ACEX 1K, FLEX 10K используется вывод DATA0, а в

микросхемах FLEX 6000 - вывод DATA). Данные синхронно принимаются

конфигурируемой микросхемой до момента перехода вывода CONF_DONE в

состояние "1". При использовании программирующей аппаратуры для микро-

схем APEX II, APEX 20K, Mercury, ACEX 1K, FLEX 10K, FLEX 6000 опция

"Auto-Restart Configuration on Frame Error" не влияет на цикл конфигурации,

поскольку САПР MAX+PLUS II или QUARTUS II перезапускает конфигуриро-

вание при обнаружении ошибки.

Схема PS-конфигурирования микросхем ACEX 1K, FLEX 10K с использованием загрузочных устройств

MasterBlaster или ByteBlasterMV приведена на рис.:

Примечания к рисунку:

1) Подтягивающий резистор должен быть подключен к тому же напря-

жению питания, что и загрузочное устройство MasterBlaster или

ByteBlasterMV (вывод VIO), за исключением микросхем APEX

20KE и APEX 20KC. Для микросхем APEX 20KE и APEX 20KC для

подтягивания напряжения на выводе nCONFIG до напряжения

VCCINT используется резистор 10 кОм.

2) Для микросхем APEX 20KE и APEX 20KC используется подтяги-

вающий резистор 10 кОм.

3) Вывод nCEO последней микросхемы в цепочке конфигурирования

оставляется неподключенным.

4) Напряжение питания составляет:

Для загрузочного устройства MasterBlaster - VCC=3,3 В или 5 В.

Для загрузочного устройства MasterBlasterMV VCC = 3,3 В или 5 В.

5) На вывод 6 разъема подается опорное напряжение VIO выходного бу-

фера MasterBlaster. Напряжение VIO должно быть согласовано с на-

пряжением VCCIO

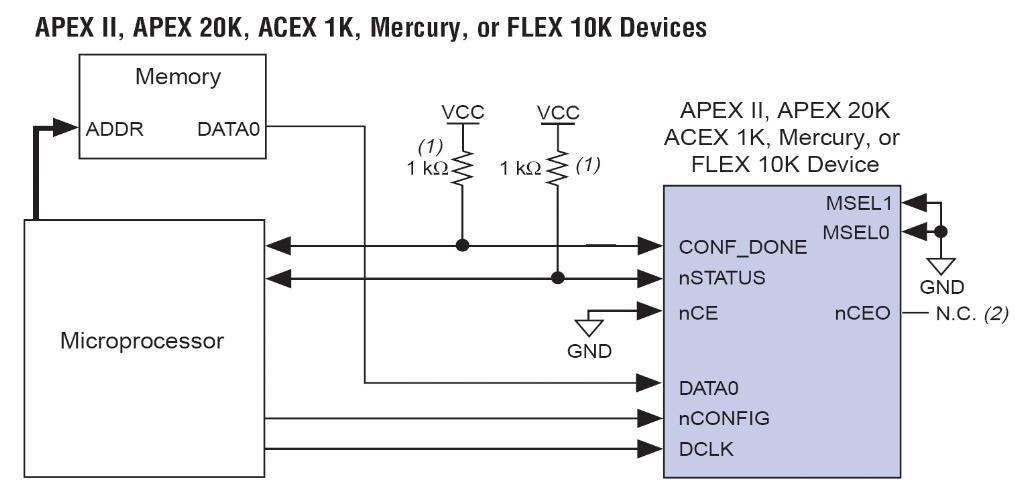

Схема PS-конфигурирования с помощью микропроцессора:

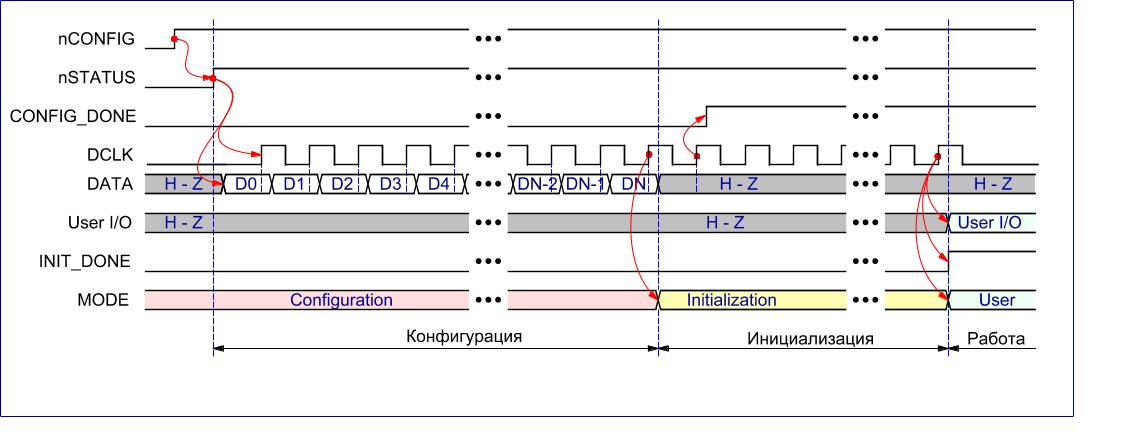

Временные диаграммы при конфигурировании с помощью микропроцессора:

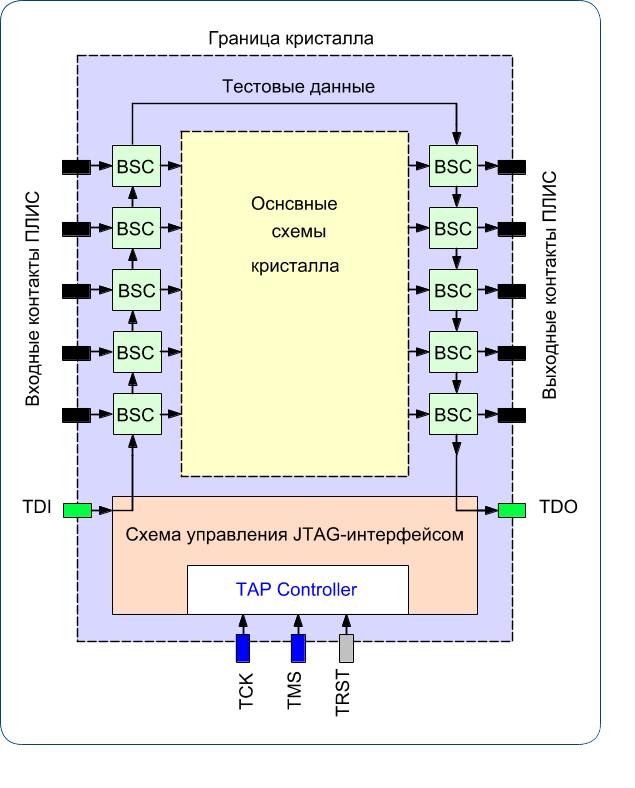

JTAG-программирование:

Для загрузки конфигурационных данных в микросхемы может использо-

ваться схема JTAG. Объединенная группа по вопросам тестирования (JTAG -

Joint Test Action Group) разработала спецификации для периферийного скани-

рования (BST – Boundary Scan Test). BST-технология позволяет выполнить эф-

фективное тестирование компонентов на прецизионных печатных платах (PCB –

Printed Circuit Board). BST-технология может тестировать выводы без исполь-

зования щупов и пробников (обычный мультиметр) и выполняет сбор необхо-

димых функциональных данных в нормальном режиме функционирования мик-

росхемы.

Для работы в JTAG-режиме используются четыре выделенных вывода:

TDI, TDO, TMS, и TCK, и вспомогательный вывод TRST. Все остальные выво-

ды во время JTAG-конфигурирования находятся в третьем состоянии. JTAG-

конфигурирование нельзя начинать до завершения других режимов конфигури-

рования.

BSC – Ячейки граничного сканирования (Boundary Scan Cells)

TDI - Вход тестовых данных (Test data intput)

TDO - Выход тестовых данных (Test data output)

TMS - Выбор режима тестирования (Test mode select )

TCK - Тактовый вход контроллера BST (Test clock input)

TRST - Вход прекращения тестирования (Test reset input)