- •Вопрос 1 - Основные свойства цифровых устройств (цу) обработки сигнала. Элементная база цу. Классификация цу.

- •Вопрос 2 - Функциональный преобразователь (фп) на программируемой логической матрице (плм). Структурная схема и работа фп. Реализация контерма и переключательной функции на плм.

- •Вопрос 3 - Функциональный преобразователь (фп) на программируемой матрице логики (пмл). Структурная схема и работа фп. Реализация системы уравнений в нормальной дизъюнктивной форме (ндф) на пмл.

- •Вопрос 4 - Функциональный преобразователь (фп) табличный lut. Структурная схема и работа фп. Реализация переключательных функций на пзу.

- •Вопрос 5 - Функциональный преобразователь (фп) на мультиплексоре. Структурная схема и работа фп фирмы Actel. Реализация переключательных функций на мультиплексоре.

- •Вопрос 6 - Функциональный преобразователь (фп) на программируемом логическом устройстве (плу). Структурная схема и работа плу. Реализация секции цифрового автомата на плу.

- •Вопрос 7 - Семейство плис max 7000. Общая характеристика семейства. Структурная схема плис max 7000. Назначение элементов структурной схемы.

- •Вопрос 8 - Структурная схема макроячейки плис max 7000. Основные характеристики ячейки. Назначение логического и параллельного расширителей.

- •Вопрос 9 - Семейство flex10k. Общая характеристика семейства. Структурная схема плис семейства flex10k. Назначение элементов структурной схемы.

- •Вопрос 10 - Структурная схема логического блока и логического элемента плис семейства flex10k. Назначение элементов структурной схемы.

- •Вопрос 12 - Организация процесса обработки информации. Основные характеристики последовательного и потокового (конвейерного) стилей обработки.

- •Вопрос 13 - Трехстабильный порт. Назначение, область применения. Использование примитивы tri для проектирования трехстабильного порта.

- •Вопрос 14 - Двунаправленный порт. Назначение, область применения. Использование мегафункции lpm_bustri для проектирования двунаправленного порта.

- •Вопрос 15 - Реализация звена нерекурсивного фильтра типа tdf II с использованием мегафункции lpm_mult. Организация конвейерной обработки.

- •Вопрос 16 - Реализация звена рекурсивного фильтра типа tdf II с использованием мегафункции lpm_mult. Организация конвейерной обработки.

- •Вопрос 19 - Разработка иерархических проектов. Способы подключения к проекту модулей нижнего уровня. Способы использования модулей.

- •Вопрос 20 - Программирование и конфигурирование плис. Способы программирования и конфигурирования (конфигурационная микросхема, пассивная последовательная (ps) и jtag).

- •Вопрос 21 - Языки описания аппаратуры. Язык ahdl. Структура проекта текстового описания модуля. Алфавит языка. Строчные и блочные комментарии (назначение, синтаксис, применение).

- •Вопрос 22 - Имена (символические, модуля, вывода) в языке ahdl. Назначение, синтаксис, применение.

- •Вопрос 23 - Константы (литеральные, именованные, параметры) в языке ahdl. Назначение, синтаксис, применение.

- •Порты модуля

- •Порты модулей нижнего уровня

- •Вопрос 25 - Арифметические, логические операторы и операторы сравнения языка ahdl. Назначение, синтаксис, область применения в текстовом проекте.

- •Вопрос 26 - Логические выражения и уравнения языка ahdl. Логические уравнения управления. Назначение, синтаксис, применение.

- •Вопрос 27 - Условный оператор If Then. Назначение, синтаксис и применение оператора.

- •Вопрос 28 - Условный оператор If Generate. Назначение, синтаксис и применение оператора.

- •Вопрос 29 - Оператор выбора Case. Назначение, синтаксис и применение оператора.

- •Вопрос 30 - Таблица истинности Truth Table. Назначение, синтаксис и применение оператора.

- •Вопрос 31 - Оператор цикла For Generate. Назначение, синтаксис и применение оператора.

- •Вопрос 32 - Оператор объявления значения по умолчанию Defaults. Назначение, синтаксис и применение оператора.

- •Вопрос 33 - Оператор контроля Assert. Назначение, синтаксис и применение оператора.

- •Вопрос 34 - Операторы заголовка Title и задания опции Options. Назначение, синтаксис и применение операторов.

- •Вопрос 36 - Оператор задания константы Constant. Назначение, синтаксис и применение оператора.

- •Вопрос 37 - Оператор обозначения Define. Назначение, синтаксис и применение оператора.

- •Вопрос 38 - Оператор объявления параметра Parameters. Назначение, синтаксис и применение оператора.

- •Вопрос 39 - Оператор описания прототипа Function Prototype. Назначение и синтаксис оператора.

- •Вопрос 40 - Оператор непосредственного обращения к прототипу In-Line Logic Function Reference. Назначение, синтаксис и применение оператора. Позиционное и именное присвоение.

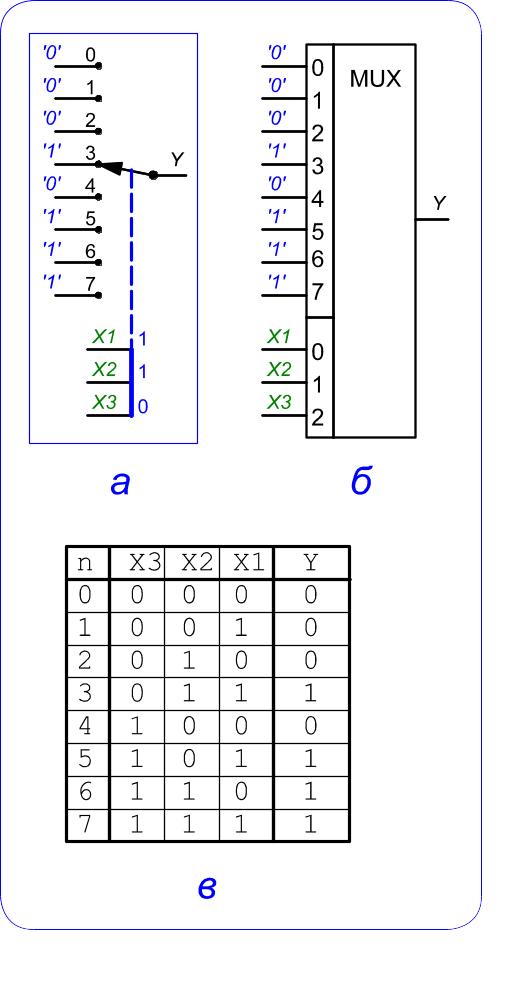

Вопрос 5 - Функциональный преобразователь (фп) на мультиплексоре. Структурная схема и работа фп фирмы Actel. Реализация переключательных функций на мультиплексоре.

Функциональный преобразователь на мультиплексоре:

Формирование “мажоритарной функции”.

MUX – мультиплексор;

‘0’, ‘1’ – логические уровни сигналов;

X1, X2, X3 – информационные сигналы;

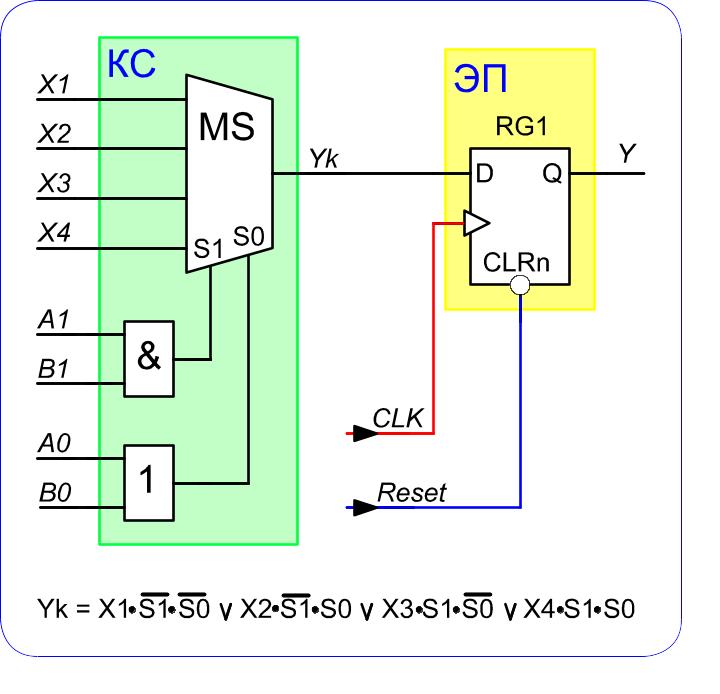

Функциональный преобразователь фирмы Actel:

КС – комбинационная схема;

MS – мультиплексор 4 → 1;

X1..X4 – входы ФП;

A1, A0, B1, B0 – входы ФП;

Y – выход ФП;

S1..S0 – адресные входы мультиплексора;

ЭП – элемент памяти;

RG1 - триггер;

CLK (Clock) – вход синхронизации;

Reset – сброс триггера;

D – информационный вход триггера;

Q - информационный выход триггера;

CLRn – вход сброса триггера;

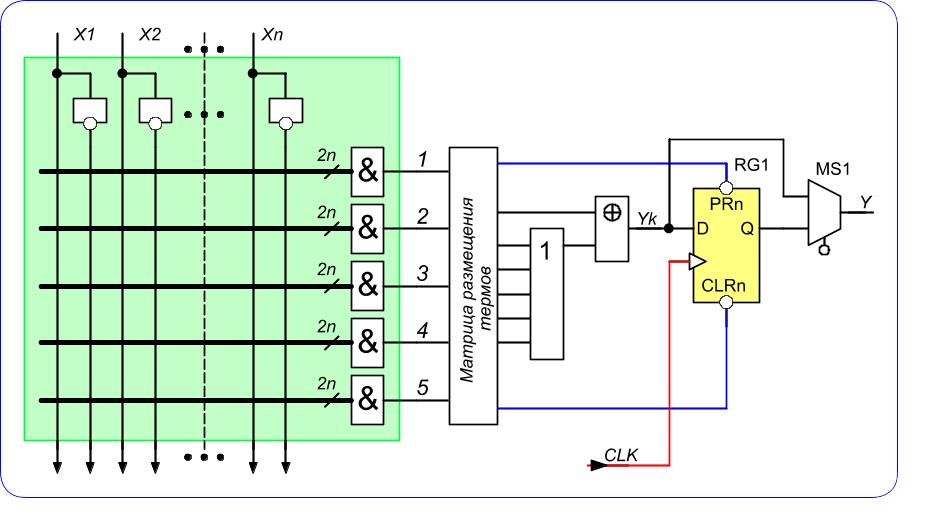

Вопрос 6 - Функциональный преобразователь (фп) на программируемом логическом устройстве (плу). Структурная схема и работа плу. Реализация секции цифрового автомата на плу.

Вопрос 7 - Семейство плис max 7000. Общая характеристика семейства. Структурная схема плис max 7000. Назначение элементов структурной схемы.

Общая характеристика семейства:

Тип конфигурационной памяти: EEPROM;

Комбинационная часть ЛЭ: программируемая матричная логика (ПМЛ);

Способы программирования:

Вне системы: Программатор ASAP2 (фирмы ALTERA);

В составе системы (ISP): ByteBlaster, BiteBlaster, JTAG.

Защита информации: Бит секретности.

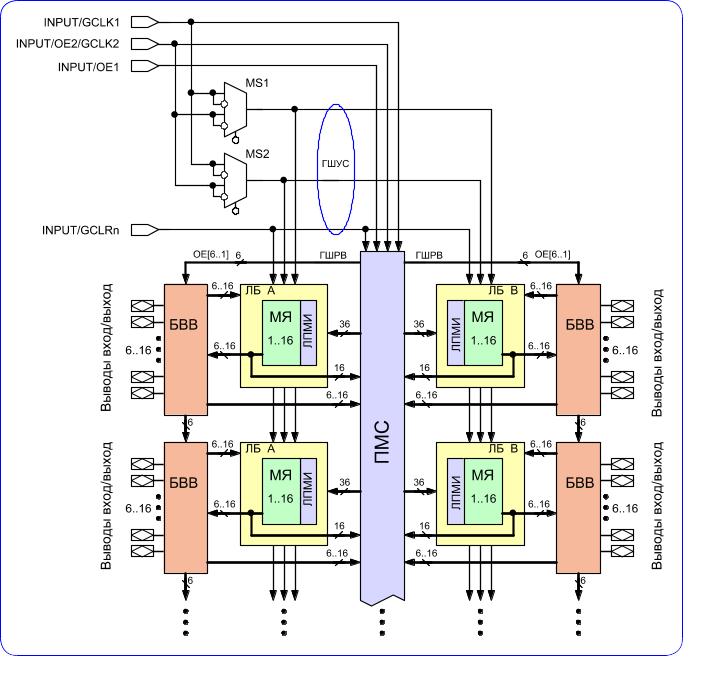

Структура ПЛИС MAX 7000S:

ЛБ – логический блок;

МЯ – макроячейка;

ЛПМИ – локальная программируемая матрица И;

ПМС – программируемая матрица соединений;

БВВ – блок ввода\вывода;

ГШУС – глобальная шина управляющих сигналов;

ГШРВ – глобальная шина разрешения выхода;

OE (Output Enable) – разрешение выхода;

GCLK (Global Clock) – глобальная синхронизация;

GCLR (Global Clear) – глобальная очистка триггеров ПЛИС

Вопрос 8 - Структурная схема макроячейки плис max 7000. Основные характеристики ячейки. Назначение логического и параллельного расширителей.

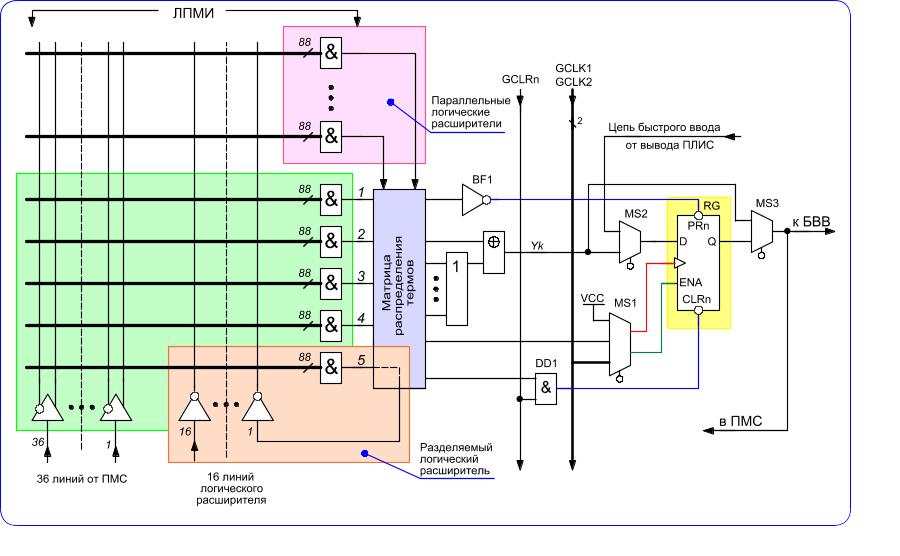

Структура макроячейки ПЛИС MAX 7000S:

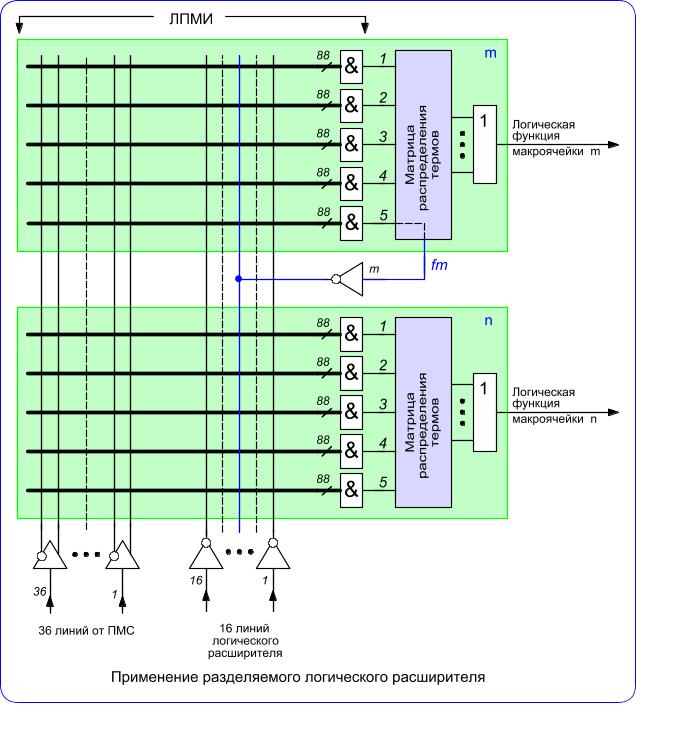

Логический расширитель MAX 7000S:

Скобочные формы

fm = x1 x2 x3;

Yk = x1 x2 x3 v x1 x2 x3 x5 v x1 x2 x3 x7 x9 = fm (1 v x5 v x7 x9);

Yn = x1 x2 x3 x7 v x1 x2 x3 x8 x v x3 x4 x9 = fm (x7 v x8) v x3 x4 x9;

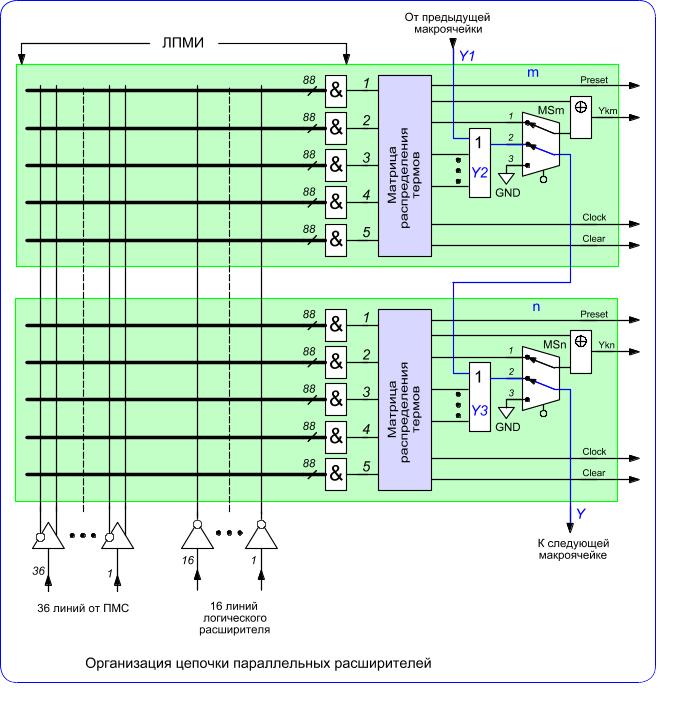

Параллельный расширитель MAX 7000S:

Y = f1 v f2 v … v fm; m > 5;

m = 14.

Y = f1 v f2 v … v f14;

Y = (f1 v…v f5) v (f6 v…v f10) v (f11 v…v f14);

Y1 = f1 v…v f5;

Y2 = f6 v…v f10;

Y3 = f11 v…v f14.

Y = Y1 v Y2 v Y3.

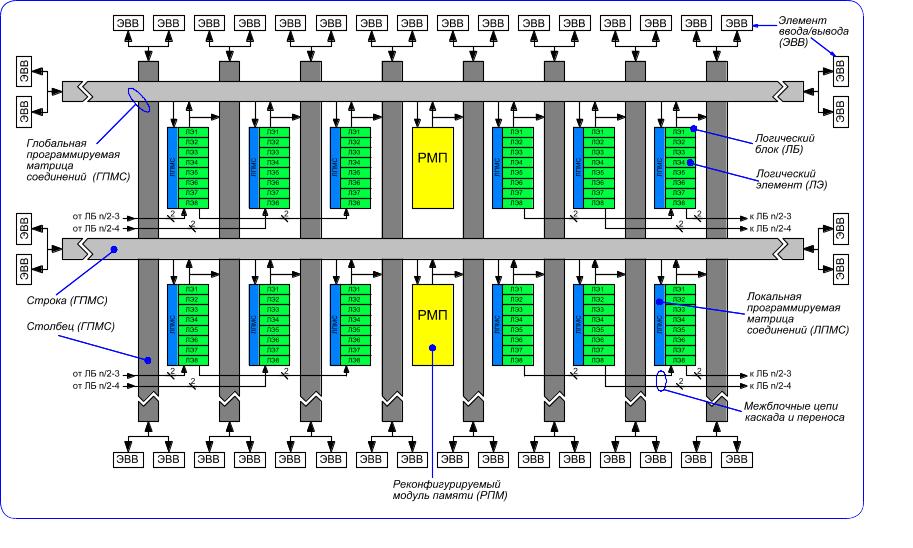

Вопрос 9 - Семейство flex10k. Общая характеристика семейства. Структурная схема плис семейства flex10k. Назначение элементов структурной схемы.

Общая характеристика семейства FLEX10K:

Тип конфигурационной памяти: SRAM;

Объем конфигурирующих данных: (115 000 …1 172 000) бит

Комбинационная часть ЛЭ: табличный преобразователь (LUT);

Способы конфигурирования в составе системы (ISP):

Пассивная последовательная (последовательное ПЗУ, ByteBlaster, BiteBlaster, JTAG, микроконтроллер);

Пассивная параллельная синхронная (микроконтроллер);

Пассивная параллельная асинхронная (микроконтроллер);

Структура ПЛИС семейства FLEX10K: