- •1) Логические элементы. Таблицы соответствия, переключательные функции.

- •2) Кнф и днф переход от одной формы к другой

- •4) Карты Карно

- •5) Rs триггер на элементах и-не

- •6) Rs триггер на элементах или-не

- •7) Синхронный двухтактный rs – триггер

- •11) Регистры последовательный и параллельный

- •12) Трехразрядный последовательный регистр

- •13) Универсальный регистр

- •14) Суммирующий счетчик с последовательным переносом

- •15)Вычитающий счетчик с последовательным переносом

- •16) Трехразрядный реверсивный счетчик на 2-х тактном т-триггере

- •17) Счетчик со сквозным переносом

- •18) Кольцевой счетчик

- •19) Дешифраторы

- •20) Прямоугольный дешифратор.

- •21) Каскадный дешифратор.

- •22) Шифраторы

- •23) Сумматоры

- •24) Полусумматор

- •25) Мультиплесоры

- •26) Демультиплексоры

- •27) Зу эвм. Иерархическая структура памяти эвм

- •28) Зу с непосредственной адресацией

- •29) Сверхоперативное зу с непосредственной адресацией

- •30) Ассоциативное зу

- •31) Созу с ассоциативной адресацией

- •32) Комбинационное алу магистрального типа

- •33) Накапливающее алу

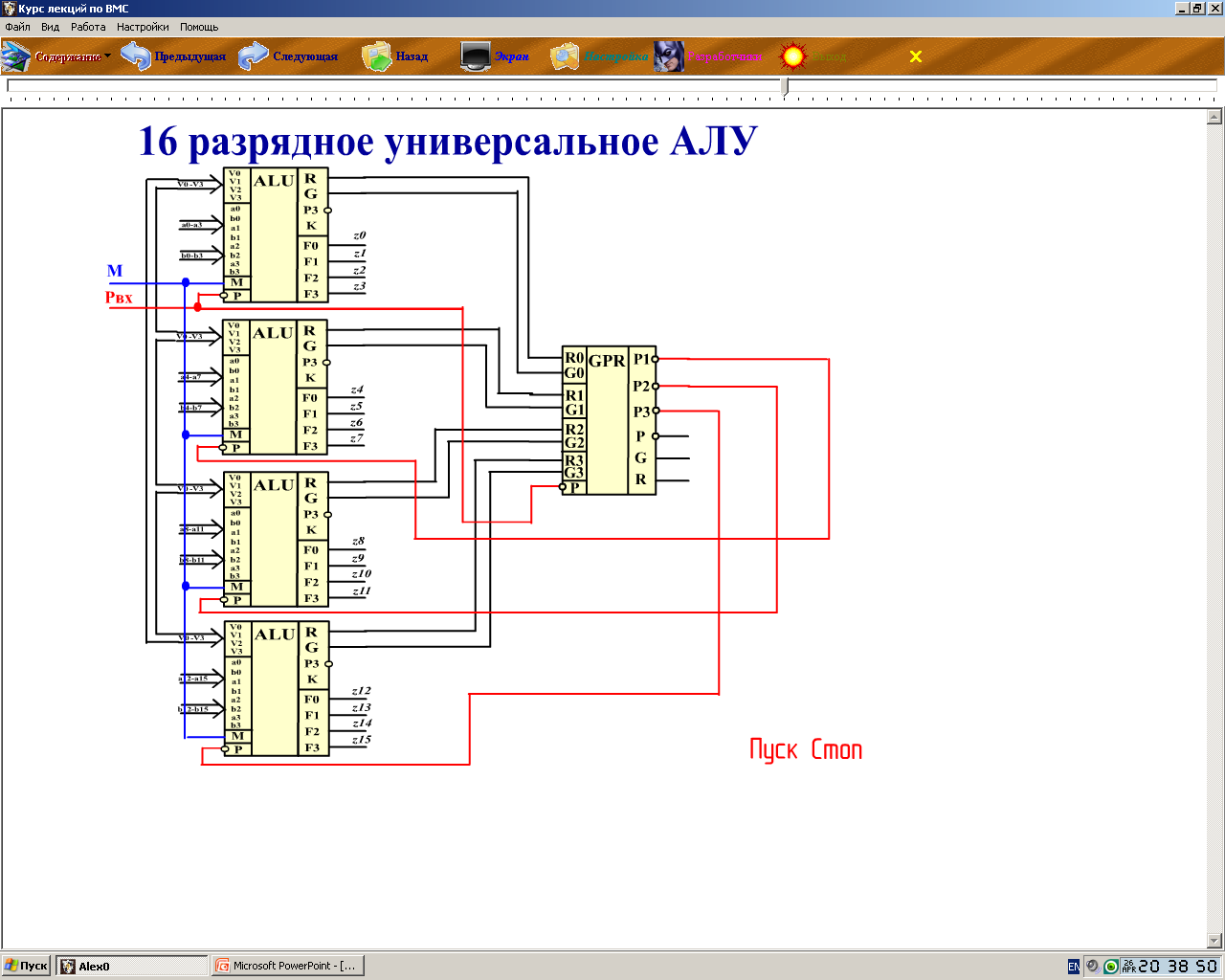

- •34)16-Разрядное универсальное алу

- •35) Алу для сложения чисел с фиксированной запятой

- •36) Алу для умножения чисел с фиксированной запятой.

- •37)Четыре способа умножения чисел с фиксированной запятой в алу

- •38) Центральное устройство управления процессором

- •39) Основные характеристики системы прерывания и диаграмма прерываний

- •40) Блок прерываний процессора

- •41) Блок синхронизации процессора.

31) Созу с ассоциативной адресацией

А дрес

ячейки памяти, в которой хранится

исходная информация поступает на СхСР

(схемы сравнения) и РгА (регистр адреса).

дрес

ячейки памяти, в которой хранится

исходная информация поступает на СхСР

(схемы сравнения) и РгА (регистр адреса).

Адрес ячейки памяти является ассоциативным признаком в том случае если в каком либо регистре найдено искомое слово, и схема сравнения вырабатывает сигналы λi=1. В этом случае происходит либо запись либо считывание информации из соответствующего информационно регистра.

При каждом РгИ (регистре информации) существует РгА и СхСР.

БР СОЗУ – блок разгрузки СОЗУ, он анализирует к какому регистру больше всего не велось обращение, и позволяет очищать соответствующий регистр информации, и соответственно регистр адреса.

32) Комбинационное алу магистрального типа

В данном АЛУ можно четко выделить три

основные точки. Две точки подключения

к шине данных и одна точка подключения

к выходной шине.

данном АЛУ можно четко выделить три

основные точки. Две точки подключения

к шине данных и одна точка подключения

к выходной шине.

РезШУ – результат шины Y

Оп 1, оп 2 – операнд 1, операнд 2

АЛУ содержит:

ПС – преобразователь сигнала (преобразует прямой код в обратный)

Д – дизъюнктор

К – конъюнктур

М2 – схема сложения по модулю два

Для реализации операции вычитания в СМ (сумматоре) оп1 принимает инверсное значение, сам СМ служит для сложения или вычитания оп1 и оп2

СФР – схема формирования результата

На основании входных сигналов схема формирует результат обработки оп1 и ип2, и выдает результат Мишина вывода.

СФПР – схема формирования признака результата. Формирует банарный код по которому можно судить о признаке результата обработки данных (четыре признака: >0, <0, =0, переполнение разрядной сетки).

Недостаток данного АЛУ: поскольку данная схема не содержит элементов памяти, в нем не производятся длинные операции (*, и /)

33) Накапливающее алу

Р ассмотрим

структурную схему оп1 и оп2 подаются

последовательно и запоминаются в

аккумуляторе (АК), затем данные операнды

поступают в блок логических операций

(БЛОП), где производится сложение и

вычитание данных операндов. Затем

результат поступает в буферный регистр

(БР) либо обратно в АК. После обработки

информации результат поступает на

выходную шину.

ассмотрим

структурную схему оп1 и оп2 подаются

последовательно и запоминаются в

аккумуляторе (АК), затем данные операнды

поступают в блок логических операций

(БЛОП), где производится сложение и

вычитание данных операндов. Затем

результат поступает в буферный регистр

(БР) либо обратно в АК. После обработки

информации результат поступает на

выходную шину.

В данных АЛУ могут выполняться операции * и /, т.к. буферный регистр является ячейкой памяти. АК в данной схеме служит для хранения сомножителя или делителя.

34)16-Разрядное универсальное алу

Входы:

V0 – V3 – управляющие диоды;

а0 – а3 – информационный вход 1-го слагаемого;

b0 – b3 – информационный вход 2-го слагаемого;

М – режим работы АЛУ, если М=1 выполняется логическая операция, если М≠0 – а-л операция.

Выходы:

R – сигнал распространения переноса;

G – выход генерации переноса;

PЗ – выход переноса старший разряд;

K – результат сравнения кодов чисел;

F0 – F3 – результат операций.

35) Алу для сложения чисел с фиксированной запятой

z 0

– знаковый разряд. Если z0=0, то результат

положительный, если z0=1, результат

отрицательный.

0

– знаковый разряд. Если z0=0, то результат

положительный, если z0=1, результат

отрицательный.

р0 – знак переноса. Наличие переноса из знакового разряда.

z0…zn-1 – значение знаковых разрядов.

Под влиянием ОС1 происходит запись 1-го операнда в РгА (регистр А).

Под действием ОС2 происходит запись 2-го операнда в Рг1 (буферный регистр 1). В этом случае если осуществляется операция сложения, то вырабатывается УС3 и операнд 2 поступает в РгВ (регистр В) в прямом коде, т.е. является слагаемым. Если реализуется операция вычитания, то операнд 2 поступает в РгВ в обратном коде под действием УС4.

После сложения или вычитания двух операндов в СМ (сумматоре) под действием УС5 СФПР вырабатывает сигналы α0 или α1:

Если α0=0, α1=0 – результат равен 0-ю.

Если α0=0, α1=1 – результат отрицательный.

Если α0=1, α1=0 – результат положительный.

Если α0=1, α1=1 – переполнение разрядной сетки, и в этом случае по действием сигнала УС6 происходит запись результата в РгΣ (регистр суммы). Далее под действием УС7 разрешается передача сигнала на выходную шину.

Формула для определения признака положительного числа в СФПР:

- переполнение

- переполнение

(или равно 0-ю)

(или равно 0-ю)