- •1. Структура многоуровневой системы управления. Решаемые задачи и требования к системе.

- •2. Структура и устройства управляющей микропроцессорной системы. Способы аналоговой обработки данных.

- •4. Схемы сопряжения устройств озу, пзу и портов ввода/вывода с шинами системной магистрали. Управление доступом к устройствам мп-системы:

- •5. Применение дешифраторов, ппзу и плм в схемах выборки устройств мп-системы.

- •6. Структура и интерфейс 8-разрядного микропроцессора.

- •7. Цикл выполнения команды 8-разрядного микропроцессора.

- •8. Диаграмма машинного цикла 8-разрядного микропроцессора. Типы машинных циклов, используемых при выполнении команд. Диаграмма цикла микроконтроллера mcs-51.

- •9. Системный контроллер мп – системы и системные сигналы управления.

- •10. Программистские модели 8-разрядных микропроцессоров (ресурсы, способы представления данных и виды адресации, слово состояния программы). Работа со стеком.

- •11. Структура и интерфейс микроконтроллеров с архитектурой cisc (на примере mcs-51).

- •12. Логическая организация памяти микроконтроллера mcs-51.

- •13. Характеристика системы команд микроконтроллера мcs-51. Слово состояния программы, типы данных, способы адресации. Организация ветвлений в программах.

- •14. Состав и назначение регистров специальных функций в микроконтроллерах.

- •16. Организация адресного пространства микроконтроллеров avr, способы адресации памяти программ и памяти данных.

- •18. Операции умножения/деления двоичных чисел.

- •Программная процедура деления:

- •19. Арифметическая обработка многобайтных операндов в микропроцессорах и микроконтроллерах с 8 – разрядной архитектурой.

- •20. Сложение-вычитание многобайтных 2-10 чисел в 8-разрядных микропроцессорах и микроконтроллерах.

- •19. Программная реализация временной задержки с заданным временем (задача). Расчетные зависимости.

- •21. Логическая обработка данных в микроконтроллерах. Битовые операции. Вычисление логической функции, аргументы которой поступают по входным линиям порта (задача).

- •22. Порты параллельного синхронного ввода-вывода мп систем. Программирование ввода-вывода.

- •23. Схемы портов параллельного асинхронного ввода-вывода мп – систем.

- •24. Структурная схема параллельного программируемого интерфейса. Основные режимы работы.

- •25. Организация ввода-вывода данных по запросам прерываний от схемы программируемого параллельного интерфейса.

- •26. Схемы и принципы работы двунаправленного (p0) и квазидвунаправленных портов (p1, p2, p3) микроконтроллеров mcs-51.

- •27. Режимы работы портов ввода-вывода микроконтроллеров avr.

- •28. Параллельный обмен данными с внешними устройствами в микроконтроллерных системах. Обмен с квитированием.

- •29. Схема, основные режимы работы и программирование таймера микроконтроллера mcs51.

- •30. Применение таймеров mcs51 для отсчета времени, измерения длительности сигнала, подсчета событий, формирования периодических сигналов.

- •1. Подсчет числа импульсов, поступающих на вход мк51 за 10мс.

- •2. Измерение длительности сигнала, поступающего на вход .

- •3. Организовать временную задержку длительность 500мс

- •4. Формирование пер. Сиг. (100мкс

- •31. Таймеры микроконтроллеров avr. Использование таймеров для сравнения, захвата событий, формирования шим-сигналов, в сторожевом режиме.

- •32. Основные функции системы прерываний.

- •33. Способы программной и аппаратной идентификация запроса прерываний в одноуровневых и многоуровневых системах прерываний.

- •34. Механизм обработки векторных прерываний в мп-системах с помощью команд rst n и call addr.

- •35. Контроллер прерываний. Структура, интерфейс, способы обработки прерываний.

- •36. Построение системы прерываний с несколькими контроллерами. Идентификация запроса прерываний.

- •37. Программирование контроллера прерываний. Назначение управляющих слов при инициализации контроллера и во время работы.

- •38. Система прерываний микроконтроллера mcs51. Работа со стеком.

- •39. Структура и основные режимы работы канала последовательного ввода-вывода uart микроконтроллера mcs-51.

- •40. Программирование приёма/передачи данных по каналу uart между двумя микроконтроллерами.

- •41. Организация обмена данными между микроконтроллерами при работе в сети.

- •43. Схема интерфейса микроконтроллера mcs-51 с внешней памятью программ, внешней памятью данных и дополнительными портами ввода-вывода.

- •42. Интерфейсы последовательной связи i2c. Программная и аппаратная реализация в микроконтроллерах avr.

- •44. Взаимодействие микроконтроллера с клавиатурой,дисплеем

- •45. Устройства энергонезависимой памяти с последовательным интерфейсом (на примере at25, at45).

- •47. Применение ацп и цап в мп-системах.

- •46. Память DataFlash -структура, операции, применение.

18. Операции умножения/деления двоичных чисел.

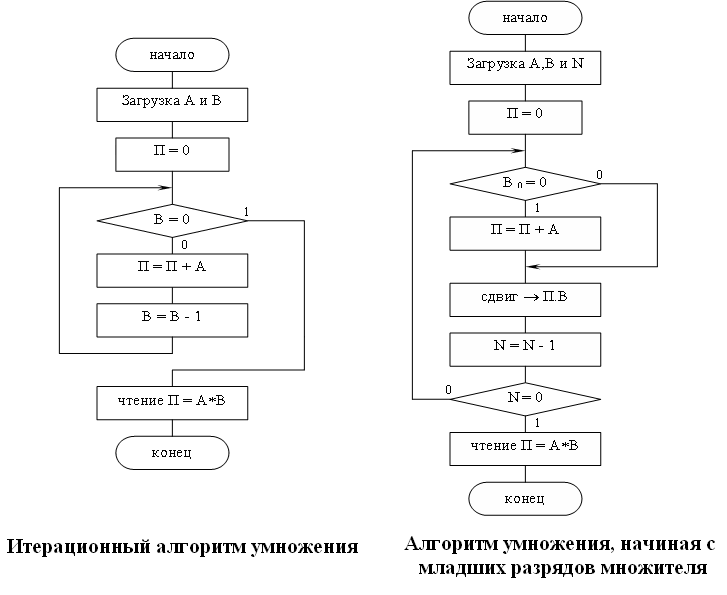

Итерационный алгоритм умножения.

После загрузки множимого А и множителя В в регистры общего назначения и обнуления регистра произведения П производится анализ содержимого регистра множителя. Если В ¹ 0, то к сумме частичных произведений П прибавляется множимое А. Затем содержимое регистра множителя уменьшается на 1 и цикл умножения повторяется до тех пор, пока содержимое регистра множителя не окажется равным 0. При умножении n – разрядных сомножителей 2n – разрядное произведение размещают в двух регистрах. Данный метод умножения находит ограниченное применение в сравнительно несложных микропроцессорных системах.

Алгоритм умножения, начиная с младших разрядов множителя. Этот алгоритм может быть использован для получения произведения двух двоичных чисел без знака. Количество итераций умножения N определяется числом разрядов множителя. Поскольку в процессе умножения на каждой итерации осуществляется сдвиг множителя В на 1 разряд вправо, на место освобождаемых разрядов можно записать выталкиваемые при сдвиге вправо разряды произведения П. При использовании n – разрядного сумматора или АЛУ исходные двоичные числа без знака не должны выходить за пределы диапазона от 1 до 2(n-1) -1.

Деление двоичных чисел.

X – 16-ти разрядное делимое (XH, XL)

Y – 8-ми разрядный делитель

Z – 8-ми разрядное частное

При выполнении делении необходимо исключить возможность деления на 0. Если для представления частного потребуется более одного слова, то возникает переполнение. Поэтому перед выполнением деления необходимо проверить условие – делитель должен быть больше старшего байта делимого.

Алгоритм деления по методу итераций с восстановлением остатка.

Пример:

X=19; y=4.

X=00010011

Y=0100

Программная процедура деления:

AL REG R3

AH REGR4

MOV R2,#8; счетчик циклов

MOV AL,#DATA; делимое

MOV AH,#DATA

MOV B, #DATA; делитель

CLR C; обнулим флаг заёма

MOV A, AH

SUBB A,B

JZ OV_DIV; AH=B

JNC OV_DIV; AH>B

LOOP:

CLR C

RLC A

MOV AL,A; сдвиг

MOV A,AH; делимого

RLCA

MOV AH,A

SUBB A,B

MOV AH,A

JNC digC1; переход на занесение 1 в Сi

ADD A,B; восстановление

MOV AH,A

JMP M1

Digc1: ORL AL,#1

M1: DJNZ R2, LOOP

;вывод результата

OV_DIV:…; вывод сообщения о переполнении

19. Арифметическая обработка многобайтных операндов в микропроцессорах и микроконтроллерах с 8 – разрядной архитектурой.

16 разрядные числа A и B: AH AL , BH, BL

AL+BL=>CL; С- флаг переноса

AH+BH+CL=>CH

Вычитание

A=0001 0011 0000 00012 = 130116

B=0000 0101 0000 00112 = 050316

1. AL-BL

00000001

11111101

111111102 = [-0316]доп. C=1

2. AH-BH

00010011

11111010* - последний разряд не 1 из-за заёма

00001101 = [0D16]

Программная процедура сложения/вычитания:

Addr_A EQU 10h

Addr_B EQU 20h

MOV R2, #2 ;обработка 2-х байтов

MOV R0, #Addr_A

MOV R1, #Addr_B

CLR C

loop: MOV A, @R0

ADD A, @R1 ; SUB для вычитания, ADDC и SUBB для ДД чисел

MOV @R0, A

inc R0

inc R1

DJNZ R2, loop

20. Сложение-вычитание многобайтных 2-10 чисел в 8-разрядных микропроцессорах и микроконтроллерах.

Сложение многобайтных 2-10 чисел.

1) Складываем L-байты;

2) Коррекция. (DDA – коррекция содержимого аккумулятора после сложения).

3) Складываем H-байты + возможный перенос (ADC);

4) Коррекция.

Алгоритм коррекции состоит из двух шагов:

а) Если AС = 1 (дополнительный перенос между тетрадами), или младшая тетрада больше 9, но меньше 15, то к ней прибавляется код 6. Возникающий перенос прибавляется к старшей тетраде;

б) Если C = 1, или старшая тетрада содержит недопустимую комбинацию, то к результирующему байту прибавляется код 60h.

Пример: 2985 + 4936 = 7921

1) 10000101

00110110

10111011

2) 10111011

0110

11000001

0110

00100001

\ 2 / \ 1 /

3) 00101001

01001001

1 (перенос)

01110011

4) 01110011

0110

11000001

0110

00100001

\ 7 / \ 9 /

Вычитание многобайтных 2-10 чисел.

1) Вычитаемое заменяем дополнительным кодом.

2) Добавляем уменьшаемое.

3) Проводи коррекцию.

4) Повтор шагов 1-3 для всех байтов 2-10 чисел.

(-35) доп = 65 – дополнение до десятки.

Пример 1. 0493 – 0298 = 0195

99 + 1 9A +68 02 - дополнение до BL +93 95

|

99 +FE 97 +04 9B +06 - коррекция A1 +60 101 |

этот перенос указывает на то, что получен результат в прямом коде.

Пример 2. 0298 – 0493 = 9805

99 + 1 9A +60 07 - дополнение до BL +98 9F +06 A5 +60 05 |

99 + 1 9A +FC 96 +02 98

нет переноса - значит результат получен в дополнительном коде

|

Программная процедура вычитания ДД чисел

addr_A EQU 10h

addr_B EQU 20h

mov R2,#2; число повторений

mov R0,#addr_A

mov R1,#addr_B

setb C; перенос - 1

loop: mov A,#99h

addc A,#0

subb A,@R1

add A,@r0; + 1-ый операнд

DA A ; коррекция

mov @R0,A; сохраняем результат вместо 1го операнда

inc R0

inc R1

djnz R2,loop