- •1. Величины и способы формирования напряжений логических уровней. Высокоимпедансное состояние выхода.

- •2. Вычитание чисел в обратном и дополнительном кодах.

- •3. Вычитатель, работающий в дополнительном коде.

- •4. Вычитатель, работающий в обратном коде.

- •5. Иерархия шин современных персональных компьютеров. Структура пэвм.

- •6. Конфигурируемая логическая матрица и-или.

- •7. Методы выбора микропроцессоров

- •8. Многовходовой элемент логического умножения: схема монтажного «и»

- •9. Обмен по магистрали с мультиплексированной шиной адрес/данные.

- •10. Обмен по магистрали с разделенными шинами адрес/данные

- •12. Параллельный сумматор.

- •13. Полувычитатель и вычитатель

- •14. Полусумматоры и сумматоры

- •15. Понятие макроячейки программируемых логических интегральный схем.

- •17. Последовательный сумматор

- •18. Построение комбинационных схем по булевой функции, заданной таблицей истинности.

- •19. Правила перевода чисел из одной системы счисления в другую

- •20. Представление информации в эвм. Представление чисел в обратном и дополнительном коде. Числа с плавающей и фиксированной запятой.

- •21. Представление команд в эвм. Cisc, risc, нульоперандные процессоры.

- •22. Принципы фон Неймана.

- •23. Программируемые логические интегральные схемы: основные понятия.

- •24. Системы счисления. Их виды. Способы записи чисел.

- •25. Состав и назначение элементов процессора. Функции алу.

- •26. Способ построения двунаправленного буферного элемента.

- •27. Способ построения трехстабильного буферного элемента.

- •28. Способы табличного и модульного умножения.

- •29. Способы умножения чисел.

- •30. Табличные и модульные умножители.

- •31. Умножитель, использующий многократное сложение.

- •32. Умножитель, использующий операции сложения и сдвига.

- •33. Универсальный сумматор-вычитатель, работающий в дополнительном коде.

- •3 4. Условные графические обозначения микросхем.

- •35. Физические принципы построения вычислительных машин. Классификация эвм.

- •36. Элементы алгебры логики. Законы булевой алгебры.

- •37. Элементы микропроцессорных систем: постоянная и оперативная память.

- •38. Элементы микропроцессорных систем: регистры, дешифраторы, шифраторы.

- •39. Элементы микропроцессорных систем: счетчики, мультиплексоры.

- •40. Элементы микропроцессорных систем: триггеры и регистры.

- •41. Этапы развития вычислительной техники, поколения и перспективы развития эвм.

- •42. Физические принципы построения вычислительных машин.

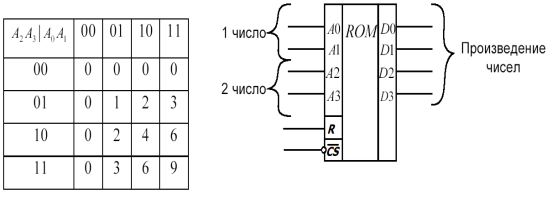

30. Табличные и модульные умножители.

В качестве ядра табличного умножителя используется постоянное запоминающее устройство (ПЗУ). В него записывается таблица Пифагора, причем номер строки и столбца подается параллельно на адресные входы ПЗУ.

При умножении двух чисел n и m разрядности результат произведения имеет разрядность n+m

16 вариантов входных данных

Преимущества: 1) умножение производится максимально быстро 2) простота схемотехнической реализации

Недостаток:

1) неприемлем для умножения многоразрядных чисел, например для умножения двух 16рахрядных чисел V такой ПЗУ будет 16Гб.

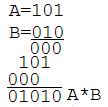

A= B= A*B=

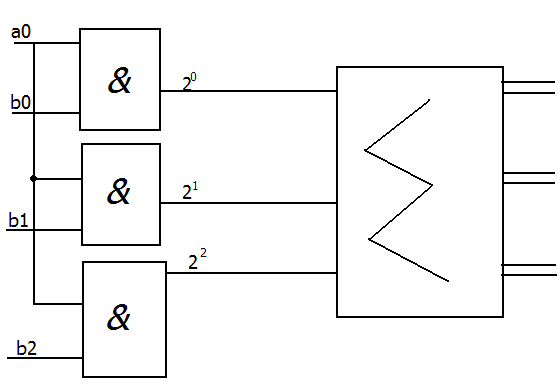

При аппаратной реализации данной функции произведение двух разрядов ai и bk может быть осуществлено с помощью логического умножения.

Результаты умножения подаются на специальный сумматор, входы которого определяются весом и плюс k.

Р азряды

имеющие один и тот же вес i+k

подаются на один многоразрядный вход

сумматора.

азряды

имеющие один и тот же вес i+k

подаются на один многоразрядный вход

сумматора.

Преимущества:

1) умножение выполняется за один такт (состоит из 2 комбинационных схем)

2) высокая скорость работы которая следует из того,что умножение выполняется за один такт

Недостаток:

1) аппаратные средства незначительно выше, чем у предыдущих схем.

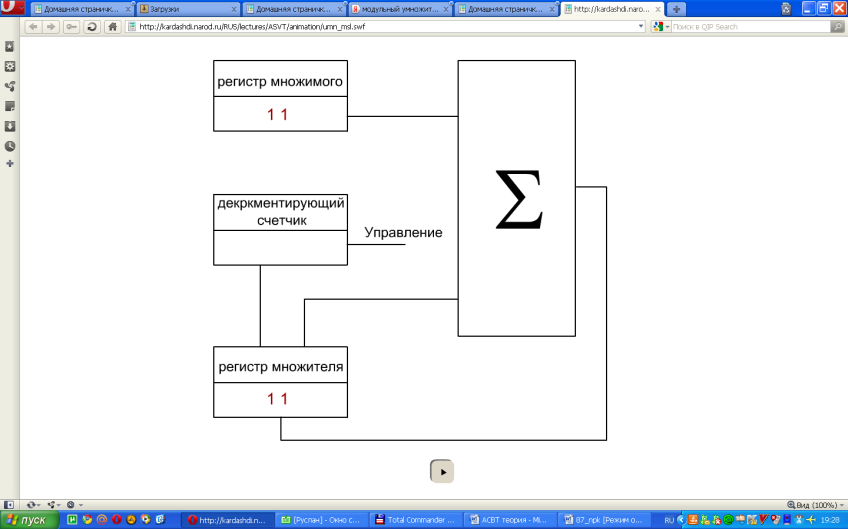

31. Умножитель, использующий многократное сложение.

Данный метод основан на следующей формуле:

С=A*B=

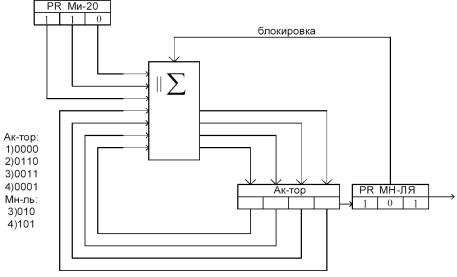

32. Умножитель, использующий операции сложения и сдвига.

![]()

PM- регистр множимого

PMn- регистр множителя

A- аккумулятор (временный регистр)

Аккумулятор сохраняет как временную сумму, так и перенос от текущего шага сложения. Суммарная разрядность аккумулятора и регистра множителя равна разрядности результата плюс бит переноса.

Аккумулятор- дополнительный регистр, который выполняет хранение промежуточной суммы.

Результат находится в аккумуляторе и регистре множителя.

Преимущества:

1) сравнительная простота схемотехнической реализации в зависимости от разрядности чисел

Недостаток:

1) умножение происходит за количество тактов, определенное разрядностью множителя.

Алгоритм работы:

1) регистр аккумулятора обнуляется, множимое и множители заносятся в соответственный регистр.

2) анализируем младший разряд множителя. Если он равен 1, то выполняем сложение.

3) регистры аккумулятора и множителя сдвигаются на 1 разряд вправо.

4) если не произведено количество сдвигов, равное разрядности операндов, перенос на шаг 2, иначе конец алгоритма.

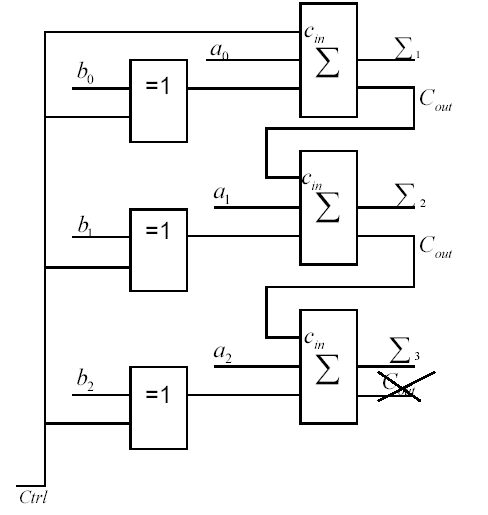

33. Универсальный сумматор-вычитатель, работающий в дополнительном коде.