- •1. Величины и способы формирования напряжений логических уровней. Высокоимпедансное состояние выхода.

- •2. Вычитание чисел в обратном и дополнительном кодах.

- •3. Вычитатель, работающий в дополнительном коде.

- •4. Вычитатель, работающий в обратном коде.

- •5. Иерархия шин современных персональных компьютеров. Структура пэвм.

- •6. Конфигурируемая логическая матрица и-или.

- •7. Методы выбора микропроцессоров

- •8. Многовходовой элемент логического умножения: схема монтажного «и»

- •9. Обмен по магистрали с мультиплексированной шиной адрес/данные.

- •10. Обмен по магистрали с разделенными шинами адрес/данные

- •12. Параллельный сумматор.

- •13. Полувычитатель и вычитатель

- •14. Полусумматоры и сумматоры

- •15. Понятие макроячейки программируемых логических интегральный схем.

- •17. Последовательный сумматор

- •18. Построение комбинационных схем по булевой функции, заданной таблицей истинности.

- •19. Правила перевода чисел из одной системы счисления в другую

- •20. Представление информации в эвм. Представление чисел в обратном и дополнительном коде. Числа с плавающей и фиксированной запятой.

- •21. Представление команд в эвм. Cisc, risc, нульоперандные процессоры.

- •22. Принципы фон Неймана.

- •23. Программируемые логические интегральные схемы: основные понятия.

- •24. Системы счисления. Их виды. Способы записи чисел.

- •25. Состав и назначение элементов процессора. Функции алу.

- •26. Способ построения двунаправленного буферного элемента.

- •27. Способ построения трехстабильного буферного элемента.

- •28. Способы табличного и модульного умножения.

- •29. Способы умножения чисел.

- •30. Табличные и модульные умножители.

- •31. Умножитель, использующий многократное сложение.

- •32. Умножитель, использующий операции сложения и сдвига.

- •33. Универсальный сумматор-вычитатель, работающий в дополнительном коде.

- •3 4. Условные графические обозначения микросхем.

- •35. Физические принципы построения вычислительных машин. Классификация эвм.

- •36. Элементы алгебры логики. Законы булевой алгебры.

- •37. Элементы микропроцессорных систем: постоянная и оперативная память.

- •38. Элементы микропроцессорных систем: регистры, дешифраторы, шифраторы.

- •39. Элементы микропроцессорных систем: счетчики, мультиплексоры.

- •40. Элементы микропроцессорных систем: триггеры и регистры.

- •41. Этапы развития вычислительной техники, поколения и перспективы развития эвм.

- •42. Физические принципы построения вычислительных машин.

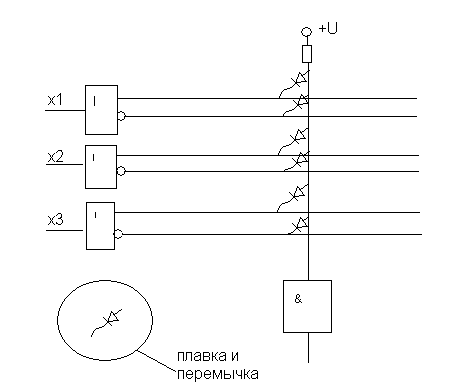

8. Многовходовой элемент логического умножения: схема монтажного «и»

9. Обмен по магистрали с мультиплексированной шиной адрес/данные.

Шаг 1. Процессор переводит ШАД в режим выдачи информации

Шаг 2. Процессор выдает на ШАД адрес внешнего устройства

Шаг 3. Процессор выдает сигнал готовности адреса

Шаг 4. Внешнее устройство, получив сигнал готовности адреса, записывает в следующ. регистр значение адреса

Шаг 5. Процессор снимает сигнал готовности адреса

Шаг 6. Процессор убирает адрес ШАД

Шаг 7. Процессор переводит ШАД либо в режим чтения, либо в режим записи в зависимости от того, какую процедуру проц. выполняет

Шаг 8. Процессор выдает сигнал чтения или записи

10. Обмен по магистрали с разделенными шинами адрес/данные

Алгоритм работы магистралей (чтение).

Процессор выставляет на ША адрес.

Процессор выдает сигнал готовности адреса ALE.

Процессор переводит линии данных в режим ввода.

Процессор выдает сигнал чтение; выдает сигнал- значит, что линия становится активной, переводит линию в активное состояние.

Процессор ожидает активного уровня сигнала на линии готовности.

После получения сигнала готовности процессор считывает данные с шины данных.

Процессор переводит в неактивное состояние сигнал готовности адреса, сигнал чтения и в 3 состояние шины адреса и данных

Алгоритм работы магистралей (запись).

Процессор выдает адрес

Выдает сигнал готовности адреса

Переводит шину данных в режим выдачи информации

Выдает на шину данных записываемое число

Процессор выдает сигнал записи

Процессор ожидает сигнала готовности

Процессор приводит в неактивное состояние готовность адреса, сигнал записи и в 3 состояние шину адреса и данных.

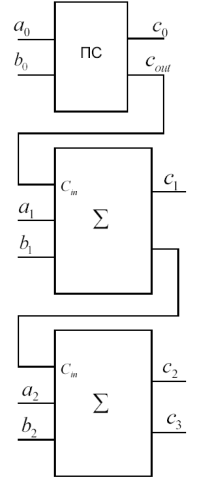

12. Параллельный сумматор.

Предназначен для сложения двух n-разрядных чисел. Схема данного сумматора состоит из линейки сумматоров, причем младший из них- полусумматор, а старшие- полные сумматоры. Результат работы этой схемы- n-разрядное число плюс бит переноса или переполнение из старшего разряда слагаемых.

Работу данного сумматора можно продемонстрировать на схеме трехразрядного параллельного сумматора:

а0 , b0 –младшие разряды числа

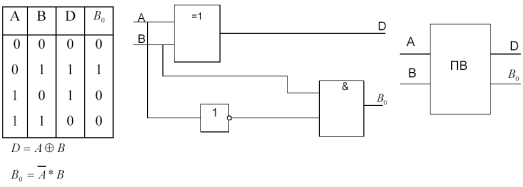

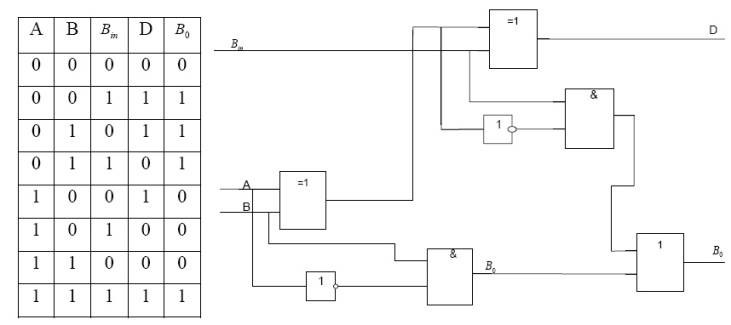

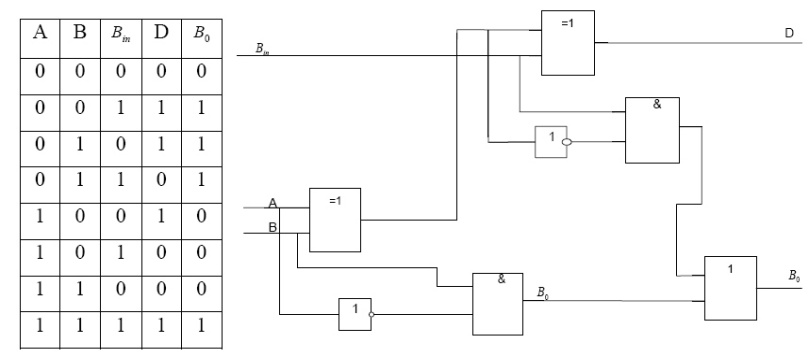

13. Полувычитатель и вычитатель

Структура полувычитателя:

Полный вычитатель:

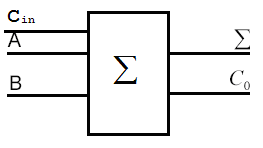

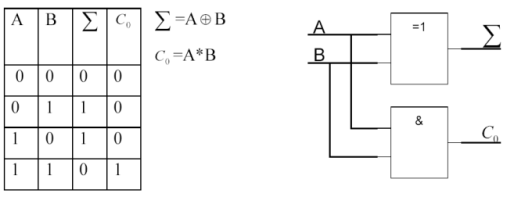

14. Полусумматоры и сумматоры

Полусумматор предназначен для сложения двух одноразрядных чисел. Результатами сложения являются двоичный разряд результата и разряд переноса, следующий значащий бит. Полусумматор работает в соответствии со следующей таблицей истинности:

На функциональных схемах данную схему будем обозначать:

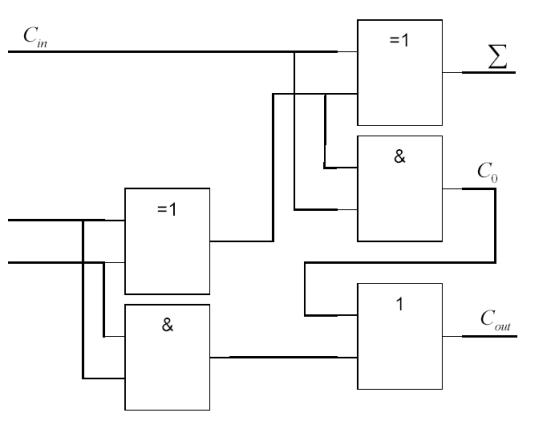

П олный

сумматор.

олный

сумматор.

Этот блок выполняет функцию сложения двух одноразрядных чисел с учетом входящего переноса из младшего значащего разряда. В качестве выходов можно указать те же выходы, что и в полусумматоре.

Полный сумматор строится на основании следующей таблицы истинности:

Полный сумматор на функциональных схемах обозначается: