- •Определение микропроцессора. Общие сведения о микропроцессорных системах. Классификация микропроцессоров.

- •Risc и cisc-архитектуры процессоров. Преимущества и недостатки. Примеры современных процессоров с risc и cisc-архитектурой.

- •Укрупненная структурная схема элементарной микропроцессорной системы. Назначение основных функциональных узлов.

- •Функции процессора. Системная магистраль, назначение шин. Схема подключения процессора, основные выводы микросхемы процессора.

- •Внутренняя структура микропроцессора. Схема управления выборкой команд, алу, регистры процессора, схема управления прерываниями, схема управления прямым доступом к памяти, логика управления.

- •Характеристики систем памяти микропроцессорных систем, методы доступа к памяти.

- •Многоуровневая иерархическая архитектура памяти: описание каждого уровня. Основная память.

- •Увеличение разрядности микросхем памяти. Структура памяти на основе блочной схемы.

- •Расслоение памяти. Блочная память с чередованием адресов по циклической схеме. Блочно-циклическая схема расслоения памяти.

- •Режимы доступа к памяти: последовательный, конвейерный, регистровый; страничный; пакетный, удвоенной скорости.

- •Статическая и динамическая оперативная память, классификация. Основные функциональные характеристики.

- •Однопортовые и многопортовые запоминающие устройства. Структура двухпортовых оперативных запоминающих устройств.

- •Постоянная память. Память программ для микроконтроллеров. Микросхемы постоянной памяти.

- •Ассоциативная память. Структура ассоциативного запоминающего устройства. Классификация.

- •Организация кэш-памяти. Структура микропроцессорной системы с основной и кэш-памятью. Параметры кэш-памяти.

- •Способы отображения основной памяти на кэш-память: прямое, полностью ассоциативное, частично-ассоциативное отображение. Структурные схемы, сравнительная характеристика.

- •17 Микроконтроллеры, классификация, структурные схемы. Принстонская и Гарвардская архитектуры. Преимущества и недостатки.

- •Типы памяти микроконтроллеров. Память программ, память данных, внешняя память, регистры мк, стек.

- •Система питания микроконтроллеров, понятие собственной мощности. Система тактирования и синхронизации микроконтроллеров, виды, преимущества и недостатки.

- •Отличительные признаки современных 8-разрядных микроконтроллеров. Модульная организация мк. Структура процессорного ядра мк и изменяемого функционального блока.

- •Организация связи мк с внешней средой и временем. Порты ввода-вывода. Типовая схема двунаправленного порта ввода-вывода.

- •Микроконтроллер 8051, его место в современном производстве микроконтроллеров. Базовая архитектура процессора. Назначение основных регистров. Регистры специальных функций. Регистр флагов.

- •Микроконтроллер 8051: организация памяти программ и памяти данных. Способы адресации. Устройство управления и синхронизации.

- •Организация портов ввода-вывода микроконтроллера 8051. Устройство портов. Альтернативные функции портов.

- •Таймеры-счетчики микроконтроллеров семейства 8051: регистр режима работы, регистр управления-статуса. Режимы работы таймеров-счетчиков.

- •. Организация прерываний микроконтроллера 8051. Регистры прерываний.

- •Система команд микроконтроллера 8051. Способы адресации.

- •Средства и системы разработки микроконтроллеров.

- •29. Системы ввода/вывода (свв). Способы подключения свв к процессору, их достоинства и недостатки.

- •30. Организация адресного пространства системы ввода/вывода. Совмещенное и выделенное адресное пространство, достоинства и недостатки. Адресное пространство системы ввода/вывода

- •31. Категории и структура внешних устройств. Внешние устройства

- •32. Модули ввода-вывода. Функции модуля ввода-вывода. Модули ввода/вывода Функции модуля

- •33. Структура модуля ввода-вывода, описание регистров (привести схему).

- •34. Методы управления вводом-выводом: программно управляемый ввод/вывод. Программно управляемый ввод/вывод

- •35. Методы управления вводом-выводом: ввод/вывод по прерываниям. Ввод/вывод по прерываниям

- •36. Методы управления вводом-выводом: прямой доступ к памяти. Прямой доступ к памяти

Организация связи мк с внешней средой и временем. Порты ввода-вывода. Типовая схема двунаправленного порта ввода-вывода.

Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в многоразрядные (чаще 8-разрядные) параллельные порты ввода/вывода. В памяти МК каждому порту ввода/вывода соответствует свой адрес регистра данных. Обращение к регистру данных порта ввода/вывода производится теми же командами, что и обращение к памяти данных. Кроме того, во многих МК отдельные разряды портов могут быть опрошены или установлены командами битового процессора.

В зависимости от реализуемых функций различают следующие типы параллельных портов:

однонаправленные порты, предназначенные только для ввода или только для вывода информации;

двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации МК;

порты с альтернативной функцией (мультиплексированные порты). Отдельные линии этих портов используются совместно со встроенными периферийными устройствами МК, такими как таймеры, АЦП, контроллеры последовательных интерфейсов;

порты с программно управляемой схемотехникой входного/выходного буфера.

Порты выполняют роль устройств временного согласования функционирования МК и объекта управления, которые в общем случае работают асинхронно. Различают три типа алгоритмов обмена информацией между МК и внешним устройством через параллельные порты ввода/вывода:

режим простого программного ввода/вывода;

режим ввода/вывода со стробированием;

режим ввода/вывода с полным набором сигналов подтверждения обмена.

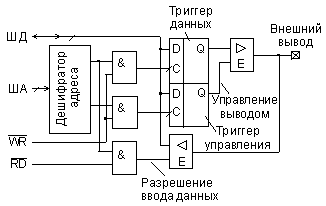

Типичная схема двунаправленного порта ввода/вывода МК приведена на рис. 4.4.

Рис. 4.4. Типовая схема двунаправленного порта ввода/вывода МК.

Триггер управления разрешает вывод данных на внешний вывод. В современных МК, как правило, обеспечивается индивидуальный доступ к триггерам данных и управления, что позволяет использовать каждую линию независимо в режимеввода или вывода.

Необходимо обратить особое внимание на то, что при вводе данных считывается значение сигнала, поступающее на внешний вывод, а не содержимое триггера данных. Если к внешнему выводу МК подключены выходы других устройств, то они могут установить свой уровень выходного сигнала, который и будет считан вместо ожидаемого значения триггера данных.

Другим распространенным вариантом схемотехнической организации порта ввода/вывода является вывод с "открытым истоком", называемый еще "квазидвунаправленным". Такая организация вывода позволяет создавать шины с объединением устройств по схеме "монтажное И".

Микроконтроллер 8051, его место в современном производстве микроконтроллеров. Базовая архитектура процессора. Назначение основных регистров. Регистры специальных функций. Регистр флагов.

Несмотря на непрерывное развитие и появление все новых и новых 16- и 32-разрядных МК, наибольшая доля мирового микропроцессорного рынка остается за 8-разрядными устройствами. В 2002 году общий мировой объем продаж МК всех типов составил $ 15,4 млрд., при этом 48,6% пришлось на долю 8-разрядных кристаллов. Это в 2,5 раза больше объема продаж ближайших конкурентов: 16-разрядных МК ($ 2,1 млрд.) и DSP ($ 2,4 млрд.). За последние пять лет лидирующее положение 8-разрядных МК на мировом рынке сохраняется.

Первые МК 8051 были выпущены Intel в 1980 г.

МК 8051 представляет сбой законченное устройство с большим объемом встроенной памяти программ и данных, портами ввода/вывода и возможностью подключения внешней памяти. Типовые характеристики:

- тактовая частота 24 МГц;

- командный цикл 12 тактов;

- объем памяти программ 4 Кб;

- объем памяти данных 128 байт;

- число линий ввода/вывода – 32;

- два 8/16-разрядных таймера;

- множество внутренних и внешних источников прерываний;

- программируемый последовательный порт;

- интерфейс с внешней памятью объемом до 128 Кб.

МК 8051 имеет Гарвардскую архитектуру, то есть память программ и память данных являются самостоятельными и независимыми друг от друга устройствами.

Регистры специальных функций управляют работой блоков, входящих в микроконтроллер. Регистры-защелки SFR параллельных портов P0...P3 - служат для ввода-вывода информации.

Две регистровые пары с именами TH0, TL0 и TH1, TL1 представляют собой регистры, двух программно-управляемых 16-битных таймеров-счетчиков. Режимы таймеров-счетчиков задаются с использованием регистра TMOD, а управление ими осуществляется с помощью регистра TCON. Для управления режимами энергопотребления МК используется регистр PCON. Регистры IP и IE управляют работой системы прерываний МК, регистры SBUF и SCON — работой приемопередатчика последовательного порта. Регистр-указатель стека SP в МК рассматриваемого семейства — восьмибитный.

Перечень флагов, их символические имена и условия формирования приведены в таблице 2.2.

Таблица 2.2 – Регистр флагов Intel 8051

Символ |

Позиция |

Имя и назначение |

P |

PSW.0 |

Флаг приоритета. Устанавливается и сбрасывается аппаратурно в каждом цикле команды и фиксирует нечетное/четное число единичных бит в аккумуляторе |

- |

PSW.1 |

Не используется |

OV |

PSW.2 |

Флаг переполнения. Устанавливается и сбрасывается аппаратурно при выполнении арифметических операций |

RS0 - RS1 |

PSW.3 - PSW.4 |

Биты выбора используемого банка регистров. Могут быть изменены программным путем |

F0 |

PSW.5 |

Флаг пользователя. Может быть установлен, сброшен или проверен программой пользователя |

АС |

PSW.6 |

Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратными средствами при выполнении команд сложения и вычитания и сигнализирует о переносе или заеме в бите 3 аккумулятора |

C |

PSW.7 |

Флаг переноса. Устанавливается и сбрасывается как аппаратурно, так и программным путем |