- •3.Реле тока.

- •4.Реле времени.

- •8.Аналоговые электронные устройства контроля перемещения, положения. Компаратор

- •5. Одновибратор.

- •6. Мультивибратор. Симметричный мультивибратор

- •7.Задатчик ускорения.

- •9. Дифференциальный усилитель.

- •8.Компаратор

- •1.Автоматика, определения, классификация, функции систем автоматики.

- •2. Операционный усилитель, характеристики

- •11.Инвертирующий и неинвертирующий усилители.

- •Неинвертирующий усилитель.

- •12.Цифровые элементы автоматики. Генераторы импульсов.

- •14.Триггеры.

- •16.Цифровые элементы автоматики. Rs – триггер.

- •17.Цифровые элементы автоматики. Двухступенчатый триггер.

- •18.Цифровые элементы автоматики. Jk – триггер.

- •19.Цифровые элементы автоматики. Регистры памяти.

- •20.Цифровые элементы автоматики. Регистры сдвига.

- •21.Цифровые элементы автоматики. Счетчики.

- •22. Цифровые элементы автоматики. Делители.

- •23. Цифровые элементы автоматики. Одновибратор

- •24. Цифровые элементы автоматики. Счетчики. 4-х разрядный счетчик последовательного типа.

- •26. Датчики изображения

- •27. Таймеры

- •28. Магниточувствительные датчики

- •29. Тактильные чувствительные элементы

- •30. Кнопочный переключатель

- •31. Емкостные сенсоры

- •32. Датчики температуры

- •33. Твердотельные реле

- •34. Цифровой задатчик интенсивности.

- •35. Устройство контроля подачи двойного листа

- •36. Электронные устройства защитного отключения

- •37. Устройства на основе светодиодов

- •38. Цифровой потенциометр

- •39. Оптронные элементы

- •40. Микропроцессоры в устройствах автоматики

- •41. Устройства измерения тока

- •42. Фотоэлектрический преобразователь перемещения

- •43. Интеллектуальные силовые модули

- •44. Преобразователи для электроприводов переменного тока. Инверторы напряжения.

- •45.Структурная схема и принцип действия автономного инвертора напряжения (аин).

- •46. Способы формирования выходного напряжения аин.

- •47. Полупроводниковый регулятор напряжения. Принцип параметрического регулирования напряжения.

- •48. Схемное решение регулятора напряжения.

- •49. Схема управления регулятором напряжения.

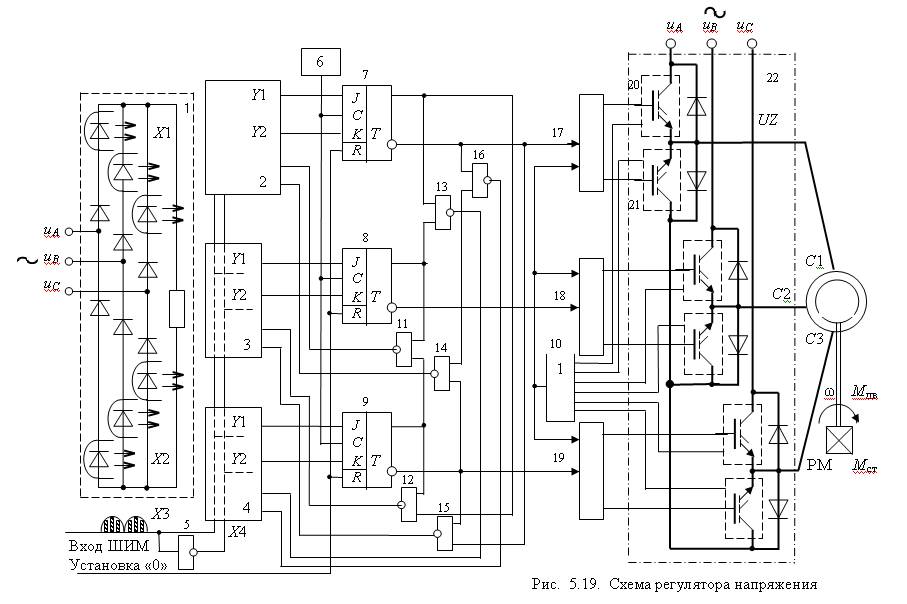

49. Схема управления регулятором напряжения.

Схема содержит синхронизатор 1; дискриминаторы 2, 3, 4; JK-триггеры 7, 8, 9 и драйверы 17, 18, 19 управления транзисторными модулями 20, 21 для каждой фазы питающего напряжения; генератор тактовых импульсов 6; элемент 5, задающий начало и конец пульса напряжения на фазе нагрузки в соответствии с законом его ШИМ, а также группу логических элементов 11…16 типа 2И-НЕ, контролирующих включенное-отключенное состояние силовых транзисторов регулятора UZ, и элемент 10, накладывающий ограничение на работу драйверов в зависимости от функционирования защитных устройств транзисторных модулей. Синхронизатор в данной схеме выполняет три функции: первая состоит в гальванической развязке сети, с которой синхронизируется система управления силовыми транзисторами регулятора, вторая – в выделении участков напряжения силовой цепи, на которых управляются силовые транзисторы (участки a – b, a – e, e – c, рис. 42, 47), а третья – в преобразовании аналогового сигнала (синусоидальных напряжений на входе синхронизатора) в цифровой сигнал (в комбинацию логических единиц и нулей на выходе синхронизатора). Первая и третья функции выполняются путем использования в схеме синхронизатора оптронных пар. Вторая – схемным решением синхронизатора. Основную функциональную роль в работе системы управления играют дискриминаторы. Каждый дискриминатор имеет (рис. 5.20):

– два синхронизирующих

входа: X1 – с положительной полуволной

напряжения, X2 – с отрицательной полуволной

того же напряжения;

два синхронизирующих

входа: X1 – с положительной полуволной

напряжения, X2 – с отрицательной полуволной

того же напряжения;

– два управляющих входа: X3, разрешающий формировать передний фронт пульса выходного напряжения, и X4, разрешающий формировать задний фронт этого пульса;

– два информационных входа: X5 и X6 о включенном и выключенном состоянии двух других фаз;

– два выхода Y1и Y2, задающих состояния JK-триггеров, необходимые для управления силовыми транзисторами регулятора. На участке a – b напряжения любой фазы синхронизирующий сигнал Х1 каждого дискриминатора имеет логическое значение, равное «1», на участке b – c или b – e – равное «0», на участке c – d – равное «0», а синхронизирующий сигнал Х2 этого же дискриминатора имеет на участке a – b логическое значение, равное «0», на участке b – c или b – e – равное «0», на участке c – d – равное «1».