- •Конспект лекций по дисциплине “Информатика” § 1. Введение в информатику

- •1. Определение инфоpматики

- •2. Понятие термина "информация"

- •3. Информация и данные

- •4. Формы существования информации

- •5. Виды информации

- •6. Как передаётся информация

- •7. Понятие о количестве информации

- •8. Свойства информации

- •9. Понятие об информационных процессах

- •10. Обработка информации

- •11. Информационные ресурсы и информационные технологии

- •12. Что означает информатизация общества?

- •§2. Общие принципы организации и работы компьютеров Введение. Краткая история вычислительной техники.

- •I Поколение

- •III Поколение

- •VI Поколение

- •V Поколение

- •1. Что такое компьютер?

- •2. Как устроен компьютер?

- •Функции процессора:

- •3. На каких принципах построены компьютеры?

- •4. Что такое команда?

- •5. Как выполняется команда?

- •6. Понятие об архитектуре и структуре компьютера

- •7. Многопроцессорная архитектура.

- •8. Основные блоки персонального компьютера.

- •9. Устройство персонального компьютера.

- •10. Что такое центральный процессор?

- •11. Принципы построения памяти

- •12. Устройства внутренней памяти

- •Оперативная память

- •Специальная память

- •12. Внешняя память компьютера.

- •Накопители на компакт-дисках.

- •Используются также накопители на магнитной ленте (стримеры):

- •13. Аудиоадаптер.

- •14. Видеоадаптер и графический акселератор.

- •15. Клавиатура.

- •16. Видеосистема компьютера.

- •Жидкокристаллические мониторы.

- •Сенсорный экран

- •17. Принтер, плоттер, сканер.

- •Плоттер

- •18. Модем и факс-модем.

- •19. Устройства - манипуляторы.

- •§3. Организация межкомпьютерной связи.

- •1. Понятие о сетевом сервере и клиенте.

- •2. Компьютерные сети и топологии.

- •3. Соединения устройств в сети.

- •4. Классификация компьютерных сетей по степени их географического распространения

- •5. Устройства для соединения локальных сетей между собой.

- •6. Беспроводные сети и их топологии

- •7. Сеть Интернет и как она работает?

- •8. Коммутация сетей в Интернет.

- •9. Структура сетевого адреса.

- •10. Информационные сервисы Интернет.

- •§4. Арифметические основы компьютеров

- •1. Система счисления.

- •2. Целые числа в позиционных системах счисления.

- •3. Системы счисления для компьютера.

- •4. Восьмеричная и шестнадцатеричная системы счисления.

- •5. Перевод целого числа из десятичной системы в другую позиционную систему счисления.

- •6. Пеpевод пpавильной десятичной дpоби в другую позиционную систему счисления.

- •7. Пеpевод числа из двоичной (восьмеpичной,шестнадцатеpичной) системы в десятичную.

- •8. Арифметические операции в позиционных системах счисления.

- •Сложение

- •Вычитание Операция вычитания является обратной по отношению к сложению.

- •Умножение

- •Деление

- •9. Представление в компьютере целых чисел.

- •Диапазоны значений целых чисел без знака

- •Целые числа со знаком

- •Диапазоны значений целых чисел со знаком

- •10. Выполнение арифметических действий над целыми числами компьютером Сложение и вычитание

- •Умножение и деление

- •11. Представление в компьютере вещественных чисел.

- •12. Выполнение арифметических действий над нормализованными числами.

- •Сложение и вычитание

- •Умножение

- •Деление

- •§ 5. Логические основы компьютеров

- •1. Что такое алгебра логики?

- •2. Что такое логическая формула?

- •3.Какая связь между алгеброй логики и двоичным кодированием?

- •4. Что такое логический элемент компьютера?

- •5. Схемы и, или, не, и-не, или-не

- •6. Что такое триггер?

- •7. Что такое сумматор?

- •§ 6. Программное обеспечение компьютеров

- •1. Что такое программное обеспечение?

- •2. Классификация программного обеспечения.

- •3. Системные программы

- •4. Операционная система.

- •5. Прикладные программы.

- •6. Файловая система ос.

- •7. Операционная система ms dos.

- •8. Программы - оболочки.

- •9. Операционные системы Windows и Windows nt.

- •10. Что такое транслятор, компилятор, интерпретатор?

- •11. Инструментальные системы программирования.

- •12. Инструментальные программы.

- •13. Текстовый редактор.

- •14. Графический редактор.

- •16. Табличный процессор.

- •17. Системы управления базами данных - субд.

- •18. Библиотеки стандартных подпрограмм.

- •19. Пакеты прикладных программ.

- •20. Интегрированные пакеты программ.

- •21. Органайзеры

- •22. Сетевое программное обеспечение.

- •§ 7. Алгоритмы, алгоритмизация и алгоритмические языки

- •1. Определение алгоритма.

- •2. Понятие -"исполнитель алгоритма".

- •3. Основные свойства алгоpитма.

- •4. Формы записи алгоритма.

- •5. Словесный способ записи алгоритмов

- •6. Графический способ записи алгоритмов.

- •7. Понятие о псевдокоде.

- •9. Основные алгоритмические структуры.

- •3. Базовая структура - цикл.

- •10. Итерационные циклы.

- •11. Вложенные циклы.

- •12. Особенности программного способа записи алгоритмов.

- •13. Уровни языков программирования.

- •14. Достоинства и недостатки машинных языков

- •15. Язык ассемблера.

- •16. Преимущества алгоритмических языков перед машинными.

- •17. Основные компоненты алгоритмического языка

- •18. Основные понятия алгоритмического языка.

- •19. Стандартные функции языка

- •20. Правила записи арифметических выражений.

- •Примеры записи арифметических выражений.

- •21. Правила записи логических выражений.

- •Примеры записи логических выражений, которые принимают значение "истина" при выполнении указанных условий.

- •§ 8.Технология решения задач с помощью компьютера

- •1. Этапы решения задач с помощью компьютера.

- •2. Понятие о математической модели.

- •3. Предварительный контроль текста программы.

- •4. Отладка и тестирование программы на компьютере.

- •5. Отладка программы современными средствами.

- •6. Тестирование программы.

- •Какими должны быть тестовые данные?

- •Основные этапы процесса тестирования.

- •7. Характерные ошибки программирования.

- •8. Сопровождение программы.

- •§ 9. Области применения информатики и компьютерной техники

- •1. Системы автоматизированного проектирования (сапр)

- •2. Автоматизированные системы научных исследований (асни)

- •3. Базы знаний и экспертные системы

- •4. Компьютеры в административном управлении

- •5. Роль компьютеров в образовании

- •7. Роль компьютеров в управлении технологическими процессами в производстве

- •8. Применение компьютеров в медицине

- •9. Применение компьютеров в торговле

- •10. Банки и Электронные деньги

- •§10. Школьный алгоритмический язык

- •1. Запись алгоритмов на школьном алгоритмическом языке? Основные служебные слова алгоритмического языка

- •2. Команды школьного языка программирования ая

- •Пример записи алгоритма на школьном языке ая.

- •3. Базовые алгоритмические структуры

- •4. Какие циклы называют итерационными?

- •5. Что такое вложенные циклы?

- •Пример вложенных циклов вида для.

- •Пример вложенных циклов вида пока.

- •6. Что такое стандартная функция?

- •7. Как записываются арифметические выражения?

- •Примеры записи арифметических выражений

- •8. Как записываются логические выражения?

- •Примеры записи логических выражений, истинных при выполнении указанных условий.

6. Что такое триггер?

Триггер — это электронная схема, применяемая в регистрах компьютера для запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. |

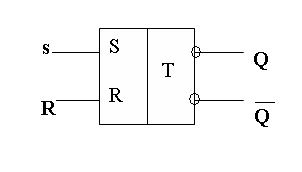

Термин триггер в схемах имеет название f lip-flop, что в переводе означает “хлопанье”. Самый распространённый тип триггера — так называемый RS-триггер ( S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера в схемах — на рис. 5.6.

Рис. 5.6

Он имеет два симметричных входа S и R и два симметричных выхода Q и ┐Q, причем выходной сигнал ┐Q является логическим отрицанием сигнала Q.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов .

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

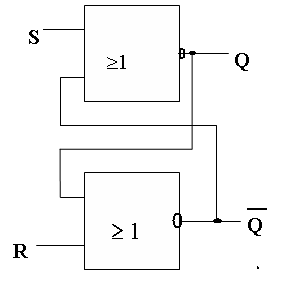

На рис. 5.7 показана реализация триггера с помощью двух вентилей ИЛИ-НЕ и соответствующая таблица истинности.

S |

R |

Q |

Q |

0 |

0 |

запрещено |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

обнуление бита |

|

Рис. 5.7

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (табл. 5.5).

1.

Если на входы триггера подать S=“1”,

R=“0”,

то (независимо от начального состояния)

на выходе Q

верхнего вентиля появится “0”. После

этого на входах нижнего вентиля окажется

R=

“0”, Q

=“0” и выход

![]() станет

равным “1”.

станет

равным “1”.

2. Точно так же при подаче “0” на вход S и “1” на вход R на выходе появится “0”, а на Q =“1”.

3. Если на входы R и S подана логическая “1”, то состояние Q и не меняется.

Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому такая комбинация для входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

7. Что такое сумматор?

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел. |

Сумматор служит центральным узлом арифметико - логического устройства компьютера – АЛУ.

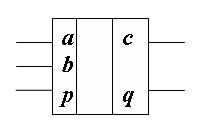

Многоразрядный двоичный сумматор предназначен для сложения многоразрядных двоичных чисел и представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение (в схемах) одноразрядного сумматора на рис. 5.8.

Рис. 5.8

При сложении двух чисел a и b в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос цифры pi–1 из младшего разряда в старший разряд.

В результате сложения получаются две цифры c и q :

1. цифра ci для суммы данного i-го разряда;

2. цифра qi - перенос цифры pi из данного разряда в старший i+1 разряд.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

Входы |

Выходы |

|||

Первое слагаемое |

Второе слагаемое |

Перенос pi-1 |

Сумма ci |

Перенос pi |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Если требуется складывать двоичные числа длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.