- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

I (invalid) - недостоверное (аннулированное) содержимое строки.

Для идентификации состояния строки служат соответствующие биты состояния. Для каждого состояния установлен определенный протокол обращения к содержимому строки.

При этом реализуется снупинг — возможность обращения к содержимому кэша данных со стороны другого устройства (процессора в мультипроцессорной системе). Установленный протокол обращения (MESI - протокол) с применением снупинга обеспечивает соответствие данных, хранящихся в различных кэшах мультипроцессорной системы, что позволяет избежать ошибок из-за использования каким-либо из процессоров старых данных, которые были модифицированы другим процессором.

Обращение к кэшу команд 1C производится устройством управления микропроцессора (см. рис. 2.70), которое одновременно выбирает из строки четыре команды (16 байт). Обращение к кэшу данных выполняется блоком LSU, который одновременно выбирает два слова (8 байт). Оба кэша подключены к общей шине через блок интерфейса BIU, который обеспечивает пересылку двух слов (8 байт) в одном цикле. Пересылка содержимого кэшей в ОЗУ или в обратном направлении выполняется с помощью пакетного обмена, при котором реализуется четыре последовательных цикла для передачи содержимого строки (32 байт).

Отдельные биты содержимого регистра конфигурации HIDO определяют режим использования кэшей. Установкой значения «О» или «1» этих битов можно обеспечить включение или отключение каждого кэша, его блокировку, при которой кэш не используется, но его содержимое сохраняется, освобождение кэша путем аннулирования содержимого его строк (перевод в недостоверное состояние).

Обычно кэши работают в режиме обратной записи, который снижает нагрузку на общую шину, обеспечивая повышение производительности системы. Однако при обращении к отдельным блокам или страницам памяти возможна реализация сквозной записи.

Изменение содержимого отдельных строк кэша 1C или DC осуществляется с помощью специальных команд (см. табл. 2.77). Эти команды производят расчет адреса ЕА = (гА!0) + (гВ), а затем выбирают строку кэша, в которой размещаются команды или данные с таким адресом. При выполнении операций со строками кэша данных учитывается состояние их содержимого: М, Е, S или I.

Команда dcbz записывает «О» во все байты выбранной строки, после чего для нее устанавливается состояние М. Если перед этим строка имела состояние S, то при выполнении команды производится обращение (снупинг) к кэшам других устройств, содержащих данную строку, и содержимое аналогичных строк аннулируется (для них устанавливается состояние I). Команда dcbst выполняет запись в память содержимого выбранной строки кэша данных, если она имеет состояние М. При других состояниях строки или при отсутствии в кэше строки, содержащей данные с полученным адресом, эта команда не производит каких-либо операций. Команда dcbf аннулирует содержимое выбранной строки кэша данных, устанавливая для нее состояние I. Если перед этим строка имела состояние М, то предварительно ее содержимое переписывается в ОЗУ. При выполнении команды dcbi аннулируется содержимое строк с аналогичным содержимым в кэшах данных всех устройств системы.

Так как при этом могут быть потеряны модифицированные данные, хранящиеся в кэшах других процессоров, то команда dcbi выполняется только в режиме супервизора (привилегированная команда, помечена символом «*» в табл. 2.77). Команда icbi производит аннулирование содержимого строки кэша команд. При выполнении команды debt (возможен вариант мнемокода dcbtst) из ОЗУ в кэш данных загружается строка, для которой устанавливается состояние Е или S (если эта строка уже присутствует в кэшах других устройств системы).

Полная очистка (аннулирование содержимого всех строк) кэшей команд или данных реализуется путем записи соответствующего содержимого в регистр HIDO, которая производится с помощью команды mtspr, выполняемой в режиме супервизора (см. табл. 2.71).

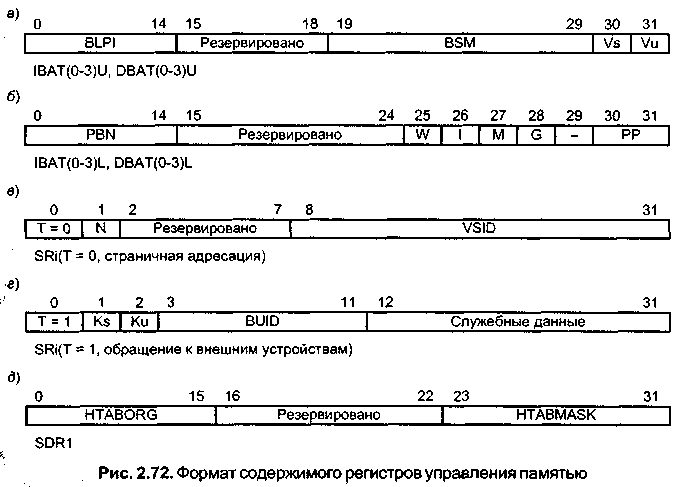

Устройства управления памятью IMMU, DMMU осуществляют трансляцию адреса при выборке команд и данных, обеспечивая возможность блочной, сегментной и страничной организации памяти. Кроме того, DMMU позволяет реализовать специальный протокол DS для многобайтного обмена данными с внешними устройствами. Работа IMMU, DMMU обеспечивается с помощью 8 пар регистров IBAT, DBAT, 16 сегментных регистров SRO-SR15 и регистра SDR1, обращение к которым выполняется только в режиме супервизора. Форматы содержимого этих регистров приведены на рис. 2.72.

Если в регистре управления MSR биты IT, DT имеют значение «О», то трансляция адреса не выполняется (IMMU, DMMU отключены), и сформированный процессором эффективный адрес поступает на выводы АО-31 в качестве физического адреса ячейки памяти или внешнего устройства. Включение IMMU, DMMU производится путем записи в регистр MSR содержимого, в котором соответствующий бит IT, DT имеет значение «1». В этом случае сформированный адрес команды или данных воспринимается как логический адрес LAO—31, который с помощью IMMU или DMMU транслируется в физический адрес РАО-31, поступающий на внешние адресные выводы. Рассмотрим реализуемые IMMU, DMMU варианты адресной трансляции.

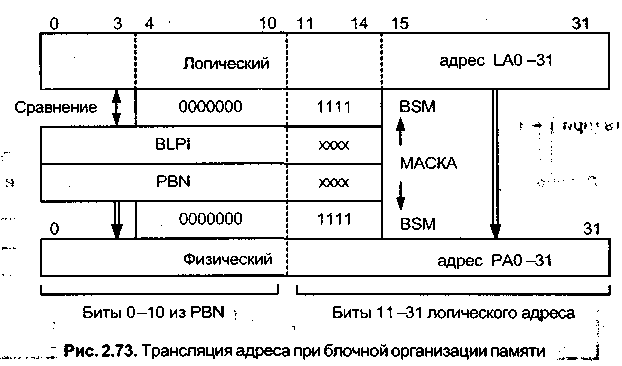

1. Блочная трансляция обеспечивает обращение к блокам внешней памяти заданного объема - от 128 Кбайт до 256 Мбайт. Возможна организация четырех блоков для хранения команд и четыре -для хранения данных. Параметры каждого блока задаются дескриптором, который содержится в паре регистров IBATiU - IBATiL для команд, DBATiU -DBATiL для данных, где i = 0...3 - номер блока (рис. 2.72, а, б). Поле BSM в дескрипторе определяет объем блока памяти (табл. 2.78) и служит маской при сравнении разрядов LA4-14 логического адреса и соответствующих разрядов логического индекса данного блока BLPI. Поле PBN содержит старшие разряды получаемого при трансляции физического адреса.

Процесс трансляции иллюстрируется рис. 2.73. Если устройство IMMU или DMMU включено, то старшие разряды сформированного логического адреса LAO-14 команды или данных сравниваются со значениями индекса BLPI в дескрипторах блоков, хранящихся в регистрах IBATOU - IBAT3U (для команд) или DBATOU - DBAT3U (для данных). При этом BSM служит маской для разрядов 4-15 адреса LA и индекса BLPI: разряды, для которых биты BSM имеют значение «1», не участвуют в сравнении. Таким образом, сравниваются старшие разряды, определяющие базовый адрес блока заданного объема. Младшие разряды LA, указывающие относительное положение байта (смещение), транслируются в младшие разряды физического адреса РА без изменений.

Если обнаруживается совпадение старших немаскированных разрядов LA с соответствующими разрядами BLPI в одном из дескрипторов, то выбираемая команда или данные размещаются в i-м блоке. В этом случае базовый физический адрес блока задается немаскированными старшими разрядами поля PBN в дескрипторе. Полученный в результате трансляции физический адрес РАО-31 содержит базовый адрес блока РАО-(14 - п), полученный из PBN, и смещение РА(15 - п)-31 = 1_А(15 - п)-31, где п - число «1» в маске BSM. В примере, данном на рис. 2.71, обеспечивается обращение к блоку объемом 2 Мбайт, для которого базовый физический адрес РАО-10 задается битами 0-10 поля PBN, а смещение РА11-31 указывается разрядами LA11-31 логического адреса.

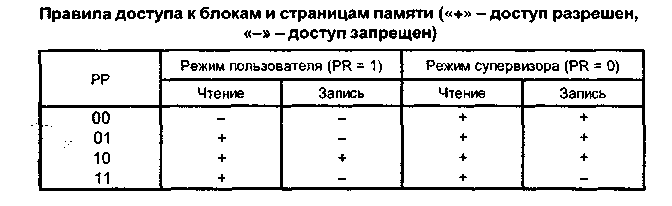

Остальные биты в дескрипторах блоков обеспечивают защиту памяти и определяют работу кэша при обращении к блоку:

Vs, Vu - разрешают обращение к блоку в режиме супервизора (при Vs =1) или в режиме пользователя (при Vu = 1);

W- обеспечивает при W = 1 режим сквозной записи для соответствующего кэша, если его использование разрешено (бит I = 0);

I -запрещает при I = 1 использование кэша при обращении к блоку;

М - обеспечивает при М = 1 соответствие данных, размещаемых в разных кэшах, путем реализации при обменах MESI-протокола;

G - запрещает при G=1 чтение из данного блока (устанавливается только в регистрах DBATiL);

РР — определяет условия доступа к данному блоку (табл. 2.79), обеспечивая совместно с битами Vs, Vu защиту блока памяти.

При нарушениях правил обращения реализуется исключение с адресом вектора Av=$00300 при выборке данных или Av = $00400 при выборке команд (см. табл. 2.64).

Если немаскированные старшие разряды логического адреса команды или данных не совпадают с разрядами индекса BLPI в каком-либо из четырех дескрипторов, то выполняется сегментная трансляция адреса.

2. Сегментная трансляция обеспечивает обращение к сегментам памяти емкостью 256 Мбайт, которые разбиваются на страницы объемом по 4 Кбайт, размещаемые в ОЗУ, или представляют массивы данных, расположенные во внешних устройствах. Для обращения к сегментам используются 16 сегментных регистров SRO-SR15, которые содержат дескрипторы сегментов (см. рис. 2.72, в, г). Если при значении бита IT = 1 или DT = 1 в регистре MSR не реализуется блочная трансляция (старшие немаскированные разряды логического адреса не совпадают с полями BLP! в дескрипторах блоков), то производится сегментная трансляция. В этом случае разряды LAO-3 задают номер i регистра SRi, из которого выбирается дескриптор соответствующего сегмента. В зависимости от значения бита Т в выбранном дескрипторе реализуется страничная адресация памяти (при Т = 0) или адресация внешних устройств (при Т = 1).

Таблица 2.79

При страничной адресации памяти биты дескриптора сегмента (рис. 2.72, в) имеют следующее назначение:

Т = 0 - определяет вид трансляции;

N-запрещает при N = 1 выборку команд изданного сегмента;

поле VSID - содержит 24-разрядный виртуальный индекс сегмента.

Процесс страничной адресации иллюстрируется на рис. 2.74. Устройство управления памятью IMMU или DMMU формирует при этом 52-разрядный виртуальный адрес VAO-51, составленный из виртуального адреса сегмента VSID, индекса страницы (разряды LA4-19 логического адреса) и относительного адреса байта на странице (разряды LA20-31 логического адреса). Старшие разряды VAO-39 этого адреса, представляющие виртуальный номер страницы VPN, поступают в блок страничной трансляции (БСТ), определяющий физический номер страницы RPN, который служит разрядами РАО-19 физического адреса. Младшие разряды физического адреса совпадают с адресом байта на странице РА20-31 = = LA20-31. Для определения RPN используются дескрипторы страниц PD, которые хранятся в специальной таблице TPD, хранящейся в ОЗУ. Базовый адрес этой таблицы задается содержимым регистра SDR1 (рис. 2.72, д): поле HTABORG содержит старшие разряды адреса, в поле HTABMASK дается маска адреса.

Дескрипторы в таблице TPD объединены в группы по восемь 64-битовых дескрипторов PD. Каждый дескриптор содержит: 30-битовый виртуальный индекс страницы, который сравнивается со значением битов (VSID:API) виртуального номера VPN; 20-битовый физический номер страницы RPN; биты W, I, M, G, имеющие такое же назначение, как аналогичные биты в дескрипторах блоков; биты РР, реализующие защиту страницы (см. табл. 2.79) совместно с битом N в дескрипторе сегмента; а также биты R, С, характеризующие предыдущие обращения к этой странице («историю» страницы). Бит R = 1, если к данной странице производилось обращение, бит С = 1, если выполнялась запись на эту страницу. Биты R, С используются операционной системой для организации виртуальной памяти, которая требует оперативного обмена содержимым страниц между ОЗУ и внешней памятью большого объема.

Дескрипторы страниц, к которым выполнялось обращение, хранятся в специальной кэш-памяти TLB, входящей в состав IMMU и DMMU. Каждый TLB содержит 128 дескрипторов PD, которые размещены в 64 наборах, имеющих по две строки. Работа TLB организована по такому же принципу, как и работа кэшей 1C, DC. В каждую из строк TLB заносится один дескриптор страницы PD, при этом для данной строки устанавливается бит достоверности V = 1. Для пустых (незаполненных) строк значение бита V = 0. Освобождение (аннулирование содержимого) строки выполняется с помощью команды tlbie, останавливающей для выбранной строки TLB значение V = 0. В качестве тега строки используются старшие разряды виртуального номера VPN, содержащиеся в дескрипторе. При совпадении тега одной из строк выбранного в TLB набора и соответствующих разрядов сформированного номера VPN (кэш-попадание) из размещенного в строке дескриптора извлекается значение RPN, используемое в качестве разрядов РАО-19 физического адреса. Таким образом, при кэш-попадании в TLB для страничной трансляции адреса не требуется обращения к таблице TPD в ОЗУ.

Дескрипторы страниц, к которым выполнялось обращение, хранятся в специальной кэш-памяти TLB, входящей в состав IMMU и DMMU. Каждый TLB содержит 128 дескрипторов PD, которые размещены в 64 наборах, имеющих по две строки. Работа TLB организована по такому же принципу, как и работа кэшей 1C, DC. В каждую из строк TLB заносится один дескриптор страницы PD, при этом для данной строки устанавливается бит достоверности V = 1. Для пустых (незаполненных) строк значение бита V = 0. Освобождение (аннулирование содержимого) строки выполняется с помощью команды tlbie, останавливающей для выбранной строки TLB значение V = 0. В качестве тега строки используются старшие разряды виртуального номера VPN, содержащиеся в дескрипторе. При совпадении тега одной из строк выбранного в TLB набора и соответствующих разрядов сформированного номера VPN (кэш-попадание) из размещенного в строке дескриптора извлекается значение RPN, используемое в качестве разрядов РАО-19 физического адреса. Таким образом, при кэш-попадании в TLB для страничной трансляции адреса не требуется обращения к таблице TPD в ОЗУ.

Если же дескриптора страницы, адресуемой VPN, не оказывается в TLB (кэш-промах), то БСТ производит обращение к TPD. При этом из ОЗУ выбирается сразу группа PD, а затем БСТ сравнивает значения полей (VSID:API) в каждом из 8 выбранных дескрипторов с соответствующими разрядами полученного виртуального номера VPN. В случае совпадения значение RPN, хранящееся в данном дескрипторе, служит разрядами РАО-19 формируемого физического адреса, а сам дескриптор заносится в TLB. Он занимает в соответствующем наборе TLB пустую строку, устанавливая для нее бит достоверности V = 1, а при отсутствии пустой строки заменяет в этом наборе дескриптор, который дольше не использовался. Если в выбранной группе PD дескриптор адресуемой страницы отсутствует, то из TPD выбирается еще одна группа дескрипторов. Если и в ней не оказывается требуемого дескриптора, то реализуется исключение с адресом вектора Av = $00300 при выборке данных или Av = $00400 при выборке команды (см. табл. 2.64). При организации виртуальной памяти подпрограмма обслуживания должна в этом случае обеспечить загрузку в ОЗУ необходимой страницы из внешней памяти, поместив в TPD соответствующий дескриптор.

При выполнении страничной трансляции учитываются значения битов N, W, I, M, G дескрипторов. При нарушении правил обращения к сегментам и страницам реализуется исключение «ошибка выбора данных» (Av = $00300) или «ошибка выбора команды» (Av = $00400).

При адресации внешних устройств (ВУ) с помощью сегментной трансляции (реализация протокола DS) биты дескриптора сегмента в регистре SRi имеют следующее назначение (рис. 2.72, г):

Т= 1 -определяет вид трансляции;

Ks, Kp - адресные ключи, которые выдаются на шину адреса при адресации внешних устройств для идентификации режима процессора;

BUID -9-битовый код идентификации внешнего устройства, к которому производится обращение.

Этот вид трансляции адреса реализуется только при передаче данных с помощью команд загрузки-сохранения содержимого регистров GPR (см. табл. 2.68) или FPR (см. табл. 2.76).

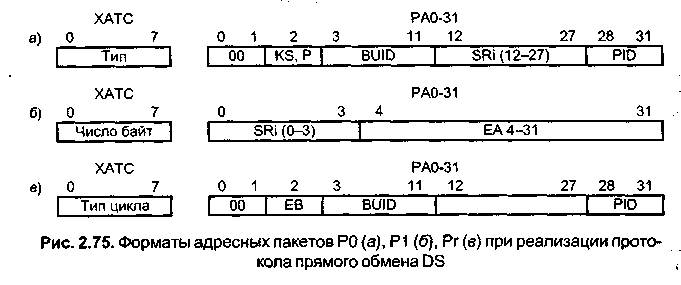

Если при сегментной трансляции адреса данных из регистра SRi выбирается дескриптор, имеющий значение бита Т = 1, то реализуется специальный протокол DS (direct-store) прямого обмена данными с ВУ. В этом случае процессор выполняет сдвоенные циклы обмена, каждый из которых занимает три такта. В первой части цикла на шину адреса выдается адресный пакет РО, во второй части цикла - пакет Р1. Каждый пакет сопровождается выдачей на внешние выводы микропроцессора 8-разрядного кода ХАТС, определяющего тип и параметры выполняемого цикла. Код ХАТС поступает на выходы, которые при обычных циклах обмена указывают тип выполняемого цикла и разрядность данных.

Адресный пакет РО (рис. 2.75, а), выдаваемый DMMU в начале каждого цикла обмена, содержит ключевой бит Ks или Кр, код BUID, идентифицирующий адресуемое ВУ, и служебную информацию, которая может быть записана в разрядах 12-27 используемого сегментного регистра SRi. Таким образом, биты РА2-27 формируемого физического адреса соответствуют битам выбранного регистра SRi (рис. 2.72, г), причем значение РА2 = Ks, если микропроцессор работает в режиме супервизора, или РА2 = Кр, если в режиме пользователя. В разрядах РА28-31 указывается код идентификации (номер) процессора, выбираемый из регистра PIR (рис. 2.68). Пакет РО определяет источник и приемник данных -процессор с номером PID и ВУ с номером BUID.

Во второй половине цикла DMMU выдает адресный пакет Р1 (рис. 2.75, б), содержащий разряды 0-3 регистра SRi и разряды ЕА4-31 Этот пакет позволяет выбрать различные адресаты (регистры) в составе ВУ, к которым выполняется обращение (запись или считывание) в данном цикле.

В соответствии с протоколом DS обмен начинается циклом инициализации и завершается циклом подтверждения. Между этими циклами выполняется необходимое число циклов пересылки данных.

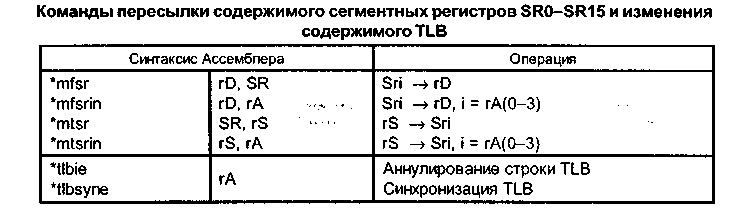

Для пересылки содержимого сегментного регистра SRi в какой-либо из регистров общего назначения rD и обратно используются команды mfsr, mfsrin и mtsr, mtsrin (табл. 2.80).Номер сегментного регистра i задается операндом SR (команды mfsr, mtsr) или разрядами 0-3 регистра ргА (команды mfsrin, mtsrin). Команда tlbie аннулирует содержание выбранной строки в кэше дескрипторов страниц TLB, устанавливая для нее значение бита V - 0.При этом содержимое регистра гА, указанного в качестве операнда, используется в качестве логического адреса LAO-31, для которого определяется виртуальный номер страницы VPN. Если дескриптор этой страницы присутствует в какой-либо из строк TLB команд или данных, то содержимое данной строки аннулируется. Команда tlbsync выполняется после команд tlbie, если требуется произвести аннулирование соответствующих строк в TLB других (ведомых) микропроцессоров. Эта команда осуществляет снупинг, обращаясь к внутреннему содержимому других TLB, чтобы обеспечить соответствие выполняемых программа используемых данных при совместной работе микропроцессоров в составе мультипроцессорной системы.

Таблица 2.80

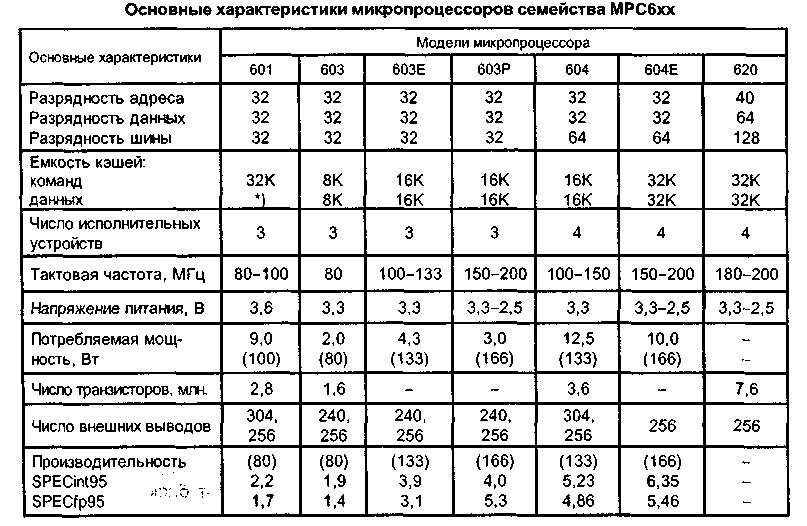

Номенклатура и применение микропроцессоров МРСбхх. Как отмечалось выше, консорциум компаний, реализующих семейство PowerPC, разработал и выпускает ряд моделей микропроцессоров этого семейства. Основные характеристики этих моделей приведены в табл. 2.81.

Все микропроцессоры семейства имеют одинаковую архитектуру PowerPC, которая включает регистровую модель пользователя (см. рис. 2.67), набор реализуемых команд и способов адресации, состав исключений и процедуру их обслуживания. Только в модели МРС620 введено несколько дополнительных команд для выполнения операций с 64-разрядными числами. Функции большинства регистров в модели супервизора (см. рис. 2.68) также одинаковы для всего семейства. Все модели имеют суперскалярную структуру (см. рис. 2.70), которая содержит 3 или 4 исполнительных устройства: два (SIU, MIU) или три (SIU1, SIU2, MIU) для обработки целочисленных операндов и одно (FPU)-для обработки операндов с плавающей точкой.

В состав семейства МРСбхх входят четыре основных модели: 601,603,604 и 620, которые имеют ряд модификаций, отличающихся в основном объемом внутренней кэш-памяти и уровнем технологии изготовления, определяющей размеры кристалла и расположенных на нем компонентов микропроцессора. Все микропроцессоры семейств изготавливаются с помощью КМОП-технологии с минимальными размерами компонентов (МОП-транзисторов): от 0,65 мкм для первых моделей 601,603 до 0,35 мкм для моделей 603Е, 604Е, 620, выпущенных в 1995-96 гг. Уменьшение размеров компонентов позволило повысить тактовую частоту до Ft - 200 МГц и увеличить за счет этого производительность микропроцессоров.

Для относительной оценки производительности в табл. 2.81 приведены результаты испытаний, полученных при использовании стандартных тестовых программ обработки целых чисел (SPECint 95) и чисел с плавающей точкой (SPECfp 95). В скобках указано значение тактовой частоты Ft. Как показывают приведенные данные, за 5 лет, прошедших с начала выпуска микропроцессоров этого семейства, их производительность возросла в 3-4 раза.

Типовое значение напряжения питания микропроцессоров составляет 3,3 В. При этом в ряде моделей для питания основной части (ядра) процессора используется напряжение 2,5 В. Благодаря пониженному напряжению питания сохраняется допустимый уровень потребления мощности. Так как для КМОП-микросхем потребляемая мощность возрастает пропорционально тактовой частоте, в табл. 2.81 для каждого микропроцессора дано значение Ft (в скобках), при котором потребляется указанная мощность.

Таблица 2.81

Сразу после начала выпуска микропроцессоры семейства МРСбхх нашли широкое применение в разнообразных цифровых системах. На базе первой модели МРС601 были реализованы персональные компьютеры PowerMacintosh компании «Apple Computers» и PowerStack компании «Motorola», рабочие станции RS/6000 компании IBM и ряд других изделий. Появление новых микропроцессоров этого семейства еще более расширило сферу его применения. В настоящее время определился следующий ряд областей, где использование микропроцессоров МРСбхх наиболее эффективно.

Модель МРС603 и ее модификации, имеющие наиболее низкое энергопотребление, широко используются в персональных компьютерах класса «notebook» и различной сложно-функциональной портативной аппаратуре. Так как модификация МРС603Р обеспечивает достаточно высокую производительность, то на ее базе реализуются также портативные рабочие станции. Модель МРС604 и ее модификации используется в основном в персональных компьютерах, заменяя в этой области более раннюю модель МРС601. Широкое применение данная модель находит также в серверах, особенно ее быстродействующая модификация МРС604Е. Модель МРС620 ориентирована на применение в высокопроизводительных рабочих станциях и мощных серверах.

Помимо перечисленных выше областей применения RISC-микропроцессоры с архитектурой PowerPC используются в разнообразных устройствах управления системами и объектами, где требуется высокая производительность и широкие функциональные возможности в сочетании с пониженным энергопотреблением и относительно невысокой стоимостью. На базе RISC-процессоров с этой архитектурой разработаны RISC-микроконтроллеры и коммуникационные контроллеры для использования в системах управления и связи. Особенности их структуры и функционирования рассмотрены в следующих разделах данной главы.

Следует отметить, что наряду с микропроцессорами и микроконтроллерами семейств МРСбОх, МРСбОх фирма «Motorola» выпускает также магистральные адаптеры МРС105, МРС106, которые обеспечивают интерфейс между общей шиной систем с архитектурой PowerPC и 32-разрядной шиной PCI, широко используемой в современных персональных компьютерах. С помощью этих адаптеров можно организовать совместную работу систем, реализуемых на базе МРСбОх или МРСбОх, с персональными компьютерами.