- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

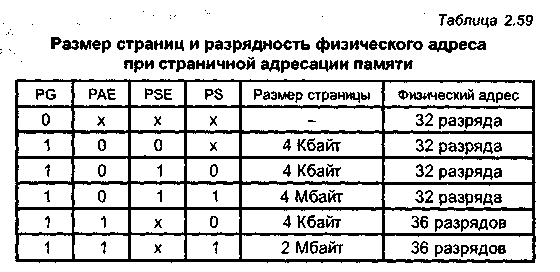

2.7.2. Страничная организация памяти

Страничная организация памяти реализуется процессором только в защищенном режиме, если в регистре управления CR3 установлено значение бита PG = 1. Размер страниц может составлять 4 Кбайт или 4 Мбайт при использовании 32-разрядных адресов и 4 Кбайт или 2 Мбайт при использовании расширенных 36-разрядных адресов. В отличие от сегментов, которые могут иметь различные размеры (от 1 байта до 4 Гбайт), размеры страниц строго фиксированы.

Если размер страниц составляет 4 Кбайт, то сегмент разбивается на отдельные разделы, число которых может достигать 210 = 1024. Каждый раздел может содержать до 210 = 1024 страниц по 4 Кбайт. Если размер страниц составляет 4 Мбайт или 2 Мбайт, то сегмент разбивается только на отдельные страницы, число которых может составлять 1024 или 2048.

Начальные (базовые) адреса страниц и разделов содержатся в специальных таблицах (каталогах), которые хранятся в основной памяти. Кроме базовых адресов в этих таблицах содержатся также атрибуты соответствующих разделов и страниц, определяющие правила доступа к ним и указывающие текущее состояние их содержимого. Совокупность этих параметров, характеризующих страницы и разделы (каталоги), представляется в виде 32-или 64-разрядных указателей страниц, разделов и каталогов (см. рис. 2.45,2.47).

Страницы, содержащие определенный сегмент программ или данных, могут быть рассеяны по разным частям памяти, а их размещение определяется содержанием каталога разделов и таблиц страниц. Таким образом обеспечивается более эффективное использование (заполнение) памяти по сравнению с сегментной. Однако при этом требуется дополнительное время и специальные аппаратные средства для преобразования (трансляции) адресов.

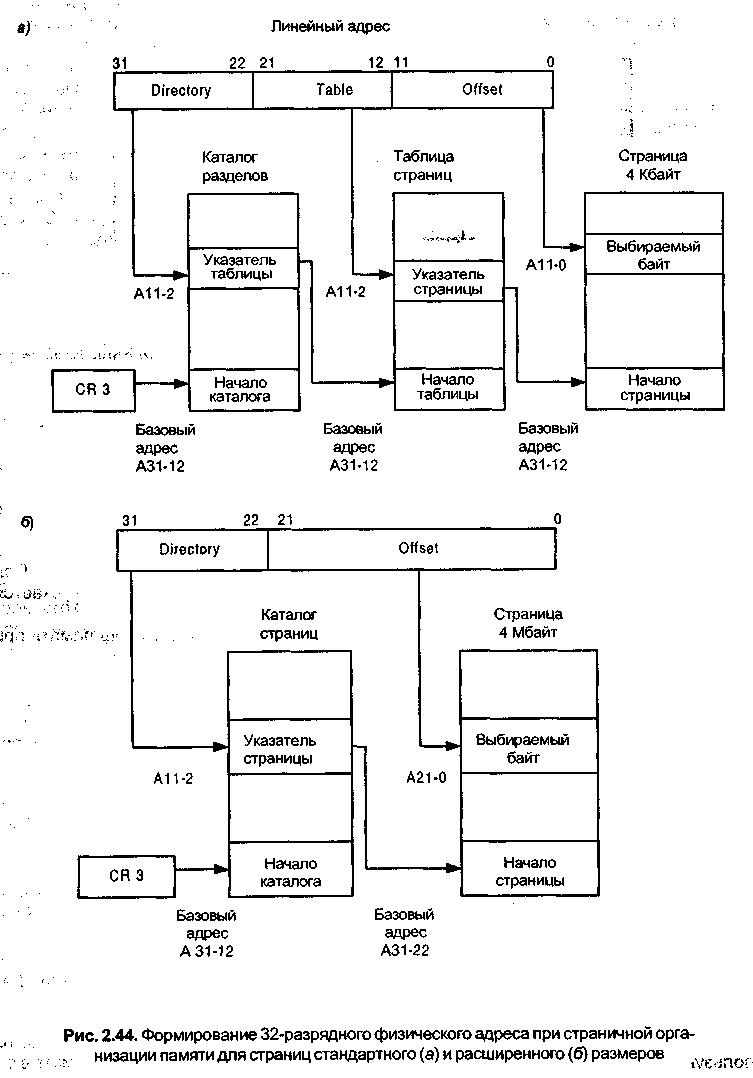

Линейный 32-разрядный адрес, получаемый в результате преобразования логического адреса, является исходной информацией для формирования физического адреса с помощью каталога разделов и таблиц страниц. Процедура формирования физического адреса при страничной организации зависит от размера используемых страниц и разрядности адреса, которые определяются значениями ряда битов, содержащихся в регистре управления CR4 и указателях разделов и страниц:

PSE в регистре CR4 (см. рис. 2.7) - разрешает при значении PSE = 1 использование страниц расширенного размера (4 или 2 Мбайт), при PSE = 0 используются только страницы стандартного размера (4 Кбайт);

РАЕ в регистре CR4 (см. рис. 2.7) - задает разрядность формируемого физического адреса: стандартная (32 разряда) при РАЕ = 0 или расширенная (36 разрядов) при РАЕ = 1;

PS в указателе раздела или страницы (см. рис. 2.45,2.47) - указывает размер используемых страниц аналогично биту PSE.

Совместное действие этих битов при установленном значении бита PG = 1 определяет разрядность формируемого физического адреса и размер используемых страниц (табл. 2.59).

Линейный адрес при страничной организации рассматривается как совокупность трех полей (рис. 2.44). Поле Directory (разряды А31-22 линейного адреса) указывает относительный адрес таблицы страниц, выбираемой в каталоге раздела. Поле Table (разряды А21-12 линейного адреса) задает относительный адрес требуемой страницы раздела. Поле Offset (разряды А11-0 линейного адреса) содержит относительный адрес выбираемого на странице байта.

Формирование 32-разрядного физического адреса выбираемого байта при использовании страничной адресации с размером страниц 4 Кбайт осуществляется путем последовательного обращения к каталогу разделов и таблице страниц (рис. 2.44, а). Каталог разделов занимает одну страницу памяти, где для каждого из 1024 возможных разделов содержатся 32-разрядные указатели входа в таблицу страниц этого раздела. Каждая из таблиц страниц также занимает одну страницу, где для каждой из 1024 страниц раздела даются 32-разрядные указатели входа в нее.

Выбор раздела определяется содержимым поля Directory линейного адреса, которое указывает относительный адрес А11 -2 указателя таблицы страниц, хранящегося в каталоге разделов. Содержимое регистра управления CR3 задает базовый адрес (значение 20 старших разрядов А31-12) каталога разделов, ячейки памяти, содержащей указатель входа в таблицу страниц раздела. Этот указатель задает базовый адрес (разряды А31-12) таблицы страниц выбранного раздела. Поле Table линейного адреса содержит разряды А11-А2 адреса ячейки (относительный адрес в таблице страниц), в которой хранится указатель страницы. Указатель задает базовый адрес (разряды А31-12) страницы, на которой размещается выбираемый байт, относительный адрес которого (разряды А11-0) содержится в поле Offset линейного адреса. Таким образом, при страничной организации памяти 32-разрядный (физический) адрес формируется как сумма базового адреса, задаваемого указателем страницы, и относительного адреса, содержащегося в поле Offset.

Если в регистре управления CR4 установлено значение бита PSE = 1, то обеспечивается работа со страницами расширенного размера 4 Мбайт. При этом линейный адрес содержит два поля: Directory и Offset, и для формирования 32-разрядного физического адреса используется только одна таблица - каталог страниц (рис. 2.44, б). Процедура формирования адреса в этом случае аналогична рассмотренной выше для страниц размером 4 Кбайт.

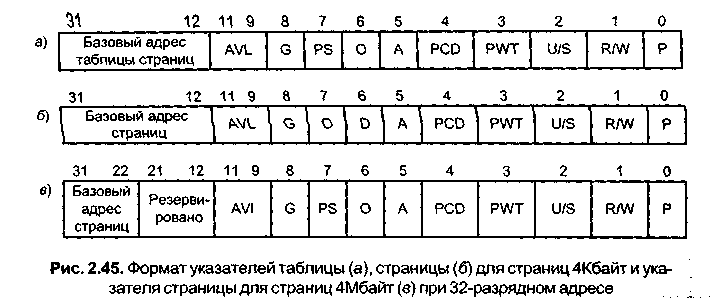

Формат содержимого указателей таблиц и страниц при использовании 32-разрядных адресов приведен на рис. 2.45. Помимо базового адреса таблицы и страницы указатели содержат дополнительную информацию, определяющую порядок их использования. Эта информация задается значениями следующих битов.

Бит присутствия Р разрешает при установленном значении Р = 1 использование соответствующего раздела или страницы. Если же Р = 0 (раздел или страница отсутствует), то попытка обращения к ним вызовет исключение типа #PF («отсутствие доступа к странице»). Отметим, что при Р = 0 остальные биты указателя могут служить для представления какой-либо информации, используемой операционной системой.

Бит чтения-записи R/W, бит пользователя- супервизора U/S определяют права доступа к соответствующим разделу или странице для программ пользователя, имеющих минимальные привилегии (уровень PL = 3). Если осуществляется запрос с уровнем привилегий RPL = 3 (программы пользователя), то при значении U/S = 0 ему запрещается доступ к соответствующему разделу или странице. Если U/S = 1, то при значении R/W = О разрешается только чтение раздела или страницы, а при R/W = 1 и чтение, и запись. При запросах с большими привилегиями (системные программные уровни 0,1,2) допускается запись и чтение разделов и страниц при любых значениях U/S, R/W.

Биты PWT и PCD указателя используются для управления работой кэш-памяти при страничной адресации.

Бит обратной записи страниц PWT определяет метод обновления содержимого кэш-памяти. При PWT = 1 для текущей страницы обновление реализуется методом сквозной записи, при PWT = 0 - методом обратной записи.

Бит запрещения кэширования страницы PCD запрещает при PCD = 1 загрузку содержимого данной страницы во внутреннюю кэш-память. При PCD = 0 такая загрузка разрешена.

Бит PWT и PCD определяют значения сигналов на внешних выходах PWT, PCD процессора. Бит PCD вместе с входным сигналом KEN управляет работой внутренней кэш-памяти.

Бит доступа А автоматически устанавливается процессором в состояние А = 1 при обращении к данному разделу или странице для записи или чтения информации.

Бит модификации D в указателе страницы устанавливается в состояние 0=1 при записи на данную страницу. В указателях таблиц данный бит не используется (устанавливается в «О»).

Биты А и D используются операционной системой, поддерживающей виртуальную память, для определения в оперативной памяти разделов и страниц, содержание которых подлежит замене из внешней памяти. Проверку и сброс этих битов выполняет операционная система.

Бит размера страниц PS при установленном значении бита PSE = 1 указывает, раз мер используемых страниц: 4 Кбайт при PS = 0, 4 Мбайт при PS = 1

Бит глобальности G программно устанавливается в состояние «1», чтобы отметить разделы или страницы, часто используемые при решении данной задачи. Базовые адреса этих разделов или страниц, загруженные во внутреннюю буферную память TLB, сохраняются при ее очистке. Подробнее работа TLB рассмотрена ниже.

Биты 9-11 указателей (AVL на рис. 2.45) зарезервированы для операционной системы (ОС), которая может использовать их для своих потребностей. Например, в этих битах может размещаться информация о времени последнего обращения к данному разделу или странице. Эта информация используется ОС для определения разделов и страниц, подлежащих замене из внешней памяти.

Если процессор работает в режиме формирования расширенных 36-разрядных адресов (в регистре CR4 установлено значение бита РАЕ = 1), то процедура формирования физического адреса несколько усложняется (см. рис. 2.46). В этом случае вводится дополнительная таблица каталогов, с помощью которой адресуется каталог разделов (при использовании стандартных страниц 4 Кбайт, рис. 2.46, а) или каталог страниц (при использовании расширенных страниц 2 Мбайт, рис. 2.46, б). Для обращения к таблице каталогов в линейном адресе выделяется 2-разрядное поле Directory Pointer. В основном процедура трансляции производится также, как описано выше для формирования 32-разрядных адресов. Отличия состоят в том, что выполняется дополнительный этап трансляции с обращением к таблице каталогов.

Форматы указателей каталогов, разделов и страниц, используемых при расширенной адресации, показаны на рис. 2.47. Указатели содержат 64 бита (часть из них резервирована), назначение которых аналогично соответствующим битам указателей при стандартной 32-разрядной адресации (см. рис. 2.45). Указатели имеют поля, в которых хранятся старшие разряды 36-разрядных базовых адресов каталогов, разделов и страниц. С помощью страничной трансляции (рис. 2.46) формируется 36-разрядный физический адрес команды или операнда.

Отметим, что расширенная разрядность адреса реализуется только при использовании страничной адресации, когда установлены значения битов PG = РАЕ = 1.

Как указано выше, страничная организация памяти требует дополнительных затрат вре-ме ни для преобразования (трансляции) линейного адреса в физический. Эти затраты будут весьма значительными, если в каждом цикле производить обращение к оперативной памяти для выбора указателей таблиц и страниц. Существенное сокращение времени преобразования адресов достигается путем использования специализированной внутренней кэш-памяти, которая называется буфером ассоциативной трансляции TLB (translation look-aside buffer).

С помощью команды INVLPG производится очистка (аннулирование содержимого) строк TLB. При этом очищается строка, содержащая базовый адрес страницы, на которой размещается адресованная командой ячейка памяти. Одновременная очистка всех строк TLB производится при записи в регистр CR3 нового значения базового адреса каталога разделов, а также при переключении задач.

Можно предохранить от аннулирования в TLB базовые адреса страниц, задав для них в указателе страницы (см. рис. 2.45, б, в, 2.47, в, г) значение бита глобальности G = 1. Если в регистре CR4 (см. рис. 2.7) установлен, бит разрешения глобальности PGE - 1, то базовые адреса этих страниц в TLB не будут аннулироваться при переключении задач или перезагрузке содержимого CR3. Таким образом, можно избежать потерь времени на трансляцию базового адреса для страниц, используемых в процессе выполнения различных задач (например, для страниц, содержащих ядро операционной системы).