- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

2.8.3. Средства обеспечения отладки

Процессоры семейства Р6 реализуют широкий набор вариантов отладки:

программный останов,

пошаговый режим,

отладку с использованием регистров отладки,

отладку с использованием специализированных MSR-регистров,

режим зондовой отладки.

Программный останов. Этот способ отладки реализуется с помощью однобайтной команды INT3, которая вводится программистом в критические точки программы, где необходимо выполнить контроль текущего состояния. Команда INT3 устанавливает безусловную программную точку останова, при выполнении которой процессор реализует исключение #ВР. Команда INT3 выполняется при любых значениях уровня привилегий программы CPL и содержимого поля IOPL. Исключение #ВР всегда вызывается через таблицу IDT. При работе процессора в режиме виртуального 8086 на выполнение команды INT3 не оказывает влияния значение битов в карте перенаправления прерываний (при установленном значении бита VME = 1 в регистре CR4). При вызове подпрограммы обслуживания через шлюз уровень приоритета этого шлюза gDPL должен быть больше или равен CPL

Пошаговый режим. Пошаговый режим имеет место, когда установлено значение признака TF=1 в регистре EFLAGS. В этом случае процессор после выполнения каждой команды (ловушка) реализует исключение типа #DB, вызывая соответствующую подпрограмму обслуживания. Перед вызовом этой подпрограммы процессор устанавливает значение признака TF = 0, чтобы обеспечить выполнение обработки без пошаговых остановов. Команда IRET, завершающая подпрограмму обработки, восстанавливает из стека содержимое регистра EFLAGS (где значение TF = 1), передавая управление следующей команде программы, после которой снова реализуется прерывание #DB.

Останов с помощью регистров отладки DRO-DR7. Регистры отладки имеют следующее назначение:

DR3-0 - содержат линейные адреса четырех контрольных точек останова; DR6 - регистр состояния, указывающий причину останова в контрольной точке; DR7 - регистр управления, задающий условия останова в контрольных точках.

Доступ к регистрам отладки разрешен только программам с уровнем привилегий CPL = 0. Попытка обратиться к этим регистрам на другом уровне привилегий (CPL > 0) приводит к исключению #GP.

Регистры DR4, DR5 в выпускаемых моделях процессоров не используются. Если в регистре управления CR4 установлено значение бита DE = 1 (расширение отладки), то обращение к регистрам DR4, DR5 приводит к исключению #UD. Если бит DE = 0, то при вызове DR4, DR5 производится обращение к регистрам DR6, DR7.

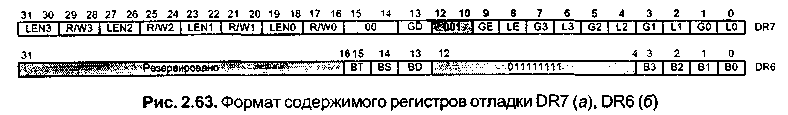

Формат содержимого регистров управления DR7 и состояния DR6 отладки показан на рис. 2.63.

Регистр управления отладкой DR7 определяет условия останова для каждой из четырех контрольных точек, линейные адреса которых находятся в регистрах DRO-DR3. Отдельные биты и поля в регистре DR7 имеют следующее назначение:

LENi-размер точки останова. Двухбитные поля LEN/указывают, какие биты линейного адреса участвуют в определении адреса срабатывания /-и точки останова, определяя, таким образом, размер области памяти, в пределах которой выполняется останов.

При реализации останова по обращению к данным поле LEN/ может принимать следующие значения:

00 -1 байт (используются биты А31-0 линейного адреса в регистре DRi);

01-2 байта (используются биты А31-1 линейного адреса);

10-не определено;

11-4 байта (используются биты А31-2 линейного адреса).

Если соответствующее поле R/W/ в регистре DR7 равно 00 (реализация останова по выборке команды), то поле LENi должно быть равно 00.

R/Wi-mun доступа. Двухбитные поля R/W/ определяют тип обращения к памяти, при котором происходит срабатывание / - и точки останова. Поле R/Wi может принимать следующие значения:

00-выборка команды;

01-записьданных;

10 -чтение или запись порта ввода/вывода (при значении бита DE = 1 в регистре управления CR4, при DE = 0 значение R/Wi=10 не определено);

11-запись или чтение данных.

Точки останова по выборке команд обрабатываются как ошибки, а точки останова по обращению к данным - как ловушки. Срабатывание точки останова при выборке команды происходит только тогда, когда линейный адрес точки останова указывает на первый байт команды (включая префиксы). Срабатывание точки останова при обращении к данным или портам ввода/вывода имеет место, когда заданный адрес операнда полностью или частично попадает в область срабатывания точки останова (область определяется регистром DR/'и полем LENi в регистре DR7).

GD - идентификация обращений к регистрам отладки. Когда установлено значение бита GD = 1, то обращение к регистрам отладки приводит к исключению #DB. В этом случае перед реализацией исключения #DB в регистре состояния DR6 устанавливается значение бита BD = 1, а бит GD сбрасывается в «О», что дает возможность обработчику исключения #DB обращаться к регистрам отладки.

GE, LE -не используемые (резервированные) биты, которые рекомендуется устанавливать в «1».

Gi - разрешение глобальных точек останова. Установка этого бита разрешает срабатывание соответствующей контрольной точки во всех задачах. Если выполняется условие срабатывания i-й контрольной точки (определенное регистром DRi и полями LENi, R/Wi в регистре DR7) и установлено значение бита Gi = 1, то реализуется исключение #DB. Бит Gi не изменяется при переключении задач.

Li - разрешение локальных точек останова. Установка этого бита разрешает срабатывание соответствующей контрольной точки в текущей задаче. Если выполняется условие срабатывания /-и контрольной точки и значение бита L/ = 1, то реализуется исключение #DB. Бит L/автоматически сбрасывается в «О» при переключении задач.

Так как точки останова по выборке команды обрабатываются как ошибки, то после возврата из подпрограммы обработки процессор снова попытается выполнить команду, на которую установлена точка останова, и снова будет реализовано исключение #DB. Для предотвращения такого зацикливания на одной точке останова в архитектуре процессора предусмотрен признак RF в регистре EFLAGS. Когда установлено значение RF = 1, то процессор игнорирует точки останова по выборке команды. Значение флага RF не оказывает влияния на срабатывание точек останова по выборке данных или точек останова по операциям ввода/вывода. Процессор автоматически устанавливает флаг RF = 1 перед вызовом любого исключения-отказа, кроме #DB, которое было вызвано точкой останова по выборке команды. Программа-обработчик исключения #DB может либо запретить точку останова, либо установить значение признака RF = 1 в содержимом регистра EFLAGS, хранящемся в стеке. При возврате из обработчика команда IRETD восстановит значение признака RF из хранящегося в стеке содержимого регистра EFLAGS. Команды POPF, POPFD и IRET не изменяют значение RF. После возврата повторной генерации исключения #DB не произойдет, так как значение признака RF = 1. Процессор автоматически устанавливает значение RF = 0 после выполнения любой команды, кроме команды IRETD и команд JMP, CALL, INT n, которые вызывают переключение задач. Процессор не устанавливает признак RF перед вызовом исключений-ловушек, аппаратных или программных прерываний.

Регистр состояния DR6 содержит информацию, которая указывает причину последнего исключения отладки #DB. Отдельные биты содержимого DR6 имеют следующее назначение:

ВТ-ошибка при переключении задач. Принимает значение ВТ = 1, если исключение #DB имело место из-за переключения на задачу, имеющую бит Т = 1 в сегменте TSS. Исключение #DB происходит после выполнения первой команды в новой задаче. Если исключение #DB обрабатывается через шлюз задачи, то бит Т в сегменте TSS обработчика должен иметь значение «1».

BS - реализация пошагового режима отладки. Принимает значение BS = 1, если исключение #DB имело место из-за установленного значения признака TF = 1 в регистре EFLAGS. Исключение пошагового режима самое приоритетное среди исключений отладки. Вместе с битом BS может быть установлен любой другой бит в регистре DR6.

BD - отказ при обращении к регистрам отладки при установленном бите GD в регистре DR7. Значение BD = 1 устанавливается, если исключение #DB происходит из-за попытки обратиться к регистрам отладки, когда установлен бит GD в регистре управления отладкой DR7. Перед передачей управления обработчику исключения #DB бит GD в регистре управления отладкой DR7 сбрасывается в «О». Это дает возможность обработчику исключения #DB обращаться к регистрам отладки.

В/- останов в 1-й контрольной точке. Четыре бита индикации останова соответствуют четырем регистрам DRO-DR3. Значение В/ = 1 устанавливается при выполнении условий, определенных регистром DR/ и полями LEN/, R/W/ в регистре DR7. Биты В; устанавливаются в «1» даже в том случае, когда соответствующая точка останова не разрешена с помощью битов L/7G/ в регистре DR7. Если одновременно выполняются условия для нескольких точек останова и хотя бы одна из этих точек останова разрешена, то реализуется исключение #DB. При этом значения битов В/ = 1 будут установлены для всех точек останова.

Биты регистра DR6 устанавливаются в «1» аппаратно при реализации соответствующих исключений. Сброс этих битов в нулевое значение выполняется программно, путем загрузки нового содержимого в регистр DR6. Эта процедура осуществляется программой обработки исключения #DB, которая перед возвратом к исходной программе должна очистить регистр DR6, установив значение «О» для всех битов.

Поддержка отладки с помощью MSR-регистров. Процессоры семейства Р6 содержат пять MSR регистров, которые предоставляют дополнительные возможности отладки: DebugCtlMSR (адрес 1 D9h), LastBranchTolP (адрес 1 DCh), LastBranchFromlP (адрес 1 DBh), LastExceptionTolP (адрес 1 DEh) и LastExceptionFromlP (адрес 1 DDh).

На рис. 2.64 приведен формат содержимого регистра DebugCtlMSR, с помощью которого производится управление режимом отладки. Его отдельные биты имеют следующее назначение:

BTF - бит разрешения пошаговых ветвлений. Когда значение BTF = 1, процессор интерпретирует значение признака TF = 1 в регистре EFLAGS как «пошаговые ветвления», а не «пошаговые команды». Это означает, что исключение #DB будет генерироваться только при обнаружении ветвления, прерывания или исключения. Бит BTF автоматически устанавливается в «О» перед передачей управления обработчику исключения #DB.

PBi - биты разрешения выдачи внешних сигналов при останове в контрольных точках. Когда бит Pbi = 1, то на соответствующем выходе процессора устанавливается сигнал BPi# = 0 при останове в контрольной точке, определенной регистром DRi. Когда значение битов PBi = 0, то выводы BPi# используются для вывода данных о мониторинге производительности процессора.

TR - бит разрешения выдачи сообщений о трассировке ветвлений. Если установлено значение TR=1, то процессор при выполнении ветвления, прерывания или исключения выдает на системную шину адрес исходной команды и команды, которой передается управление. Трассировка ветвлений приводит к снижению производительности процессора, так как о каждом ветвлении выполняется сообщение по системной шине.

LBR - бит разрешения записи информации о ветвлениях. При установке значения LBR = 1 процессор фиксирует все передачи управления. Когда происходит ветвление, процессор заносит в регистр LastBranchFromlP адрес команды ветвления, а в регистр LastBranchTolP- адрес самого перехода. Если реализуется прерывание или исключение (кроме исключения #DB), процессор копирует значение регистров LastBranchFromlP и LastBranchTolP в регистры LastExceptionFromlP и LastExceptionTolP соответственно. Затем адрес прерванной команды заносится в регистр LastBranchFromlP, а адрес вызываемого обработчика - в регистр LastBranchTolP. Бит LBR автоматически устанавливается в «О» перед передачей управления обработчику исключения #DB.

Таким образом, использование отладочных MSR-регистров обеспечивает дополнительные возможности контроля выполнения программы в процессе ее отладки.

Режим зондовой отладки. Этот способ отладки реализуется с помощью тестового пор- , та ТАР, который служит для тестирования процессора и подключенных к нему устройств системы. Специальный режим «зондовой» отладки (Probe Mode) позволяет использовать порт ТАР для ввода команд и данных, чтения и записи содержимого всех внутренних регистров процессора. С помощью этого режима можно обеспечить выполнение отлаживаемой программы, контролируя и корректируя содержимое регистров.