- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

NT-признак вложенной задачи, принимает значение N1 = 1 при переключении процессора на выполнение другой задачи с помощью команды вызова CALL; используется для организации многозадачного режима;

RF-признак маскирования ошибок отладки, при установке значения RF= 1 возможные ошибки отладки игнорируются при выполнении следующей команды; используется в процессе отладки программ;

VM - признак режима виртуального 8086, установка значения VM = 1 вызывает переключение процессора в режим виртуального процессора 8086, при котором эмулируются возможности микропроцессора 8086;

АС - признак контроля выравнивания, установка значения АС = 1 и бита AM = 1 в регистре CRO вводит контроль выравнивания операндов при обращениях к памяти; в этом случае при обращении к невыравненному операнду (выборка слова по нечетному адресу или двойного слова по адресу, не кратному четырем) реализуется исключение типа #АС;

VIF- признак разрешения обслуживания виртуального прерывания, установка значения VIF = 1 разрешает обслуживание запросов виртуальных прерываний, поступление которых фиксируется установкой признака VIP = 1;

VIP - признак запроса виртуального прерывания, значение VIP = 1 устанавливается операционной системой в защищенном режиме, если внешний запрос прерывания поступает при выполнении программ пользователя (низший уровень привилегии CPL = 3) с запрещенным обслуживанием прерываний;

Ю-признак допустимости идентификации, возможность программного изменения значения ID указывает, что для данного процессора обеспечивается выполнение команды идентификации CPUID.

Особенности использования системных признаков рассматриваются в последующих разделах, где описываются соответствующие режимы работы процессора.

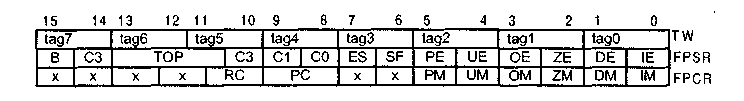

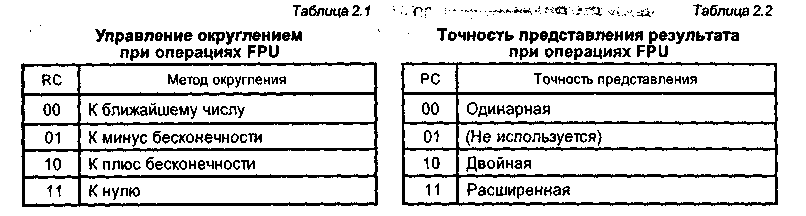

Регистры блока обработки чисел с плавающей точкой. В состав блока FPU процессоров Р6 входят восемь регистров данных R7-RO, регистр тегов TW, регистры управления FPCR и состояния FPSR, указатели команды FIP и данных FDP (рис. 2.4).

Регистры данных R7-RO содержат по 80 разрядов, разбитых на три поля: знак, порядок и мантисса, в соответствии с форматом представления чисел с плавающей точкой. Набор этих регистров организован в виде кольцевого стека, вершина которого определяется содержимым поля ТОР в регистре состояния FPSR (рис. 2.5). При выполнении различных операций над содержимым регистров данных расположение вершины стека изменяется.

Регистр тегов TW содержит 16-разрядное слово, включающее восемь двухбитных тегов tag7-tagO (см. рис. 2.5). Каждый тег (признак) характеризует содержимое соответствующего регистра данных R7-RO, указывая, является ли регистр пустым (незаполненным) или в нем размещается конечное число, нуль или неопределенное значение блока FPU (например, бесконечность). Значение тега позволяет проверить содержимое регистра, не проводя анализ хранящихся в нем данных.

Регистр состояния FPSR хранит 16-разрядное слово состояния FPU (см. рис. 2.5), отдельные биты и поля которого имеют следующее назначение:

В - признак занятости, включен в состав слова состояния для совместимости с младшими моделями процессоров; значение В дублирует значение ES-общего признака ошибки FPU;

ТОР- поле, указывающее вершину арифметического стека (см. рис. 2.4); содержит номер регистра данных FPU, являющегося в данное время верхним в стеке;

СЗ-СО- признаки результата, значение которых характеризует результат выполнения команды FPU;

ES- общий признак ошибки, принимает значение ES = 1, если установился хотя бы один из признаков ошибки операции FPU в шести младших разрядах FPSR; одновременно выдается сигнал FERR# = 0 на соответствующий внешний вывод процессора;

SF- признак переполнения стека, принимает значение SF = 1 при нарушении нормальной работы арифметического стека; используется совместно с признаком С1: если SF = 1, то значение С1 = 1 указывает на выход за верхнюю границу (переполнение) стека, а С1 = 0 -, на выход за нижнюю границу (антипереполнение) стека.

Младшие шесть разрядов содержимого FPSR хранят признаки ошибок, возникающих при выполнении команд FPU:

РЕ- признак нарушения точности;

UE- признак антипереполнения;

ОБ-признак переполнения;

ZE-признак деления на нуль;

DE-признак де нормализованного операнда;.

IE- признак неправильной операции.

Рис. 2.5. Форматы содержимого регистров TW, FPSR, FPCR

Регистр управления FPCR(pv\c. 2.5) содержит в младшем байте биты РМ, UM, ОМ, ZM, DM, IM, маскирующие соответствующие признаки ошибок, фиксируемых в регистре состояния FPSR. При единичном значении бита маски запрещается прерывание при возникновении соответствующей ошибки FPU. При нулевом значении бита маски установка соответствующего признака ошибки FPU вызывает прерывание процессора.

Старший байт в регистре управления FPSR определяет режим округления и точность представления результатов вычислений:

RC- поле управления округлением (табл. 2.1) определяет выбор одного из методов округления результата операций FPU;

PC- поле управления точностью (табл. 2.2) задает точность представления результатов арифметических операций FPU: одинарную (23 разряда мантиссы, 8 разрядов порядка), двойную (52 разряда мантиссы, 11 разрядов порядка) или расширенную (64 разряда мантиссы, 15 разрядов порядка).

Поле PC учитывается только при выполнении команд FADD, FSUB, FDIV, FMUL, FSQRT. Для остальных команд FPU используется расширенная точность.

Регистры -указатели команд FIP и данных FDP служат для идентификации команды, вызвавшей ошибку операции FPU. Содержимое этих регистров зависит от режима работы процессора. В реальном режиме при возникновении ошибки при выполнении команды FPU в эти регистры заносятся адрес и код операции данной команды, адрес использованного операнда. В защищенном режиме в них заносятся селекторы сегментов и относительные адреса команды и операнда. Эта информация используется подпрограммой обработки прерываний для выяснения причины ошибки FPU.

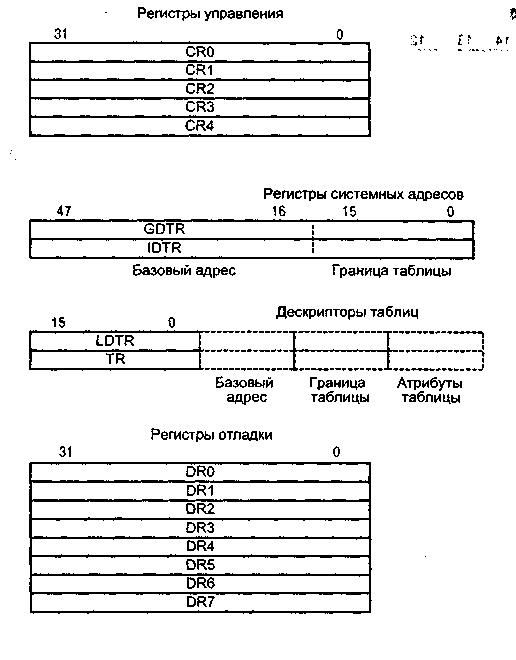

Системные регистры. В состав этой группы регистров (рис. 2.6) входят регистры управления CR4-CRO, регистры системных адресов GDTR, LDTR, IDTR, TR и регистры отладки DR7-DRO. Эти регистры доступны только в защищенном режиме для программ, имеющих максимальный уровень привилегий 0. Для доступа к системным регистрам используются специальные команды пересылки данных.

Регистры управления процессора имеют следующее назначение: \,.,,

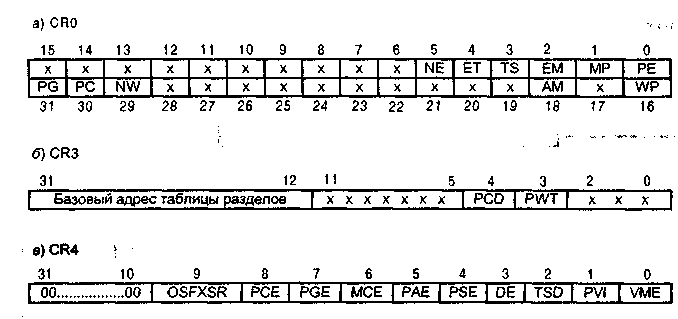

CRO-содержит биты, определяющие режим работы процессора (рис. 2.7, а);

CR2 - содержит 32- разрядный базовый адрес страницы, при обращении к которой зафиксирована ошибка при страничной адресации;

CR3 - содержит базовый адрес таблицы каталога страниц (20 старших битов), а также биты, управляющие загрузкой страниц в кэш-память данных (рис. 2.7, б);

CR4 - содержит биты, обеспечивающие расширение функциональных возможностей, реализуемое в процессорах Pentium и Р6 (рис, 2.7, в).

Форматы содержимого регистров CRO, CR3, CR4 приведены на рис. 2.7. Регистр CR1 в процессорах Р6 и более ранних моделях не используется (резервирован для последующих моделей) .

Рис. 2.6. Системные регистры процессоров Р6

Регистр управления CRO (рис. 2.7, а) содержит 11 битов, задающих режим работы различных блоков процессора:

РЕ - разрешение защиты, установка значения бита РЕ = 1 переводит процессор в защищенный режим, бит РЕ совместно с битом PG определяет режим работы процессора (см. табл.2.1);

МР - управление работой FPU, при установке значения МР = 1 и переключении задач (установка бита TS = 1) выборка команды WAIT (FWAIT) вызывает исключение типа #NM (отсутствие FPU);

ЕМ — эмуляция FPU, при установке значения ЕМ = 0 указывает на присутствие в системе блока FPU; установка значения ЕМ=0 вызывает при выборке команды FPU исключение типа #NM (отсутствие FPU), которое должно обеспечить обращение к подпрограмме, эмулирующей работу FPU;

TS - признак переключения задачи, принимает значение TS = 1 при каждом переключении задачи и проверяется при поступлении команд FPU: если TS = 1, то реализуется исключение типа #NM (отсутствие FPU);

ЕТ - в процессорах семейств Р6 и Pentium не используется (резервирован); в процессорах Intel 386,486 установка значения ЕТ = 1 указывает на включение в систему математических сопроцессоров Intel 387DX;

Рис. 2.7. Форматы содержимого регистров управления CRO (a), CR3 (б), CR4 (в)

N/Е — управление прерываниями FPU, при установке значения бита NE = 1 ошибки, возникающие при выполнении команд FPU, вызывают исключение типа #MF (ошибка FPU) при выборке следующей команды FPU; при установке значения NE = 0 ошибка FPU вызывает выдачу на соответствующий вывод процессора сигнала FERFW = 0, который поступает во внешний контроллер прерываний (этот способ обслуживания прерываний FPU реализуется в персональных компьютерах);

WP- защита от записи, при установке значения бита WP = 1 программам супервизора, имеющим уровень привилегий 0-2, запрещается запись на страницы пользователя, имеющие уровень привилегии 3; при значении WP = 0 такая запись разрешена;

AM - управление проверкой выравнивания, разрешает при установке значения бита AM = 1 проверку выравнивания адресов по границам слов (кратные двум) или двойных слов (кратные четырем) выборке операндов из памяти, если в регистре EFLAGS установлено значение бита АС = 1 и выполняемая программа имеет уровень привилегии 3 (программа пользователя);

N/W - запрещение записи в кэш-память, совместно с битом CD определяет режим работы внутренней кэш-памяти процессора;

CD-запрещение заполнения кэш-памяти, совместно с битом NW определяет режим работы внутренней кэш-памяти процессора;

PG - разрешение страничной трансляции адреса, при установке значения PG = 1 обеспечивает страничную адресацию памяти в защищенном режиме (табл. 2.3).

Отметим, что биты МР, ЕМ, TS влияют также на выполнение команд, реализуемых блоком ММХ. В табл. 2.4 указано, как реагирует процессор на поступление команд FPU или ММХ в зависимости от установленного значения этих битов.

Таблица