- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

2.3.5. Префиксные байты

Префиксы (табл. 2.25), имеющие разрядность один байт, оказывают влияние на выполнение команды, которой они предшествуют. Таким образом, они являются дополнительными программными средствами, управляющими работой процессора.

Префикс SEG определяет выбор сегмента CS, DS, ES, FS, GS или SS для адресации операнда в выполняемой команде. При отсутствии этого префикса сегмент выбирается по умолчанию согласно табл. 2.8. Префикс действует, если команда выбирает операнд из памяти; в противном случае он не учитывается.

Префиксы AS, OS позволяют при выполнении последующей команды изменять разрядность адреса и операнда в соответствии с табл. 2.14.

Префикс блокировки LOCK, который используется для организации работы мультипроцессорных систем, вызывает установку на выходе LOCK# процессора низкого потенциала, запрещающего другим устройствам системы (процессорам) обращаться к системной шине в течение времени выполнения последующей команды. Префикс LOCK может предшествовать только командам ADD, XADD, ADC, SUB, SBB, AND, OR, XOR, DEC, INC, NEG, NOT, ВТ, ВТС, BTR, BTS, CMPXCHG и XCHG. Использование префикса LOCK перед другими командами вызовет прерывание с номером Ne = 6 (#UD - неразрешенный код операции).

Префиксы повторения REP, REPE/REPZ и REPNE/REPNZ применяются только с командами операций над строками. Префикс REP используется с командами INS, OUTS, MOVS и STOS и вызывает их повторение до тех пор, пока содержимое регистра ЕСХ (или СХ)>0. С командами CMPS и SCAS используются префиксы REPE или REPNE. Префикс REPE (возможная форма REPZ) обеспечивает повторение команды до тех пор, пока значение признака ZF = 0, т. е. поступают одинаковые символы. При поступлении различных операндов устанавливается значение ZF = 1, и выполнение команды прекращается. Если все операнды в строках одинаковы, то команда выполняется до получения ЕСХ(СХ) = 0, т. е. до конца строки. Префикс REPNE (возможная форма REPNZ) вызывает повторение команды, пока значение признака ZF = 0 (сравниваемые символы не одинаковы). Выполнение команды прекращается либо при поступлении одинаковых символов, когда устанавливается ZF = 1, либо при получении ЕСХ (СХ) = 0 (конец строки), если в строке отсутствуют одинаковые признаки.

2.4. Система команд: операции над числами с плавающей точкой

К данному классу относятся команды, которые осуществляют операции над вещественными, целыми и двоично-десятичными числами, представленными в формате с плавающей точкой. Такое представление позволяет значительно расширить диапазон обрабатываемых чисел. Ниже дается перечень команд над данными с плавающей точкой, разбитых на функциональные группы. Мнемокод каждой команды начинается с префикса F (float-плавающий). Для команд, оперирующих с целыми числами, за буквой F идет буква I, с двоично-десятичными числами - буква В.

Пересылка данных

FLD - Загрузка вещественного числа

FILD - Загрузка целого числа

FBLD - Загрузка двоично-десятичного числа

FST - Запись в память вещественного числа

FIST —Запись в память целого числа

FSTP - Запись в память вещественного числа с выталкиванием из стека

FISTP - Запись в память целого числа с выталкиванием из стека

FBSTP — Запись в память двоично-десятичного числа с выталкиванием из стека

FCMOVcc- Условная пересылка данных между регистрами FPU

FXCH - Обмен данными между регистрами стека Г

FLDZ Загрузка нуля + 0.0

FLD1 - Загрузка единицы + 1.0

FLDPI - Загрузка р (пи)

FLDL2T - Загрузка Iog210 (основание log = 2) FLDL2E-Загрузка Iog2e (основание log = 2) FLDLG2 - Загрузка Ig 2 (основание log =10)

FLDLN2 - Загрузка In 2 (основание log = e)

Арифметические операции

FADD - Сложение вещественных чисел

FADDP - Сложение вещественных чисел с выталкиванием из стека FIADD-Сложение целых чисел

FSUB-Вычитание вещественных чисел

FSUBP - Вычитание вещественных чисел с выталкиванием из стека FSUBR- Обратное вычитание вещественных чисел

FSUBRP - Обратное вычитание вещественных чисел с выталкиванием из стека

FISUB - Вычитание целых чисел

FISUBR-Обратное вычитание целых чисел

FMUL-Умножение вещественных чисел

FMULP - Умножение вещественных чисел с выталкиванием из стека

FIMUL-Умножение целых чисел FDIV-Деление вещественных чисел

FDIVP-Деление вещественных чисел с выталкиванием из стека

FDIVR-Обратное деление вещественных чисел

FDIVRP - Обратное деление вещественных чисел с выталкиванием из стека

FIDIV-Деление целых чисел

FIDIVR- Обратное деление целых чисел

FPREM - Нахождение частичного остатка от деления

FPREM1 - Нахождение частичного остатка в стандарте IEEE 754

FSQRT-Вычисление квадратного корня

FABS - Получение абсолютного значения . FCHS-Изменение знака числа

Операции сравнения

FCOM - Сравнение вещественных чисел

FCOMP - Сравнение вещественных чисел с выталкиванием из стека

FCOMPP - Сравнение вещественных чисел с двойным выталкиванием из стека

FCOMI - Сравнение вещественных чисел

FCOMIP -Сравнение вещественных чисел

FICOM - Сравнение целых чисел

FICOMP - Сравнение целых чисел с выталкиванием из стека

FUCOM - Сравнение неупорядоченных чисел

FUCOMP - Сравнение неупорядоченных чисел с выталкиванием из стека

FUCOMPP - Сравнение неупорядоченных чисел с двойным выталкиванием из стека

FUCOMI -Сравнение неупорядоченных чисел с установкой признаков в регистре EFLAGS

FUCOMIP-Сравнение неупорядоченных чисел с установкой признаков в регистре EFLAGS

и выталкиванием из стека

FTST - Сравнение с нулем

FXAM-Анализ вещественного числа

Рис. 2.16. Форматы представления чисел, обрабатываемых блоком FPU

Двоично-десятичные целые числа в формате ДД (рис. 2.16, г) представляются в упакованной форме и содержат 18 тетрад, каждая из которых соответствует одному десятичному разряду. Для представления знака S используется старший разряд старшего байта (бит 79), в остальных разрядах этого байта устанавливается нулевое значение. Таким образом, формат ДД обеспечивает представление целых чисел в диапазоне ±1018. Неопределенность в этом формате представляется числом 1111 1111 1111 1111 хх... хх, в котором два старших байта содержат единицу во всех разрядах, а все остальные разряды (восемь младших байтов) имеют произвольное значение ох.

Вещественные числа в каждом из трех форматов их представления ОТ, ДТ, Р. (рис. 2.16, д-ж) содержат три поля: поле знака S (старший бит числа), поле порядка и поле мантиссы. Вещественные числа одинарной точности (формат ОТ, 32-разрядные операнды) имеют 23-разрядную мантиссу и 8-разрядный порядок; числа двойной точности (формат ДТ, 64-разрядные операнды) имеют 52-разрядную мантиссу и 21 -разрядный порядок; числа расширенной точности (формат РТ, 80-разрядные операнды) имеют 64-разрядную мантиссу и 15-разрядный порядок. Двоичное число без знака Е, содержащееся в поле порядка, указывает смещенный порядок. Истинный порядок числа будет равен (Е-Р), где Р - смещение, величина которого зависит от формата: Р = 127 для ОТ, Р = 1023 для ДТ, Р = 16383 для РТ. Мантисса записывается в нормализованном виде (за исключением особых случаев): 1 ,ххх...х. При этом стоящая перед точкой единица в форматах ОТ, ДТ не указывается в поле мантиссы. В формате РТэта единица содержится в старшем разряде мантиссы: тбЗ = 1. .

Таким образом, значения вещественных чисел X определяются выражениями:

X = (-1) S х (1. m22 m21...mO) x 2 Е-127-для формата ОТ; X = (-1) S х (1. гп52 m51 ...тО) х 2 Е-1023 - для формата ДТ; X = (-1) S х (т63.т62 тО) х2 Е-16383-для формата РТ;

где S-знак мантиссы;...mlmO - разряды мантиссы.

Использование смещенного порядка Е позволяет упростить операцию сравнения вещественных чисел. При этом в большинстве случаев достаточно сравнить значения Е. Диапазон представляемых вещественных чисел составляет:

±10 ±38 –для формата ОТ, ±10 ±308-для формата ДТ, ± 10 ±4932 - для формата РТ.

Следует отметить, что диапазон чисел, представляемых в форматах ОТ, ДТ, вполне достаточен для решения практически любых задач. Поэтому данные, поступающие на обработку в FPU, обычно представлены в этих форматах. Однако в процессе обработки чисел FPU использует формат РТ, позволяющий избежать потери точности результата при многократном выполнении операций над вещественными числами.

Различные форматы представления вещественных чисел даны в табл. 2.26. Числа с нулевым значением мантиссы и максимальным порядком отведены для представления бесконечных значений. При этом различаются значения +L и - L, которые связаны соотношением +L> - L (афинная арифметика). Для нуля так же введены два значения:+0 и - 0. При выполнении операций знак нуля устанавливается согласно правилам формирования знаков при соответствующих операциях, например: +X/+L = +0, +Х/ - L = - 0 и т. д.

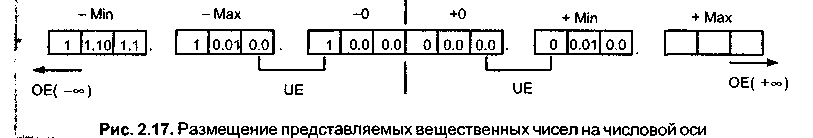

В табл. 2.26 указаны максимальные (±Мах) и минимальные (±Min) десятичные значения представляемых вещественных чисел. При получении результатов, превышающих максимальное положительное число (+Мах), или меньших минимального отрицательного числа (- Min) в регистре FPSR устанавливается флаг переполнения ОЕ = 1. В этом случае либо реализуется прерывание, либо результатом операции является бесконечность (+L или - L). Если полученный результат меньше положительного минимального нормализованного числа (+Min) или больше отрицательного максимального нормализованного числа (- Мах), то в регистре FPSR устанавливается флаг антипереполнения UE = 1. В таком случае FPU может перейти к обработке денормализованных чисел. При этом диапазон представления чисел расширяется в сторону нуля, и точность вычислений увеличивается. На рис. 2.17 показано размещение представляемых вещественных чисел на числовой оси и условия формирования признаков ОЕ, UE.

Специальные коды введены для представления нечисловых операндов NAN (Not-A-Number, не числа). Эти коды (см. табл. 2.26) имеют единичные значения всех разрядов порядка и произвольные значения знака и мантиссы (за исключением нулевого значения мантиссы, используемого для представления бесконечности). Различаются два типа не чисел: SNAN, имеющие нулевое значение старшего (после точки) разряда мантиссы; QNAN, имеющие единичное значение старшего разряда.

He-числа, выбираемые из памяти в качестве операндов FPU, определяются как SNAN. Если не число является результатом выполняемой операции FPU (например, извлечение квадратного корня из отрицательного числа, команда SQRT), то оно будет иметь тип QNAN. Отметим, что неопределенность является частным случаем не числа QNAN.

В табл. 2.26 представлены все форматы чисел, поддерживаемые процессором. Однако существует множество чисел, не вошедших в эти форматы. В формате РТ к ним относятся: ненормализованные числа, имеющие ненулевое значение порядка и мантиссу с нулевым значением старшего разряда; псевдоненормализованные числа, имеющие нулевой порядок и мантиссу с единичным значением старшего разряда; ncesfloNAN и псевдобесконечность, имеющие единичные значения всех разрядов порядка и мантиссу с нулевым значением старшего разряда. Такие варианты представления чисел называются неподдерживаемыми (unsupported) формами, так как их появление вызывает прерывание работы процессора.

При описании команд FPU выбираемые из памяти вещественные числа обозначаются символами m32real (число в формате ОТ), m64real (число в формате ДТ), mSOreal (число в формате РТ). Для обозначения целых чисел используются символы ml 6int (число в формате ЦС), m32int (число в формате КЦ), m32 int (число в формате ДЦ). Двоично-десятичные числа обозначаются символом mSObcd.

. 2.4.2. ВЫПОЛНЕНИЕ ОПЕРАЦИЙ

Описанные в предыдущем разделе форматы применяются для представления целых, двоично-десятичных и вещественных чисел в памяти. При обработке чисел в FPU используется только расширенный формат РТ. При вводе в FPU числа, представленные в форматах ЦС, КЦ, ДЦ, ДД, ОТ, ДТ, преобразуются в формат РТ. При записи результата из FPU в память производится, в случае необходимости, обратное преобразование.

Команды FPU имеют общий формат, показанный на рис. 2.11. При выполнении операций в качестве одного из операндов всегда используется содержимое ST(0) - регистра данных FPU, являющегося вершиной стека. Физический номер этого регистра определяется полем ТОР в регистре состояния FPSR (см. рис. 2.4), содержимое которого изменяется при выполнении ряда команд. Таким образом осуществляется заполнение или освобождение регистров арифметического стека. Второй операнд при выполнении двухоперандных команд FPU выбирается из памяти или из i-ro регистра данных ST(i), входящего в состав арифметического стека.

Форматы команд FPU показаны на рис. 2.18. Каждая из этих команд начинается 5-битовым полем ESC =11011, поля ОРС определяют выбор одной из возможных операций FPU. При обращениях к памяти возможно использование всех способов адресации. При этом после байта MODR/M могут следовать байт SIB, обеспечивающей масштабирование адреса, байты d8, d16 или d32, задающие необходимое смещение DISP (см. рис. 2.18, а). При регистровой адресации (MOD =11) поле R/M задает адрес i арифметического регистра ST(i), из которого выбирается операнд (см. рис. 2.18, б). В качестве i используется не физический номер регистра, а его номер относительно вершины стека.

При выполнении операций FPU контролирует точность представления чисел и производит в случае необходимости округление результата. Эти процедуры осуществляются в соответствии со значениями полей PC, RC в регистре управления FPCR.

Значение поля PC (см. табл. 2.2) определяет точность результатов арифметических операций над вещественными числами: сложения, вычитания, умножения деления, извлечения квадратного корня (команды FADD, FSUB, FSUBR, FMUL, FDIV, FDIVR, FSQRT). На результаты других операций FPU значение поля PC не влияет. При PC = 11 результат представляется с обычной для FPU расширенной точностью (64 значащих разряда мантиссы), которая обеспечивается используемым форматом РТ. При PC = 00 или 10, реализуется одинарная (23 значащих разряда мантиссы) или двойная (52 значащих разряда мантиссы) точность представления чисел. В этом случае при получении результатов с более высокой точностью производится их округление. Значение PC = 01 не используется (резервировано).

Значение поля RC определяет способ округления результата операций FPU до заданной точности (см. табл. 2.1). При RC = 00 реализуется обычный способ округления. При RC = 01 или 10 выполняется округление в сторону меньших или больших чисел. При RC = 11 осуществляется обнуление лишних разрядов мантиссы. Поле RC влияет на результаты арифметических операций (кроме операций, определяемых командами FPREM, FPREMI, FXTRACT, FABS, FCHS), операций вычисления трансцендентных функций и операций передачи, выполняемых по командам FST, FSTP, FIST.

При выполнении операций FPU контролируется шесть видов ошибок:

#1 - недействительная операция;

#D - поступление денормализованного операнда;

#Z-деление на нуль;

#О - переполнение;

#U - антипереполнение;

#Р - неточный результат.

При обнаружении ошибки устанавливается единичное значение соответствующего признака IE, DE, ZE, ОЕ, UE, РЕ в регистре состояний FPSR. В регистре управления FPCR содержатся маски этих ошибок IM, DM, ZM, ОМ, UM, РМ: при нулевом значении маски соответствующая ошибка вызовет прерывание программы (исключение), при единичном значении маски процессор продолжает выполнение программы.

Признак неточного результата РЕ = 1 устанавливается, если результат операции не может быть точно представлен в заданном командой формате. Если установлена маска РМ = 1, то процессор продолжает программу без прерывания. В этом случае производится округление результата в соответствии со значением поля RC в регистре FPCR (см. рис. 2.6).

Признак антипереполнения UE = 1 устанавливается, если результат слишком мал для представления нормализованным числом, т. е. меньше значений +Min для положительных или больше значений - Мах для отрицательных нормализованных чисел (см. табл. 2.26). Если установлена маска UM = 1, то процессор продолжает программу без прерывания, а результат представляется денормализованным числом.

Признак деления на нуль ZE = 1 устанавливается, когда делимое является конечным числом, отличным от нуля, а делитель равен нулю. Если установлена маска ZM = 1, то выполнение программы продолжается без прерывания, в качестве результата деления выдается код бесконечности. Знак результата определяется в зависимости от знаков операндов в соответствии с правилами деления.

Признак денормализованного операнда DE = 1 устанавливается, если денормализован хотя бы один из операндов. Если установлена маска DM =1, то процессор оперирует с денормализованным операндом, как с нормализованным.

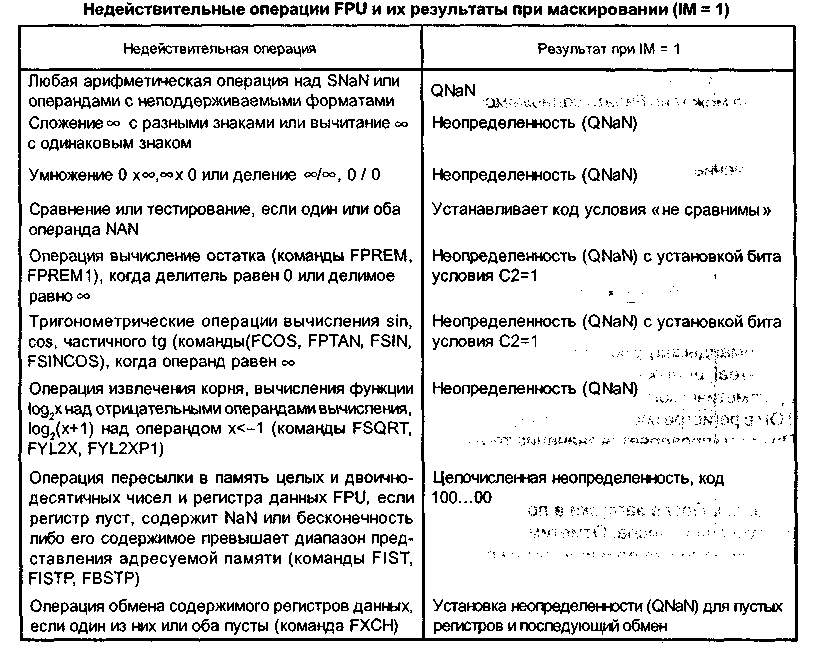

Признак недействительной операции 1Е=1 устанавливается при извлечении содержимого из пустого регистра или загрузки в заполненный регистр, выполнении действий с не числами SNaN, QNaN, извлечении квадратного корня из отрицательного числа, делении L/L и ряде других операций, указанных в табл. 2.27. Если установлена маска IM = 1, то выполнение программы продолжается без прерывания, а результат недействительной операции определяется согласно табл. 2.27.

При выполнении операций FPU контролируется переполнение или антипереполнение арифметического стека. Переполнение фиксируется, если команда пытается произвести загрузку в заполненный регистр стека. При этом в регистре FPSR устанавливаются признак SF = 1 и бит условия С1 = 1. Антипереполнение фиксируется, если команда пытается считать операнд из пустого регистра стека. В этом случае устанавливаются значения SF = 1 и С1 = 0. Значение SF = 1 указывает на выполнение недействительной операции и вызывает установку признака 1Е=1. Если флаг IE маскирован (IM = 1), то результатом операций, вызвавших переполнение или антипереполнение стека, будет загрузка или считывание не числа QNAN.

Если хотя бы один из признаков IE, DE, ZE, OE, UE, РЕ установлен в состояние «1» и не маскирован, то общий признак ошибки устанавливается в состояние ES = 1 и формируется сигнал ошибки FERR# = 0 на внешнем выводе процессора. Если в регистре управления CRO установлено значение бита NE = 1, то в этом случае непосредственно перед следующей командой FPU реализуется исключение типа #MF («ошибка FPU»).

При значении NE = 0 процедура обработки прерывания вызывается командой INTn, формируемой внешним контроллером прерываний. Получив сигнал FERR#=0, этот контроллер должен подать сигнал IGNNE# = 1 на соответствующий вход процессора. Данный сигнал вызывает остановку процессора непосредственно перед следующей командой FPU или WAIT. Эта остановка продолжается до поступления от контроллера прерываний команды INTn. Если на входе IGNNE# поддерживается состояние «О», то процессор продолжает выполнение программы, игнорируя ошибки FPU.

Процедуры обслуживания исключений, вызываемых FPU, могут использовать для выявления причины ошибок содержимое регистров FIP и FDP - указателей команд и данных, которое выводится из процессора с помощью команд управления FSTENV, FSAVE. В регистр FIP заносится адрес текущей команды FPU и 11 разрядов ее кода (два первых байта без кода ESC), если эта команда не входит в группу команд управления. Если команда выбирает операнд из памяти, то в регистр FDP заносится адрес операнда, в противном случае разряды регистра устанавливаются в неопределенное состояние. Когда выполнение команды вызывает немаскированное прерывание вследствие возникновения какой-либо из вышеуказанных ошибок, регистры FIP и FDP содержат информацию об этой команде и операнде, которая может быть использована для анализа причин ошибки. Так как команды управления не изменяют содержимое FIP и FDP, то процедура обработки ошибок FPU с помощью этих команд может выбирать содержимое FIP, FDP для проведения такого анализа.

Необходимо отметить влияние битов ЕМ, TS, МР регистра управления CRO на выполнение команд FPU и WAIT/FWAIT. При TS = 1 или ЕМ = 1 поступление команд FPU вызовет исключение типа #NM («FPU недоступен»). Команда WAIT/FWAIT вызывает это исключение только при TS = МР = 1.