- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

2.3.1. Команды управления программой

К этой группе относится большое число команд, которые для удобства описания разобьем на несколько подгрупп.

Команды безусловной передачи управления (табл. 2.21) осуществляют безусловный переход (JMP), вызов подпрограммы (CALL) и возврат из подпрограммы (RET).

Если передача управления происходит внутри сегмента (NEAR - ближняя передача), то содержимое регистра CS не меняется и реализуется переход к команде, расположенной в текущем сегменте кодов. Команды JMP и CALL с относительной адресацией производят увеличение содержимого регистра IP или EIP на указанную в команде величину ге!8,16 или 32, которая воспринимается как число со знаком. При вычислении нового относительного адреса команды (IP, EIP)+(rel8,16,32) возникающий перенос игнорируется, поэтому полученный адрес остается в пределах текущего сегмента кодов. Команды JMP и CALL с косвенной адресацией загружают в IP или EIP содержимое регистра или ячейки памяти г/гл(16,32), адресуемых байтом MODR/M. Команда CALL перед этим заносит в стек текущее значение IP или EIP, которое является относительным адресом следующей команды программы. При поступлении команды RET производится восстановление из стека содержимого IP, EIP, необходимого для вычисления адреса возврата.

При передаче управления между сегментами (FAR - дальняя передача) меняется не только содержимое регистра EIP или IP, но и базовый адрес сегмента, определяемый содержимым регистра сегмента кодов CS. При выполнении команд JMP и CALL с непосредственной адресацией в качестве операнда ptr16:16 или ptr16:32 в команде задается 16-разрядное число ptr16 - новое содержимое регистра CS, и ptr16 или ptr32 - новое содержимое регистра IP или EIP. При косвенной адресации с помощью байта MODR/M адресуются ячейки памяти гл(16:16, 16:32), в которых последовательно располагается новое содержимое IP или EIP и 16-разрядный селектор, загружаемый в регистр CS. Отметим, что в этом случае не производится адресация к регистрам, т.е. в байте MODR/M должно быть установлено значение поля mod = 11.

Для возврата из подпрограммы используется команда RET, которая восстанавливает из стека содержимое регистров EIP или IP и CS (при выполнении межсегментных переходов). Если команда RET содержит непосредственный операнд im16, то после извлечения из стека содержимого регистров EIP (IP) и CS (при межсегментном переходе) содержимое указателя стека ESP (или SP) увеличивается на величину im16. Таким образом, из стека исключается число ячеек памяти, равное im16. Эта команда производит

очистку сегмента стека от использованных в программе параметров, если они не требуются для продолжения выполнения основной программы.

Команды условных переходов Jcc выполняют переходы только в пределах текущего сегмента кодов с использованием относительной адресации. При выполнении заданного условия производится переход к команде, относительный адрес которой в сегменте кодов равен (1Р+ге18,16) или (EIP+rel8,32), где ге!8,16 или 32 представляете-, 16- или 32-разрядное смещение со знаком. Таким образом, допускаются переходы к ячейкам памяти, размещенным в текущем сегменте кодов перед командой Jcc или после нее. Возникающие при вычислении этих относительных адресов переносы не учитываются. Имеется две модификации команд Jcc: короткие и длинные переходы. Первая модификация использует 8-разрядное смещение (ге!8), вторая модификация использует 16- или 32-разрядное смещение (ге116 или ге!32) в зависимости от разрядности адреса, устанавливаемой режимом работы микропроцессора или соответствующим префиксом перед командой Jcc.

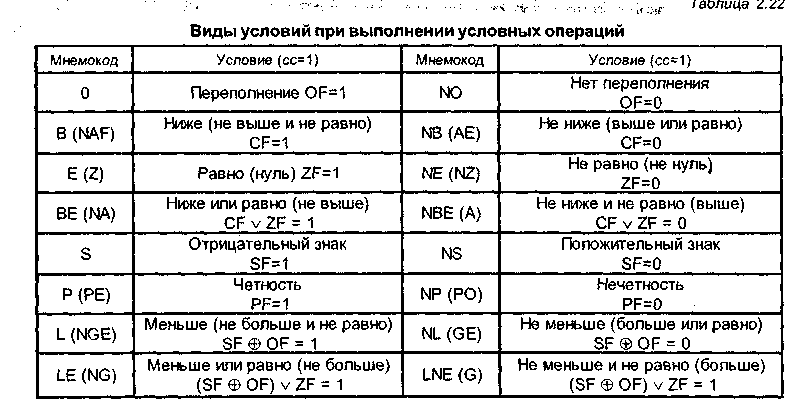

В подгруппу входят 16 команд, различающихся условием выполнения перехода ее (табл. 2.22). Соответствующие мнемокоды условий добавляются к букве J (JUMP), образуя мнемокод команды, например: J+O=JO- мнемокод команды условного перехода по переполнению. Условие определяется значением отдельных признаков или их комбинацией.

В качестве условия часто используется относительное значение двух операндов, определяемое с помощью команды сравнения СМР. Равенство операндов определяется значением признака нуля ZF после команды СМР: равно E/Z (результат равен 0); не равно NE/NZ (результат не равен 0). Если сравниваются беззнаковые операнды, то соотношение их значений (выше-ниже-равно) определяют условия:

ниже (не выше и не равно) (<) В/МАЕ;

не ниже (выше или равно) (>=) NB/AE;

ниже или равно (не выше) (<=) BE/NA;

не ниже и не равно (выше) (>) NBE/A.

Отметим, что команды JB/JNAE и JNB/JAE эквивалентны командам переходов по наличию переноса JC или отсутствию переноса JNC.

Если сравниваются операнды со знаком, то соотношение между ними (больше-меньше - равно) определяют условия:

меньше (не больше и не равно) (<) < L/NGE;

не меньше (больше или равно) (>=) NL/GE;

меньше или равно (не больше) (<=) LE/NG;

не меньше и не равно (больше) (>) NLE/G.

Команды организации циклов осуществляют условный переход в зависимости от значения содержимого регистра ЕСХ (или СХ), которое автоматически уменьшается на единицу (декремент) при поступлении команд этой подгруппы: JECXZ, (JCXZ), LOOP, LOOPE/LOOPZ, LOOPNE/LOOPNZ. Таким образом, регистр ЕСХ используется в качестве счетчика циклов.

Команды LOOPE/LOOPZ, LOOPNE/LOOPNZ аналогичны команде LOOP, но используют дополнительные условия для повторения цикла. Команда LOOPE/LOOPZ обеспечивает выход из цикла при получении ненулевого результата, т. е. при установке ZF = 0, до выполнения заданного числа циклов п = (ЕСХ). Если в каждом цикле реализуется нулевой результат, то выполняется п = (ЕСХ) циклов, как в команде LOOP. Команда LOOPNE/LOOPNZ прекращает выполнение циклов при получении нулевого результата, т. е. при установке ZF = 1.

В зависимости от режима работы процессора и наличия префиксов изменения разрядности адреса при выполнении команд организации циклов вместо регистров EIP, ЕСХ могут использоваться IP, СХ. При этом вместо мнемокода команды JECXZ используется JCXZ.

Команды прерываний обеспечивают переход к одной из 256 программ обслуживания исключений и прерываний. При этом текущее содержимое регистров IP (EIP), CS и FLAGS (EFLAGS) заносится в стек. Каждая из программ обработки соответствует определенному типу исключения или прерывания, номер которого определяется 8-разрядным непосредственным операндом im8, задаваемым во втором байте команды INT. Вызов соответствующей программы обслуживания производится с помощью таблицы, в которой содержатся векторы исключений (прерываний) Ve - адреса первых команд программ обслуживания. Номер вектора Ne = im8 указывает его положение в таблице векторов. Каждый вектор задает необходимое содержимое CS и EIP (IP), загрузка которого в эти регистры обеспечивает переход к выполнению первой команды программы обслуживания. Обращение к таблице векторов Ve производится процессором в зависимости от режима его работы. В защищенном режиме при переходе к программе обслуживания прерываний в стеке сохраняется также заданное число 16- или 32-разрядных параметров из вершины стека, которые при выполнении команд прерываний переносятся в стек программы обслуживания прерываний для использования или сохранения.

Первые 32 вектора прерываний зарезервированы для обслуживания исключительных ситуаций (ошибки, отказы и т. п.), возникающих при выполнении программы. Для трех из этих ситуаций предусмотрены отдельные однобайтные команды INT3, INTO и UD2.

Команда INT3 имеет вектор с номером Ne = 3 (исключение типа #ВР - останов в контрольной точке) и используется для установки контрольных точек в процессе отладки программы. Программа, вызываемая этой командой, обеспечивает останов процессора и выдачу пользователю необходимой информации о его текущем состоянии. Команда INTO проверяет значение признака OF и вызывает соответствующую программу обслуживания, если OF = 1, т. е. результат предыдущей операции (число со знаком) вышел за пределы разрядной сетки. Эта команда обращается к вектору прерываний с номером Ne = 4 (исключение типа #OF - переполнение разрядной сетки). Команда UD2, введенная в процессорах семейства Р6, реализует прерывание с номером Ne = 7 (#UD - недействительный код операции). Эта команда используется для вызова программы обслуживания прерывания типа #UD в процессе выполнения текущей программы.

Команда IRET обеспечивает возврат из подпрограммы обслуживания прерывания путем извлечения из стека и возвращения в регистры содержимых EIP или IP, CS, EFLAGS или FLAGS, соответствующих прерванной процедуре.

Дополнительные команды вызова системных процедур SYSENTER, SYSEXIT введены в процессорах Pentium II и последующих моделях данного семейства. Эти команды используют специальные модельно-специфические регистры (MSR), которые имеют имена SYSENTER_CS_MSR (адрес 174h), SYSENTER_ESP_MSR (адрес 175h), SYSENTER_EIP_MSR (адрес 176h). В эти регистры с помощью команд WRMSR записываются адреса ячеек памяти, содержимое которых обеспечивает переход к определенной системной программе, имеющей максимальный уровень привилегии DPL - 0. При поступлении команды SYSENTER из этих ячеек памяти производится загрузка нового содержимого: в регистр CS - из ячейки, адресуемой регистром SYSENTER_CS_MSR, в регистр EIP-ячейки, адресуемой SYSENTER_EIP_MSR, в регистр SS-из ячейки, адрес которой равен (SYSENTER_CS_MSR) + 8, в регистр ESP - из ячейки, адресуемой SYSENTER_ESP_MSR. Таким образом, обеспечивается переход к новым сегментам команд и стека. При этом не переходе к программе обслуживания прерываний в стеке сохраняется также заданное число 16- или 32-разрядных параметров из вершины стека, которые при выполнении команд прерываний переносятся в стек программы обслуживания прерываний для использования или сохранения. вложенности текущей процедуры. Этот уровень определяет количество указателей (относительных адресов) предыдущих стековых кадров, помещаемых в стек перед образуемым стековым кадром. При поступлении команды ENTER содержимое регистра ЕВР (или ВР) посылается в стек, а последнее значение указателя стека ESP (или SP) заносится в ЕВР (или ВР), после чего содержимое ESP (или SP) уменьшается на величину im8, образуя стековый кадр заданного размера. Однако, если второй непосредственный байт 18 > 0, то после содержимого ЕВР (или ВР) в стек заносится п = (18) слов (32- или 16-разрядных) из последовательно расположенных 32- или 16-разрядных ячеек памяти, адрес которых задается содержимым регистра ЕВР (или ВР), последовательно уменьшаемым на 4 (или 2).

При выполнении команды выхода из процедуры LEAVE содержимое регистра ЕВР (или ВР) заносится в регистр ESP (или SP), восстанавливая значение указателя стека, которое было до входа в процедуру с помощью предыдущей команды ENTER. Затем из стека извлекается старое значение ЕВР (или ВР). Таким образом, производится подготовка к возврату в предыдущую процедуру. Обычно команда LEAVE является последней в программе реализации вызванной процедуры, и следующая за ней команда RET обеспечивает возврат к выполнению предыдущей процедуры.