- •Предисловие

- •Введение

- •1. Системный анализ задачи - выделяются процессы и функции, реализация которых будет возложена на мк или ип.

- •Алгоритмизация процессов и функций - разрабатываются алгоритмы решения задачи.

- •Области использования мк

- •Глава 1основы микропроцессорной техники

- •1.1. Классификация микропроцессоров, основные варианты их архитектуры и структуры

- •1.2. Общая структура и принципы функционирования микропроцессорных систем

- •1.3. Система команд и способы адресации операндов

- •Начиная с младшего байта («Little-Endian»);

- •Начиная со старшего байта («Big-Endian»).

- •1.4. Интерфейсы микропроцессорных систем

- •1.4.1. Основные понятия

- •1.4.2. Магистраль vme

- •Verbs находит широкое применение в:

- •VmEbus обеспечивает наилучшее соотношение цена - производительность для системы в целом и предоставляет практически неограниченные возможности наращивания всех ресурсов.

- •1.5. Шина usb

- •На их основе

- •2.1. Структура и функционирование процессоров intel p6

- •2.1.1. Суперскалярная архитектура и организация конвейера команд

- •2.1.2. Режимы работы процессора и организация памяти

- •2.1.3. Регистровая модель

- •1. Функциональные основные регистры:

- •Iopl -уровень привилегий ввода/вывода, задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода;

- •2.3 Режимы работы процессора

- •2.1.4. Внутренняя кэш-память

- •8 Зон по 64 Кбайт, занимающих диапазон адресов 0-7fffFh (512 Кбайт);

- •16 Зон по 16 Кбайт, занимающих диапазон адресов 80000h-8ffffh (256 Кбайт);

- •8 Зон размером от 4 Кбайт до максимального размера физической памяти, которые могут размещаться в любой позиции адресного пространства.

- •2.1.5. Форматы команд и способы адресации

- •Содержимого базового регистра евр (вр) или евх (вх);

- •Содержимого индексного регистра esi (si) или edi (di);

- •Disp команды (см. Рис. 2.11).

- •2.2. Система команд: операции над целыми числами

- •Пересылка данных и адресов

- •Xchg - Обмен между регистрами или памятью и регистром

- •Xlat-Преобразование кодов

- •Imul-Знаковое (целочисленное) умножение аам- ascii-коррекция результата умножения

- •Idiv-Знаковое (целочисленное) деление

- •2.2.1. Команды пересылки

- •2.2.2. Команды арифметических операций

- •2.2.3. Команды логических операций и сдвигов

- •2.2.4. Команды битовых и байтовых операций

- •2.2.5. Команды операций со строками символов

- •2.3. Система команд: операции управления

- •Управление программой

- •Прерывания

- •Int3 - Прерывание в контрольной точке

- •Iret-Возврат из подпрограммы обслуживания прерывания

- •2.3.1. Команды управления программой

- •2.3.3. Команды организации защиты памяти

- •2.3.4. Команды управления процессором

- •2.3.5. Префиксные байты

- •2.4. Система команд: операции над числами с плавающей точкой

- •2.4.3. Команды пересылки данных

- •2.4.4. Команды арифметических операций

- •2.4.6. Команды специальных операций

- •2.4.7. Команды управления fpu

- •Команды преобразования

- •Арифметические команды

- •Inub'- Нахождение меньшего значения (беззнаковые байты) Команды сравнения

- •Команды логических операций

- •2.5.1. Форматы представления данных и выполнение операций

- •2.5.2. Команды пересылки и преобразования данных

- •1 2.5.3. Команды арифметических операций '

- •2.5.4. Команды логических операций и сдвигов

- •2.5.5. Команды сравнения и нахождения максимума/минимума

- •2.6. Система команд: операции sse

- •Команды пересылки данных

- •Команды преобразования данных

- •Арифметические команды

- •Команды нахождения максимума и минимума.

- •Команды преобразования формата чисел.

- •Команды управления

- •2.6.1. Форматы представления данных и выполнение операций

- •2.6.2. Команды пересылки и преобразования данных

- •2.6.3. Команды арифметических операций

- •2.6.6. Команды преобразования формата чисел

- •2.6.7. Команды управления

- •2.6.8. Команды пересылки данных с управлением кэшированием

- •2.7. Работа процессора в защищенном и реальном режимах

- •2.7.1. Сегментация памяти в защищенном режиме

- •2.7.2. Страничная организация памяти

- •2.7.3. Защита памяти

- •2.7.4. Поддержка многозадачного режима

- •2.7.5. Реализация режима виртуального 8086 (v86)

- •2.7.6. Функционирование процессора в реальном режиме

- •2.8. Реализация прерываний и исключений. Обеспечение тестирования и отладки

- •2.8.1. Виды прерываний и исключений, реализация их обслуживания

- •2.8.2. Причины возникновения исключений

- •2.8.3. Средства обеспечения отладки

- •2.8.4. Реализация тестирования и контроля функционирования

- •2.9. Risc-микропроцессоры и risc-микроконтроллеры семейств powerpc (мрс60х, мрс50х)

- •2.9.1. Risc-микропроцессоры семейства мрс60х (powerpc)

- •I (invalid) - недостоверное (аннулированное) содержимое строки.

- •2.9.2. Risc-микроконтроллеры семейства мрс5хх ( power pc)

- •3.1. Общие принципы организации кэш-памяти

- •3.1.1. Понятия тега, индекса и блока

- •3.1.2. Механизм кэш-памяти с прямым отображением данных

- •3.1.3. Механизм кэш-памяти

- •3.1.4. Обновление информации в кэш-памяти

- •1.5. Согласованность кэш-памяти

- •3.2.2. Внутренние кэш-памяти команд и данных

- •3.2.3. Алгоритм кэш-замещений

- •3.2 4. Состояния кэш-памяти данных

- •1.При блокированном чтении:

- •3.2.5. Согласованность внутренних кэш-памятей

- •1) Хранить таблицы страниц и директорий в не копируемой в кэш-память области основной памяти или использовать режим сквозной записи страниц;

- •Процессор может быть заменен (возможен upgraded) без изменения памяти и других подсистем мп вс;

- •Без особого снижения общих характеристик системы могут быть использованы более медленные и менее емкие устройства памяти и устройства ввода/вывода.

- •3.3. Функционирование памяти

- •1) Трансляция сегмента, при которой логический адрес, состоящий из селектора сегмента и смещения (относительного адреса внутри сегмента), преобразуется в линейный адрес.

- •3.3.1. Трансляция сегментов

- •Глобальной таблице дескрипторов (gdt);

- •Локальной таблице дескрипторов (ldt).

- •3.3.2. Адресация физической памяти

- •3.3.4. Комбинирование сегментной и страничной трансляции

- •3.4. Защита памяти

- •3.4.1. Зачем нужна защита?

- •Устанавливает различие между разными форматами дескрипторов;

- •Специфицирует функциональное назначение сегмента.

- •1 Поле предела называют также полем границы.

- •2 Байты сегмента размещены в оп в порядке возрастания адресов памяти или в обратном порядке. Такое размещение также называют соответственно по принципу «младший» и «старший крайний».

- •Cpl (текущий уровень привилегий);

- •Rpl (уровень привилегий источника обращений к сегменту) из селектора, используемый для спецификации сегмента назначения;

- •3)Dpl дескриптора сегмента назначения.

- •Загрузить регистр сегмента данных селектором несогласованного, с разрешением чтения кодового сегмента;

- •Загрузить регистр сегмента данных селектором кодового сегмента, который является согласованным и разрешенным для чтения;

- •Использовать префикс переопределения cs, чтобы прочитать разрешенный для чтения кодовый сегмент, селектор которого уже загружен в cs регистр.

- •Для команды call (или для команды jmp для согласованного сегмента) должны быть выполнены следующие правила привилегий:

- •Привилегированные команды, которые нужны для систем управления вычислительным процессом;

- •Чувствительные команды (Sensitive Instructions), которые используются для ввода/вы вода и для действий, связанных с вводом/выводом.

- •1) Проверка того, имеет ли назначение, специфицированное указателем право доступа к

- •Проверка того, соответствует ли тип сегмента заданному использованию;

- •Проверка указателя на соответствие границе сегмента.

- •Verw (Verify for Writing) - проверка доступности по записи обеспечивает те же самые возможности, что и verr для проверки доступности по чтению.

- •3.4.4. Уровень защиты страниц

- •1) Ограничение адресуемой области; 2) проверка типа страницы.

- •3.4.5. Комбинирование защиты сегментов и страниц

- •Глава 4

- •4.1. Структура современных 8-разрядных микроконтроллеров

- •4.1.1. Модульный принцип построения

- •Tiny avr - mk в 8-выводном корпусе низкой стоимости;

- •Classic avr - основная линия мк с производительностью до 16 mips, Flash память программ объемом до 8 Кбайт и статическим озу данных 128. ..512 байт;

- •Mega avr - мк для сложных приложений, требующих большого объема памяти (Flash пзу до 128 Кбайт), озу до 4 Кбайт, производительностью до 6 mips.

- •4.1.4. Резидентная память мк

- •4.1.5. Порты ввода/вывода

- •Однонаправленные порты, предназначенные в соответствие со спецификацией мк только для ввода или только для вывода информации.

- •Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

- •4.1.6. Таймеры и процессоры событий

- •Импульсную последовательность с выхода управляемого делителя частоты fBijs;

- •Внешнюю импульсную последовательность, поступающую на один из входов мк.

- •Простое увеличение числа модулей таймеров; этот путь характерен для части мк компаний «Pfilips» и «Atmel» со структурой msc-51, для мк компаний «Mitsubishi» и «Hitachi».

- •Изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

- •Изменение логического уровня с 1 на 0 (падающий фронт сигнала);

- •Любое изменение логического уровня сигнала.

2.1.3. Регистровая модель

Регистровая модель процессоров Р6 содержит набор регистров, большинство из которых входят в состав более ранних моделей семейства Intel 80x86/Pentium. Эти регистры составляют следующие группы.

1. Функциональные основные регистры:

регистры общего назначения ЕАХ. ЕВХ, ECX,EDX,ESP,EBP,ESI,EDI;

указатель команд EIP;

регистр флагов EFLAGS;

регистры сегментов CS,SS,DS,ES,FS,GS.

2. Регистры блока обработки чисел с плавающей точкой (регистры FPU): >,;,.

регистры данных R7-0 (ST7-0);

регистр тегов TW;

регистр состояния FPSR; _v, регистр управления FPCR; ;,;' регистры-указатели команды и операнда FIP, FDP.

3. Регистры обработки пакетов чисел с плавающей точкой (регистры SSE):

регистры пакетов данных ХММ7-0; регистр управления состояния MXCSR.

4. Системные регистры:

0 регистры управления режимом CR4-0;

регистры системных адресов GDTR, LDTR, IDTR, TR; регистры отладки DR7-0.

5. Служебные (модельно-специфические) регистры.

Регистры первых трех групп используются при выполнении прикладных программ, регистры 4-й группы - при выполнении системных программ и отладке, регистры 5-й группы - при тестировании микропроцессора и контроле эффективности выполнения программ. Системные и служебные регистры доступны только программам с высшим уровнем привилегий 0.

Номенклатура и содержимое служебных (модельно-специфических) регистров MSR (Model-Specific Registers) определяется конкретной моделью процессора. Запись и чтение их содержимого производится с помощью команд WRMSR и RDMSR. Обращение к некоторым из них может вызвать исключение, если эти регистры отсутствуют в данной модели. Регистры MSR используются в процессе отладки систем, содержат информацию о процессе выполнения программы (число декодированных команд, полученных запросов прерывания, число загрузок в кэш-память и т. п.), обеспечивают различные режимы работы кэш-памяти при обращении к определенным областям основной памяти (MTRR-регистры).

Полная номенклатура MSR содержит более 80 регистров, описание назначения которых выходит за рамки данной книги. В последующих разделах будет рассмотрено функционирование ряда регистров MSR, обеспечивающих реализацию определенных режимов работы процессора.

Функциональные основные регистры. Состав функциональных основных регистров (рис. 2.2) идентичен для всех 32-разрядных микропроцессоров семейства Intel 80x86 и Pentium.

Восемь 32-разрядных регистров общего назначения - ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, EBP, ESP предназначены для хранения данных и адресов. Младшие 16 разрядов этих регистров доступны под именами АХ, ВХ, СХ, DX, SI, Dl, BP, SP. При операциях с байтами можно отдельно обращаться к младшему (разряды 7-0) или старшему (разряды 15-8) байту регистров АХ, ВХ, СХ, DX: младшие байты имеют имена AL, BL, CL, DL, старшие - АН, ВН, СН, DH.

Сегментные регистры CS, SS, DS, ES, FS, GS содержат 16-разрядные значения селекторов сегментов, определяющих адресуемый сегмент памяти. В реальном режиме содержимое этих регистров непосредственно задает значение базового адреса соответствующего сегмента. В защищенном режиме содержимое этих регистров задает выбор дескриптора, который содержит значение базового адреса и другие атрибуты сегмента.

Соответствующий дескриптор выбирается из таблицы, хранящейся в ОЗУ, и размещается в программно-недоступном (теневом) регистре дескриптора сегмента (рис. 2.2). Селектор в регистре CS обеспечивает обращение к сегменту команд, селектор в SS - к сегменту стека, селекторы в DS, ES, FS, GS - к сегментам данных.

Указатель команд EIP представляет собой 32-разрядный регистр, содержимое которого используется в качестве смещения при определении адреса следующей выполняемой команды. Смещение задается относительно базового адреса сегмента команд, задаваемого регистром CS. Младшие 16 бит EIP (биты 15-0) содержат 16-разрядный указатель команд с именем IP, который используется при 16-разрядной адресации. Содержимое EIP (IP) изменяется при выполнении команд передачи управления и прерываний.

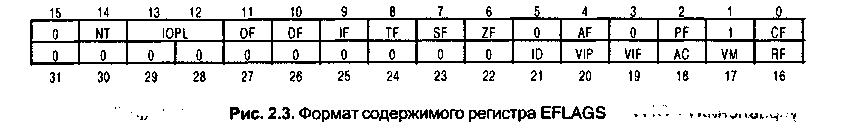

Регистр флагов EFLAGS (рис. 2.3) содержит ряд битов, которые имеют различное назначение: признаки состояния CF, PF, AF, ZF, SF, OF указывают определенные характеристики результата, полученного при выполнении команды; управляющий признак DF определяет порядок адресации операндов при выполнении последовательности команд обработки строк символов; системные признаки TF, IF, IOPL, NT, RF, VM, AC, VIF, VIP, ID задают режим процессора при обслуживании исключений и прерываний, организации ввода-вывода данных, решении последовательности вызываемых задач и реализации ряда других процедур. Младшие шестнадцать бит регистра EFLAGS (биты 15-0) представляют 16-разрядный регистр флагов FLAGS, который используется при выполнении программ, написанных для микропроцессоров 8086, 80186, 80286.

Признаки состояния в регистре EFLAGS имеют следующее значение:

CF- признак переноса, принимает значение CF = 1 при возникновении переноса из старшего разряда обрабатываемых операндов;

PF- признак четности, принимает значение PF = 1, если младшие восемь разрядов результата содержат четное число единичных бит;

AF - признак полупереноса, принимает значение AF = 1, если при выполнении операции возникает перенос между младшими тетрадами (из разряда 3 в разряд 4) обрабатываемых операндов; используется при операциях с операндами, представленными в двоично-десятичном коде (BCD);

SF-признак знака, принимает значение старшего (знакового) разряда результата операции (5 = 0- положительное число, 3 = 1- отрицательное);

OF-признак переполнения, принимает значение OF = 1 в случае переполнения разрядной сетки при обработке операндов со знаком; значение признака для п-разрядных операндов определяется логическим выражением OF = Сп + Сп - 1, где Сп - перенос, возникающий в старшем (п-1)-м разряде (знаковом), Сп-1 - перенос, возникающий в предыдущем (п - 2)-м разряде;

Значение управляющего признака DF устанавливается пользователем и задает порядок обработки строк символов при выполнении соответствующих команд:

DF — признак направления, при значении DF = 0 вызывает автоматический инкремент содержимого индексных регистров ESI, EDI (SI.DI) после выполнения команды обработки символа, при DF = 1 -декремент содержимого этих регистров; таким образом обеспечивается обработка символов слева направо (от младших адресов к старшим) или в обратном направлении (от старших адресов к младшим).

Системные признаки (кроме NT) устанавливаются операционной системой, которая с их помощью задает определенные режимы выполнения ряда процедур:

TF- признак трассировки, при значении TF = 1 процессор переключается в режим пошагового выполнения команд с реализацией после каждой команды соответствующего прерывания;

IF-признак разрешения прерывания, установка значения IF = 1 разрешает обслуживание запроса прерывания, поступающего на внешний вход INTR;