- •Структура и архитектура эвм

- •1) Понятие о структуре и архитектуре

- •2) Основные характеристики эвм

- •Обмен информации в эвм

- •Сигналы адреса, данных и управления

- •Организация магистралей. Распределение ресурсов в эвм

- •Процессоры в эвм. Структура гипотетического процессора

- •Типы процессоров. Операционная и управляющая часть.

- •Полный цикл работы процессора

- •Устройства управления

- •Принципы программного управления

- •Устройства управления с жесткими связями

- •Микропрограммный принцип управления

- •Способы формирования адресов в эвм

- •Базовые способы адресации

- •Модификация адресов

- •Процедура ввода-вывода

- •Способы обмена данными

- •Модули озу и пзу.

- •Преобразование.

Модули озу и пзу.

Структура вычислителя ориентируется на функциональные узлы ОЗУ, ПЗУ с организацией n*8. Обращение к памяти производится побайтно. В связи с эти необходимо комплексирование элементов памяти имеющих отличную организацию. Наиболее типичным примером схем ОЗУ с организацией 2n*1 являются схемы динамического типа К565РУ. Для получения требуемой организации n*8 необходимо комплексировать корпуса — объединять в блоки по 8 корпусов.

Правила объединения:

сигналы адреса всех 8 корпусов объединяются параллельно

сигналы данных подсоединяются к шине (соответствующим 8 разрядам)

сигналы RD/WR включаются параллельно

сигналы выборки CS включаются параллельно

Особенность

схем этой серии — адрес записывается

за два такта для применяют управляющие

сигналы CAS

и RAS

(включаются параллельно). Такой модуль

может иметь небольшую емкость, тогда

для увеличения емкости включают несколько

таких модулей. Выбор модулей — по

адресному дешифратору через сигнал CS.

Регенерация с схемах происходит в

выбранном модуле по столбцам.

Особенность

схем этой серии — адрес записывается

за два такта для применяют управляющие

сигналы CAS

и RAS

(включаются параллельно). Такой модуль

может иметь небольшую емкость, тогда

для увеличения емкости включают несколько

таких модулей. Выбор модулей — по

адресному дешифратору через сигнал CS.

Регенерация с схемах происходит в

выбранном модуле по столбцам.

Схемы К537РУ статического типа не требуют регенерации, поэтому при небольшом объеме более удобны, но с увеличение объема их наращивают с помощью адресного дешифратора. Статические ОЗУ более удобны в контролерах формирующих временные интервалы. Динамические схемы требуют регенерации, поэтому время выполнения отдельных команд непостоянно (импульс дрожит).

Схемы постоянной памяти.

Схемы однократно программируемые пользователем РР — используют пережог плавких перемычек соединяющих строки и столбцы матрицы. Перемычка однонаправлена, следовательно она должна включать диод или транзистор. КМОП транзисторы достаточно долго не применялись вследствие малых токов. На сегодня основной элемент в связи биполярный многоэмиттерный транзистор в эмиттер которого включена плавкая вставка. Физически плавкая вставка представляет из себя напыление из NiCr на разрыв алюминиевого проводника. Для создания локального перегрева вставка имеет утонченный профиль. По эмиттеру транзистор выбирается и через коллектор-эмиттер пропускается ток пилообразной формы. Наклон и длительность импульса подбираются для каждого типа схем. При быстром нарастании тока может произойти термовзрыв — быстрый перегрев перемычки и закипание металла (металл разбрызгивается). При медленном нарастании тока перемычка не расплавляется т.к. энергии недостаточно. Основной недостаток К556 возможность восстановления связей. Со временем кристалл нагревается, алюминиевые проводники текут и контакт восстанавливается. Такое явление устраняется термотренировкой — схема программируется, нагревается, повторно программируется, нагревается. Число таких циклов порядка 10. Эта серия не очень рекомендуется в специзделиях из-за восстановления. Для таких изделий разработана серия К541 в которой перемычки выполнены из поликремния. При разогреве перемычек полупроводник переходит в агрегатное состояние изолятора. Состояние необратимое, поэтому такие перемычки не восстанавливаются, но нагрев производится до большой температуры, поэтому выход годных схем ниже, схемы дороже.

Репрограммируемые схемы имеют также матрицу с однонаправленными элементами связи. Каждый элемент путем подачи высокого потенциала (26-28В) переводится в непроводящее состояние. Со временем накопленные заряды могут стекать и элементы связи вернутся в исходное состояние. Поэтому стремятся увеличить «время жизни» такого состояния. Искусственное стирание информации производится облучением жесткими лучами схем РФ и подачей обратного потенциала в схемах РР. Стираемые лучами связи 573РФ обычно стремятся изолировать от света солнца, закрашивая окно в корпусе непрозрачным лаком. Особый интерес представляют разработанные схемы ППЗУ на основе КМОП технологии (К162Х) — малопотребляющие, надежные. Основной недостаток РТ, РР, РФ — значительное потребление энергии.

Ассоциативные ЗУ.

Ассоциативные

ЗУ относят к безадресным элементам,

хотя косвенно термин адрес в них

появляется. Часто эти схемы называют

адресация по содержимому, т.е. при

обращении к схеме производится поиск

по входному сигналу, его образу. Например,

в толстой книге необходимо встретить

сочетание «ах, если бы». При поиске

такого сочетания результатом будет

номер страницы, номер строки, т.е.

своеобразный адрес по которому находится

фраза. Ассоциативное ЗУ работает

одновременно с процессорами. Основное

назначение таких систем — распознавание

образов. На вход системы предъявляется

некоторый образ. Система сопоставляет

этот образ с имеющимися в ее памяти

реализациями и в случае совпадения

обрабатывает соответствующую подпрограмму.

Таким образом, в основе работы таких

систем лежат процедуры сравнения,

сопоставления входной реализации с

содержимым памяти. Поскольку хранимые

образы как бы идеальны, их называют

эталонами. Схемы АЗУ сравнивают входной

сигнал с эталоном, формируя адрес при

совпадении. В основе процедур сравнения

— схемы с последовательным или

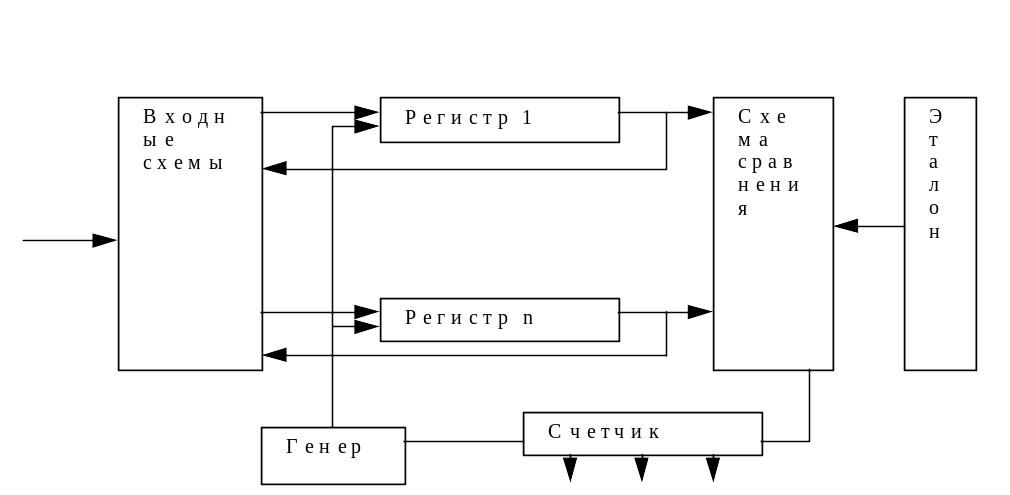

параллельным сравнением. Структура с

последовательным сравнением имеет вид.

Регистры содержат к слов (входные

реализации). Каждое слово n

разрядное. Крайние разряды (слово)

сравнивается с одним эталоном. Если

совпадения нет, то тактовый генератор

проталкивает кольцевым сдвигом содержимое

на 1 разряд вправо. Правый разряд

переписывается через входные схемы

вновь. На следующем такте сравнивается

новое слово и так до совпадения. Если

по всем разрядам информация совпала с

эталоном схема сравнения останавливает

счетчик и выдается номер совпавшей

реализации. Т.е. из пришедшего массива

находится номер слова эталона. Информация

в регистры загружается через вход n

разрядов. Таким образом процедура

сравнения требует:

Ассоциативные

ЗУ относят к безадресным элементам,

хотя косвенно термин адрес в них

появляется. Часто эти схемы называют

адресация по содержимому, т.е. при

обращении к схеме производится поиск

по входному сигналу, его образу. Например,

в толстой книге необходимо встретить

сочетание «ах, если бы». При поиске

такого сочетания результатом будет

номер страницы, номер строки, т.е.

своеобразный адрес по которому находится

фраза. Ассоциативное ЗУ работает

одновременно с процессорами. Основное

назначение таких систем — распознавание

образов. На вход системы предъявляется

некоторый образ. Система сопоставляет

этот образ с имеющимися в ее памяти

реализациями и в случае совпадения

обрабатывает соответствующую подпрограмму.

Таким образом, в основе работы таких

систем лежат процедуры сравнения,

сопоставления входной реализации с

содержимым памяти. Поскольку хранимые

образы как бы идеальны, их называют

эталонами. Схемы АЗУ сравнивают входной

сигнал с эталоном, формируя адрес при

совпадении. В основе процедур сравнения

— схемы с последовательным или

параллельным сравнением. Структура с

последовательным сравнением имеет вид.

Регистры содержат к слов (входные

реализации). Каждое слово n

разрядное. Крайние разряды (слово)

сравнивается с одним эталоном. Если

совпадения нет, то тактовый генератор

проталкивает кольцевым сдвигом содержимое

на 1 разряд вправо. Правый разряд

переписывается через входные схемы

вновь. На следующем такте сравнивается

новое слово и так до совпадения. Если

по всем разрядам информация совпала с

эталоном схема сравнения останавливает

счетчик и выдается номер совпавшей

реализации. Т.е. из пришедшего массива

находится номер слова эталона. Информация

в регистры загружается через вход n

разрядов. Таким образом процедура

сравнения требует:

загрузки информации

последовательное сравнение до совпадения.

Может

оказаться, что совпадения не произойдет,

тогда счетчик по переполнению выдает

сигнал отсутствия. Описанная схема

имеет последовательный принцип, основной

недостаток которого время. Поэтому

применяют параллельные схемы АЗУ, в

которых число схем сравнения равно

числу разрядов регистра и каждый разряд

схемы регистра связан со своей схемой

сравнения, а она с одним эталоном.

Опознавание производится за один «такт».

Если какой либо разряд совпадет с

эталонным результатом — адрес по схеме

сравнения. В параллельных схемах основное

— большое число связей, поэтому

разрядность таких схем невысокая. БИС

АЗУ с серийном виде не выпускаются. Это

связано с еще недостаточно широким

развитием распознающих автоматов.

Трудности — число входов\выходов. Схемы

АЗУ находят применение в различных

распознающих автоматах (системах и\или),

поэтому применение автоматов стимулирует

АЗУ.

Может

оказаться, что совпадения не произойдет,

тогда счетчик по переполнению выдает

сигнал отсутствия. Описанная схема

имеет последовательный принцип, основной

недостаток которого время. Поэтому

применяют параллельные схемы АЗУ, в

которых число схем сравнения равно

числу разрядов регистра и каждый разряд

схемы регистра связан со своей схемой

сравнения, а она с одним эталоном.

Опознавание производится за один «такт».

Если какой либо разряд совпадет с

эталонным результатом — адрес по схеме

сравнения. В параллельных схемах основное

— большое число связей, поэтому

разрядность таких схем невысокая. БИС

АЗУ с серийном виде не выпускаются. Это

связано с еще недостаточно широким

развитием распознающих автоматов.

Трудности — число входов\выходов. Схемы

АЗУ находят применение в различных

распознающих автоматах (системах и\или),

поэтому применение автоматов стимулирует

АЗУ.

Безадресные схемы. Стек.

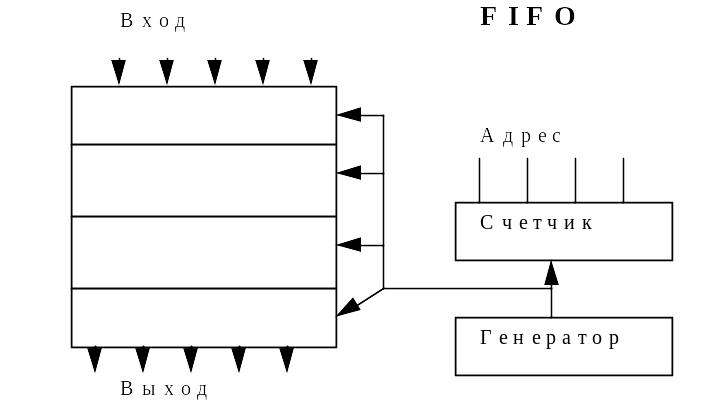

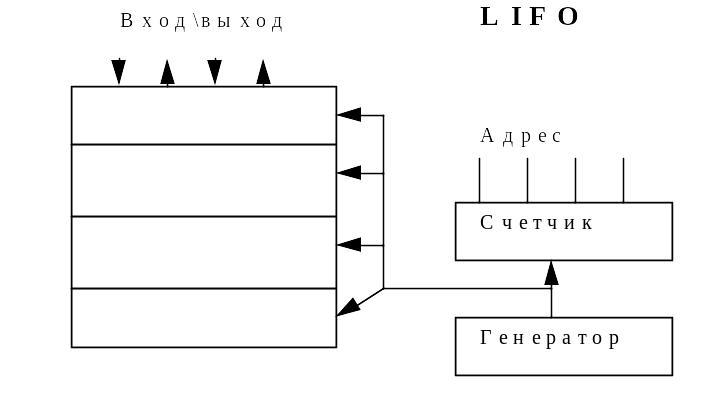

Другим примером безадресных схем, являются схемы построенные по принципу стека — набор регистров в которых информация сохраняется незначительное время. Фактически адрес в этих структурах все же присутствует, хотя проявляется неявно. FIFO — представляет из себя набор нескольких регистров разряды которых параллельно соединены, так что при каждом тактовом сигнале содержимое проталкивается вниз. Число регистров — глубина стека. Эта структура обеспечивает некоторую задержку хранимой информации и доступ к ней по внешнему сигналу. При каждом проталкивании вниз в верхний регистр записывается новая информация. LIFO предусматривает запись и чтение только с верхнего регистра. В стек заносятся последовательно несколько слов, чтение производится в обратной последовательности. Этот стек разработан для адресации при обращении к подпрограммам. При обращении к подпрограмме в стек заносится адрес возврата. Если в выполняемой подпрограмме имеются вложенные подпрограммы, адрес возврата в основную программу проталкивается вниз но полной глубины стека. При выходе из подпрограммы содержимое поднимается и последним показывается адрес возврата в основную программу. Стек выполняется аппаратно, что дает сокращение времени при переходе от\к подпрограмме. Как таковой адрес в этих схемах и не нужен. Информация об адресе косвенно учитывается программистом при составлении программы.

ВЗУ. Спектр решений.

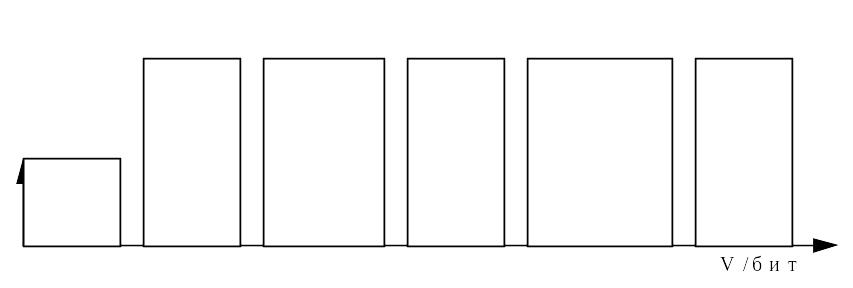

Способы

построения памяти и основные элементы

ЗУ считаются некоторым критерием,

оценивающим уровень вычислительной

техники. Поэтому системам памяти

придается много внимания при разработке.

Магнитная память считавшаяся основной

на начальных этапах вычислительной

техники сегодня прочно обосновалась

во внешних ЗУ. Объем ЗУ на единицу

хранимой информации постоянно снижается

вследствие улучшения технологии

получения самого материала и новых

способов записи\чтения информации

разрабатываемых постоянно. Эти два

направления приводят к появлению новых

конструктивных решений в ВЗУ. При этом

можно сказать, что своего предела как

по объему, так и по быстродействию

магнитные ЗУ еще не достигли. Характеристики

магнитных ЗУ с точки зрения объема на

бит хранимой информации можно представить

в виде некоторой координатной оси на

которой отмечены существующие на сегодня

технические решения. Минимально возможный

объем материала для хранения бита домен.

Рассмотренная система по координатам

имеет разрывы между реализациями. Т.к.

в природе разрывов нет, можно считать,

что в этих разрывах пока не предложенные

технические реализации. Вместе с

различными техническими реализациями

меняется и способ запаси информации на

носитель, постоянным же остается пока

только одно: информация занесется или

считается с магнитного материала при

обязательном изменении магнитного поля

пересекающего виток проводника. Вне

зависимости от уровня тока в проводнике

это требование остается. Основными

способами записи цифровой информации

в магнитные ЗУ являются:

Способы

построения памяти и основные элементы

ЗУ считаются некоторым критерием,

оценивающим уровень вычислительной

техники. Поэтому системам памяти

придается много внимания при разработке.

Магнитная память считавшаяся основной

на начальных этапах вычислительной

техники сегодня прочно обосновалась

во внешних ЗУ. Объем ЗУ на единицу

хранимой информации постоянно снижается

вследствие улучшения технологии

получения самого материала и новых

способов записи\чтения информации

разрабатываемых постоянно. Эти два

направления приводят к появлению новых

конструктивных решений в ВЗУ. При этом

можно сказать, что своего предела как

по объему, так и по быстродействию

магнитные ЗУ еще не достигли. Характеристики

магнитных ЗУ с точки зрения объема на

бит хранимой информации можно представить

в виде некоторой координатной оси на

которой отмечены существующие на сегодня

технические решения. Минимально возможный

объем материала для хранения бита домен.

Рассмотренная система по координатам

имеет разрывы между реализациями. Т.к.

в природе разрывов нет, можно считать,

что в этих разрывах пока не предложенные

технические реализации. Вместе с

различными техническими реализациями

меняется и способ запаси информации на

носитель, постоянным же остается пока

только одно: информация занесется или

считается с магнитного материала при

обязательном изменении магнитного поля

пересекающего виток проводника. Вне

зависимости от уровня тока в проводнике

это требование остается. Основными

способами записи цифровой информации

в магнитные ЗУ являются:

по трем уровням

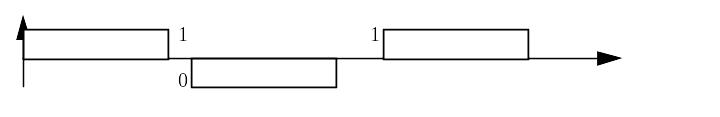

Единица

записывается при одном направлении

тока в проводнике, ноль пишется при

обратном направлении тока. Основной

недостаток способа — малая плотность

записи за счет промежутков между битами.

Единица

записывается при одном направлении

тока в проводнике, ноль пишется при

обратном направлении тока. Основной

недостаток способа — малая плотность

записи за счет промежутков между битами.

без

возврата к нулю

без

возврата к нулю

Пустых промежутков нет. Поэтому разделять одинаковые биты (например 00) сложно. Необходим синхросигнал.

двухчастотный

Единичный сигнал записывается переменным напряжением удвоенной частоты.

запись по двум дорожкам

Для записи единиц использовалась одна дорожка, для записи нулей другая.

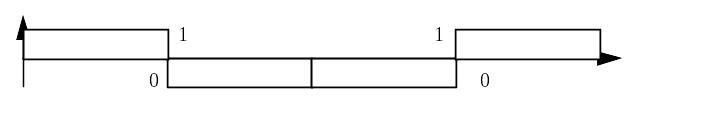

фазовый метод

Если

после записи 0 или 1 пишется тот же

уровень, направление тока изменяется.

Если уровень изменился 01,

10,

ток в магнитной головке не изменяется.

Статистически учитывая. Что разряды

постоянно меняются, скорость изменения

тока меньше. Расшифровка записанной

информации требует специальной схемы,

но стабильна.

Если

после записи 0 или 1 пишется тот же

уровень, направление тока изменяется.

Если уровень изменился 01,

10,

ток в магнитной головке не изменяется.

Статистически учитывая. Что разряды

постоянно меняются, скорость изменения

тока меньше. Расшифровка записанной

информации требует специальной схемы,

но стабильна.

Накопители на магнитных лентах продолжают оставаться основными для устройств большой емкости. Оптические накопители на сегодняшнем уровне работают только по чтению, перезапись информации с нынешним уровнем технологии невозможна.

Контроль информации в ЭВМ.

Классификация методов контроля

Контроль выполнения преобразований. Диагностика.

Классификация методов контроля.

Поскольку ВМ — сложная техническая система в ней обязательно должны использоваться процедуры контроля как передачи, так и преобразования информации, т.е. помимо основного оборудования в схемах предусматривается дополнительно средства контроля. При выявлении ошибки процесс преобразования (передачи) заканчивается, по возможности ошибка исправляется и основная программа продолжается. Таким образом цель средств контроля не остановить вычисления, а получить результат с максимальной достоверностью. Контроль проводится как аппаратными средствами, так и программно. Аппаратные средства включаются в состав основных функциональных блоков процессора, контроллера ввода\вывода, средств передачи. Программно контролируется память, выполнение отдельных операций. При появлении ошибки программно сохраняются промежуточные результаты и воспроизводится ситуация которая привела к ошибке. Она проверяется и отображается при необходимости на внешних устройствах. Все средства контроля принято условно делить на две составляющие: контроль передачи информации, контроль преобразования. Основным способом обнаружения при процедуре передачи считается сумма по модулю 2. К передаваемой информации добавляется 1, контрольный разряд ( например девятый). Источник вырабатывает байты информации и схема контроля автоматически устанавливает 9 разряд в 1 или 0 в зависимости от передаваемого кода. При контроле по чету контрольный разряд должен иметь значение с учетом которого сумма по модулю 2 передаваемых разрядов 0. При контроле по нечету сумма по модулю 2 равна 1. В приемнике все 9 принятых разрядов вновь объединяются схемой суммы по модулю 2 и вновь сравниваются (чет\нечет). Возникает ошибка — передача приостанавливается. Сумма по модулю 2 позволяет обнаружить нечетные ошибки, исправить не может. Для исправления при передаче используют избыточные коды. Суть этого метода: двоичная информация представляется не полным двоичным кодом, а избыточным (кодом Хэмминга). В коде Хэмминга одна комбинация от следующей отличается не менее чем двумя разрядами (кодовое расстояние r=>2). Увеличение кодового расстояния ведет к росту разрядности передаваемого кода, поэтому такие кода называют избыточными. Коды Хэмминга в приемнике позволяют распознать испорченную информацию, восстановить ее. Восстановление — процедура замены принятого кода на ближайший код Хэмминга. Увеличение разрядности до 30-40%. Помимо кода Хэмминга применяют циклические коды. Они основаны на том же принципе увеличения кодового расстояния. В целом контролем передачи охвачены все цепи при передаче между процессором и внешними устройствами. Контроль передачи информации вводится всегда, если информация передается между памятью процессора и внешним устройством. Наиболее популярными способами являются контрольный разряд и сумма по модулю 2.