- •Структура и архитектура эвм

- •1) Понятие о структуре и архитектуре

- •2) Основные характеристики эвм

- •Обмен информации в эвм

- •Сигналы адреса, данных и управления

- •Организация магистралей. Распределение ресурсов в эвм

- •Процессоры в эвм. Структура гипотетического процессора

- •Типы процессоров. Операционная и управляющая часть.

- •Полный цикл работы процессора

- •Устройства управления

- •Принципы программного управления

- •Устройства управления с жесткими связями

- •Микропрограммный принцип управления

- •Способы формирования адресов в эвм

- •Базовые способы адресации

- •Модификация адресов

- •Процедура ввода-вывода

- •Способы обмена данными

- •Модули озу и пзу.

- •Преобразование.

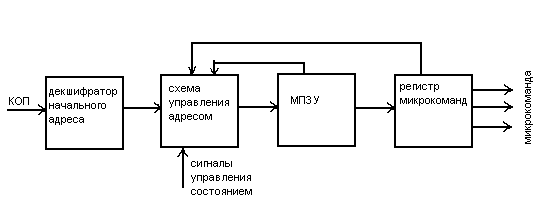

Микропрограммный принцип управления

Является основным при разработке специализированных схем и при использовании в секционированных микропроцессорах. В его основе лежит введение промежуточного преобразования кода команд в микрокоманды на основе схем памяти. Управление на уровне команд – это связь памяти команд с процессором. Но внутри самого процессора из КОП необходимо получать последовательность микрокоманд. Это последовательность может меняться. Если ее записывать в память – промежуточную, то смена содержимого памяти эквивалентно замене микрокоманд последовательным преобразованием сигналов.

С приходом КОП дешифратор начальной

команды (ПЛМ) формирует адрес, по которому

из памяти микрокоманд необходимо считать

первую микрокоманду. Считанный код

микрокоманды уходит на управление

различными узлами операционной части,

вместе с этим это код содержит признак

смещения, по которому определяется

адрес следующей микрокоманды. На

следующем тактовом сигнале по новому

адресу из памяти микрокоманды читается

новое содержимое. И так до тех пор, пока

в микрокоманде не появится признак

конца команды, этот признак увеличит

содержимое считанной команды на 1, и из

ПЗУ прочитается следующий КОП. Идея

была предложена в 50-х годах. На сегодня

схемы типа РТ. РР, РФ обеспечивают

удобства в применении такого способа.

приходом КОП дешифратор начальной

команды (ПЛМ) формирует адрес, по которому

из памяти микрокоманд необходимо считать

первую микрокоманду. Считанный код

микрокоманды уходит на управление

различными узлами операционной части,

вместе с этим это код содержит признак

смещения, по которому определяется

адрес следующей микрокоманды. На

следующем тактовом сигнале по новому

адресу из памяти микрокоманды читается

новое содержимое. И так до тех пор, пока

в микрокоманде не появится признак

конца команды, этот признак увеличит

содержимое считанной команды на 1, и из

ПЗУ прочитается следующий КОП. Идея

была предложена в 50-х годах. На сегодня

схемы типа РТ. РР, РФ обеспечивают

удобства в применении такого способа.

Обратная связь из регистра микрокоманд обеспечивает изменение текущего адреса микрокоманды. Связи жесткие и они определяют последовательность в выполнение микрокоманд. Для операций ветвления необходимы адреса переходов. Эти адреса вырабатываются из МПЗУ и совместно с управлением (смещением) изменяют следующий адрес микрокоманды. Для анализа текущих результатов (признаков) выполнения на схему управления адреса из операционного блока поступают сигналы управления состоянием – признаки (флаги), формируемые другими устройствами. В результате адрес следующей микрокоманды зависит от трех групп сигналов: 1) смещение 2) адреса перехода, если он используется 3) признаков (флагов) из операционного блока. Запаздывание смещение на один такт от адреса перехода объясняется необходимостью записи этого адреса в регистр схемы управления.

Введение регистра адреса перед МПЗУ задерживает выполнение на один такт, позволяет организовать конвейер, т.е. уменьшить время такта, которое определяется быстродействием МПЗУ. На практике МПЗУ требуется большой разрядности: от нескольких десятков до сотен бит. Поэтому регистр адреса вводят редко. В качестве МПЗУ схемы с пережогом связей (К155РТ2, К566 РТХХ). Блок микропрограммного управления при использовании схем СИС и БИС аппаратно не мал. Поэтому иногда, в специальных процессорах его выполняют в виде одной БИС – управляющей памяти. Эти БИС, как правило, масочно программируемые. Содержимое неизменно. Аппаратные затраты сокращаются, но изменять микрокоманды нельзя.

Способы формирования адресов в эвм

Базовые способы адресации

Модификация адресов

(1) Принцип работы любого вычислителя основан на использовании содержимого памяти: по адресу читаем содержимое, модифицируем его и возвращаем назад в память. При этом в вычислителе выделяем два потока информации: 1) команды от ПЗУ до регистра команд, адрес выбирает команды устанавливаемые счетчиком адресов процессора. Последовательная выборка, переходы выполняются только с использованием этого счетчика. 2) данные. Объем памяти данных значительно больше памяти команд. К данным процессора обращается по адресу зачастую зависимому от алгоритма – пользователя. Поэтому чтение (запись) возможно с применением нескольких способов формирования адреса данных. Эти способы называют – адресацией. Переход от одного типа к другому объясняется стремлением пользователя упростить процедуру написания программы, сэкономить память команд. Основными типами адресации данных являются: 1) прямая адресация 2) косвенная 3) непосредственная.

прямая адресация применяется для R/W данных в ОЗУ. Формат команды прямой адресации имеет вид.

КОП младший байт старший байт

Прямая адресация наиболее проста. Она обеспечивает произвольный доступ к любой ячейки памяти в интервале всего адресного пространства. В большинстве систем команд разрядность 16, следовательно, прямая адресация обеспечит доступ к любой ячейке памяти в интервале 64К.

Недостаток – способ не позволяет произвольно обращаться к большей памяти. Прямая адресация осталась основной в малых вычислителях, в которых нет расширения памяти. В ЭВМ прямая адресация применяется для работы внутри сегмента. Последовательность прохождения сигнала: процессор читает КОП по признаку. В КОП он выбирает следующие два бита, записывает их в регистр адреса ,и содержимое регистра адреса выставляет на шину адреса. От туда идет в ОЗУ и из него в регистр входа данных процессора. Т. о. Такая команда требует 4 цикла при выполнении. Прямая адресация основа для расширения модификации адресов.

2) непосредственная адресация. Применяют для ввода данных, начальных данных, констант в ОЗУ. Эти данные должны храниться в ПЗУ. Эти данные не могут быть модифицированы, поэтому работа с ними возможна с ними только через ОЗУ. Такая адресация применяется во всех командах загрузки данных. Формат

КОП

данные КОП младший байт старший

байт данные

КОП

данные КОП младший байт старший

байт данные

Основные ограничения на непосредственную адресацию – это сам операнд. Поскольку операнд должен храниться в памяти команд невозможно оперативно его изменить. Отсюда команды применяются только для загрузки.

3) Наиболее удобным способом обращения к ОЗУ – косвенная адресация. Как правило она применяется при работе с масштабами: формирование масштаба, накопление данных, ввод данных, при чтении и выводе информации на дисплей через ЦАП на процессор. В основе косвенного метода лежит использование промежуточного ОЗУ для получения физического адреса. Последовательность формирования адреса:

К

ОП

адрес промежуточное ОЗУ ША

ОЗУ

ОП

адрес промежуточное ОЗУ ША

ОЗУ

В поле команды за КОП располагается адресная часть, ее разрядность не велика, поэтому она занимает немного места. Содержимое адресной части: адрес 1 поступает на промежуточное ОЗУ, выбирая из него ячейку содержащую физический адрес. Последний пересылается на ША. По нему выбирается нужная ячейка ОЗУ. В старых разработках в качестве промежуточного ОЗУ применяли специальные схемы СОЗУ малой емкости. Число слов хранения в них 16-32. В тоже время, разрядность таких СОЗУ соответствовала полной разрядности памяти данных (16,20). С появлением процессора промежуточное ОЗУ начали размещать непосредственно на кристалле микропроцессора, поэтому связь кода команды с промежуточным ОЗУ – по внутренним сигналам процессора. Пользователь не ощущает этого промежуточного ОЗУ. Га ША появляется уже физический адрес. В отличие от прямой адресации косвенная: 1) формат команды короче, он занимает один байт. Адресная часть размещена в КОП. Количество адресов (объем промежуточного ОЗУ) уменьшилось, но команда занимает в памяти меньше места. 2) Любая команда прямой адресации требует нескольких обращений в память команд. КОП, адрес младший, адрес старший и адрес доступа к данным, т.е. минимум 4 раза на ША. Косвенная адресация обходится двумя циклами: КОП, физический адрес доступа к данным. В косвенной адресации прежде чем воспользоваться ее, требуется определить содержимое памяти: в регистровую пару необходимо занести адрес начальной ячейки памяти данных, т.е. определить составные этой памяти. Если это не сделать, обращение произойдет по нулевому адресу, либо по случайному адресу. При обращении к следующей ячейке содержимое регистровой пары следует увеличить (уменьшить) на единицу специальной командой. Команды косвенной адресации дают заметное преимущество, если массив пересылает данных более 10. Тем более, что косвенная адресация легко вписывается в цикл – прямая же нет. Косвенная адресация позволяет просто организовать цикл в программе, прямая – затруднительно.

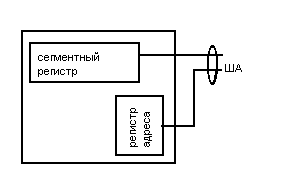

(2) С расширением адресного пространства ОЗУ стала проблема увеличения разрядности адреса без изменения процессора. С этой целью разрабатываются различные подходы к получению физического адреса при сохранности структуры самого процессора.

1) страничная адресация – это варианты позволяющие увеличить разрядность шины адреса. Дополнительно к адресной шине процессор комплексируется разряды с триггера адреса.

Триггеры адреса – обычно счетчик с последовательным счетом и возможностью установки данных дополнительно в ША. Использует выходные разряды такого счетчика. ША увеличивается во много раз. Основной недостаток этого способа – необходимость управления счетчиком. Им необходимо управлять через внешние сигналы процессора. Идея страничной адресации интегрирована в сегментную. Этот триггер выполнен внутри процессора, его выходы образуют дополнительные 4 разряда адреса.

Поскольку сегментный регистр выполняется 16 разрядным, его содержимое сдвигается на 4 разряда влево и складывается с регистром адреса. В результате формируется смещение содержимого адресного регистра. При таком способе изменить адрес можно двумя путями. Появляющаяся степень свободы накладывает дополнительно заботу о состоянии всех внутренних регистров процессора. Сформировать физический адрес можно и с участием третьего регистра – регистра смещения или базового регистра. Его содержимое как бы перемещает физический адрес в пространстве адресов на некоторую величину. Если вместо базового использовать другой регистр получают относительный адрес.

Все способы модификации ориентируются на критерий: минимальное время формирования адреса при максимальном адресном пространстве. Прежде чем начать работу с процессором надо определить все его регистры. Можно использовать и композицию, объеденные способы увеличения адресов, если возникает в том необходимость. В системе DEC существуют два дополнительных способа: автоинкремент и автодекримент. При косвенной адресации увеличение/ уменьшение на1 (2) содержимого адресного регистра происходит автоматически после обращения в память.

Рассмотренные способы адресации позволяют успешно обращаться к любым ячейкам памяти в предельно максимальный адрес системы.

Процессоры

Типы процессоров, классификация.

Микропроцессоры, микроконтроллеры

многокристальные микропроцессоры

Секционированные микропроцессоры.

(1) Классификация. Со времени появления микропроцессоров их структура и возможности значительно изменились. Первые микропроцессоры были разработаны для устройств автоматического управления, но не для вычислителей. Отсюда появление множества новых фирм, которые занимались разработкой вычислителей на первых микропроцессорах. Но с увеличением интеграции появилась возможность разработки кристаллов, структура которых была близка к процессорам универсальных ЭВМ. Дальнейшее увеличение интеграции привело к появлению целых групп различных процессоров: 1) арифметические процессоры, ориентированные на выполнение команд длинной арифметики.

2) многокристальные процессоры, когда в один корпус вставляли 2-3 кристалла, выполняющих функции основного процессора, памяти, сопроцессора.

3) микроконтроллеры – схемы с архитектурой процессора, но интегрированные в один кристалл – однокристальные микроЭВМ.

4) транспьютеры – кристаллы, работающие в структурах однородных вычислительных сред.

5) секционированные микропроцессоры и специализированные схемы.

Каждое из этих направлений имеет свою область применения, решает свои задачи. Более того, внутри каждого направления существует деление: а) по разрядности схем (2,4,8,16,32) б) по потребляемой мощности в) по системе команд микропроцессора и т.д. Любая классификация преследует цель – полнее показать варианты изделия, опираясь на признак.

Микроконтроллеры.

Составляют большую группу ЦФУ, использующих последовательный принцип обработки. В основе микроконтроллера – большая ИМС микроконтроллера. На сегодня выделяется три вида таких схем: 1) однокристальные микропроцессоры с разрядностью 8-16 (ОМП) 2) однокристальные микроЭВМ 8 разрядов 3) PIC контроллеры.

Первоначально контроллеры строились на основе ОМП. Это традиционный подход. Первые МП предназначались для контроллеров. С увеличением интеграции во многих применяемых ОМП стали заменятся на однокристальные микроЭВМ. И на сегодняшний день микроЭВМ – основной тип интегральных схем в контроллерах.

PIC контроллеры используют несколько иную структуру. По больше ориентированы по алгоритмам на анализ входных сигналов. Направление развивается.

Программная структура однокристального микропроцессора (8 разрядов)

Основа схемы - двухвходовое АЛУ. Операнды фиксируются перед АЛУ в промежуточных регистрах А и В. необходимость в них выравнивание во времени появления операндов. Сигнал с выхода АЛУ через внутренний выход ШД поступает в РОН. Количество и разрядность РОНов изменяется 8-16. Их количество определяется числом разрядов в коде команды прямой регистровой адресации (3-4). Разрядность одинарной длины 8 или двойной – 16. РОНы связаны внутри входной ШД, через которую сигнал поступает в регистр промежуточного хранения или регистр данных. Входные сигналы через ШД фиксируется регистр. Далее поступая в промежуточный регистр. Код команды КОП запоминается регистром команд, после чего устройство управления с помощью тактовых сигналов преобразует код команды в микрокоманду, управляющей внутренним коммутатором схемы. Счетчик адреса формирует адрес на ША по сигналам микрокоманды, при имеется возможность занесение входного сигнала непосредственно в счетчик. Для косвенной адресации необходимо занесение в счетчик адреса содержимого РОНа. При выполнении любой операции, АЛУ формирует признаки (флаги), которые фиксируются регистре признаков. Схема не только обрабатывает операнды, но и формирует управляющие сигналы для работы внешних блоков.

Главной особенностью микропроцессора является наличие внутренней входной и выходной ШД. Эти шины отделяют микропроцессоры от других БИС.

Примеры ОМП, используемых в микроконтроллерах микроЭВМ.

семейство микропроцессоров К580ВМ80, кроме 8 разрядного. Аналог Intel8080. Рекомендуют в качестве памяти использовать типовые схемы ОЗУ (серии К565 ПУХХ, К541ПУХХ), ПЗУ – К556РТХХ

этой схемы Intel 8085 соответствует К1821ВМ85

Z-80 во многом схема похожа на к580ВМ, но в ней предусмотрена регенерация памяти (восстановление) и добавлены еще две команды.

Третью группу схем контроллеров – программируемые интегральные контроллеры. Используют не вычислительную структуру для получения сигналов управления. Это позволяет им иметь большую производительность, но требует несколько иного подхода при разработке программного обеспечения- использует не очень простые эмуляторы

Секционные микропроцессоры.

Они ориентированы на использование в специализированных вычислителях и контроллерах. Требуемая разрядность устройства получается за счет наращивания разрядности нескольких секций. Например: 16 разрядный вычислитель строится на 4 разрядных секциях. На сегодняшний день наиболее замечательными сериями являются К588ВС1;2 К1804ВС1;2;3

К588ВС – 16 разрядная секция, выполнена КМОП технологии, но ориентирована на применение в вычислителях с системой DEC. Она может использоваться как самостоятельная схема с микропрограммным управлением. КМОП позволяет использовать автономное питание. Схема не требует тактового генератора. В качестве тактового генератора используется 13 разряд микрокоманды. Схема была ориентирована на автономные системы обработки и управления. Совместно с основной схемой разработаны дополнительные ИМС регистры контроллера. Поскольку КМОП не может работать в жестких условиях, разработали ТТЛШ секции. К1802, К1804. Основное назначение – бортовая аппаратура высокой производительности. Секции включают набор дополнительных схем. По распространенности 1804 лучше – в его состав входит комплекты более 10 схем, но в них нет ОЗУ и ПЗУ. Ориентация как и в 580. Помимо серии 1802 и 1804 существуют сверхбыстродействующие К1800ВС1 ЭСЛ 4-разрядная. В состав кроме секций и буферных регистров входит ОЗУ и ПЗУ. Структура секций во многом повторяет ОМП, где отсутствует адресный счетчик и регистр команд. Отсутствует регистр флагов, а дешифратор преобразует микрокоманду в унитарный код. Причина – биполярный, рассеивается больше мощности и что бы кристалл не перегрелся , степень его интеграции не высока.

Многокристальные микропроцессоры.

Первые однокристальные микропроцессоры (микроконтроллеры) мало подходили для организации удобных вычислительных процедур, а именно: 1) разрядность адреса не высока, разрядность данных (8,16). 2) при необходимости можно было увеличить в 2-4 раза, но это увеличение приводило к большим временным затратам. 3) сложные арифметические операции выполнялись программно, т.е. нужно время. 4) неудобная система прерываний. С учетом сказанного микропроцессоры от микроконтроллеров значительно продвинулись в своем развитии, прежде всего, по возможности увеличения адресуемого пространства.

первый шаг был сделан за счет введения адресного сумматора, позволяющего формировать адрес на ША очень гибким способом. Адрес формировался как сумма содержимого нескольких внутренних регистров процессора: непосредственно адресного, смещения и сегментного и базового регистров. Причем последние складываются в сумматоре после сдвига в сторону старших на 4. За счет чего старшие разряды адреса идут, минуя сумматор. Адрес в ОЗУ может быть изменен содержанием любого из указанных регистров, т.е косвенная адресация позволяла легко перемещаться в адресном поле за счет только одной команды.

Сложные команды начали выполняться с использованием аппаратных средств. Первые опыты применения арифметических микропроцессоров.

Примеры:

К1810ВМ87 процессор заменяет основной при

выполнении команд деления , умножения,

требующих большого времени. Такие схемы

назывались сопроцессорными. Локальная

шина объединяет ША и ШД двух схем и о бщие

сигналы управления при получении кода

длинной команды. Основной процессор

блокируется, операция выполняется

сопроцессором. Это направление получило

распространение в системах требующих

реализации длинных операций.

Специализированные схемы, как правило,

сочетали программную и аппаратную

реализацию, что позволяло выполнять

также операции за несколько тактов

(5-6). Но это направление было оправдано,

если в задачах постоянно встречались

эти операции. В универсальных ВМ они

встречались не столь часто, поэтому в

них арифметический сопроцессор.

Увеличение интеграции позволило

разместить на кристалле большее число

элементов и интегрировать сопроцессор

в основной кристалл, либо сделать

кристалл сопроцессора рядом с основным

кристаллом. Это направление привело

также к введению буферной памяти команд

и данных в структурах микропроцессора.

бщие

сигналы управления при получении кода

длинной команды. Основной процессор

блокируется, операция выполняется

сопроцессором. Это направление получило

распространение в системах требующих

реализации длинных операций.

Специализированные схемы, как правило,

сочетали программную и аппаратную

реализацию, что позволяло выполнять

также операции за несколько тактов

(5-6). Но это направление было оправдано,

если в задачах постоянно встречались

эти операции. В универсальных ВМ они

встречались не столь часто, поэтому в

них арифметический сопроцессор.

Увеличение интеграции позволило

разместить на кристалле большее число

элементов и интегрировать сопроцессор

в основной кристалл, либо сделать

кристалл сопроцессора рядом с основным

кристаллом. Это направление привело

также к введению буферной памяти команд

и данных в структурах микропроцессора.

П ри

передаче по ШД КОП и данных не мало

ситуаций, когда по шине ничег

ри

передаче по ШД КОП и данных не мало

ситуаций, когда по шине ничег о

не передается, т.к. процессор выполняет

текущую команду. Чтобы повысить

производительность, предложено в

«свободные окна» на ШД передавать коды

следующих команд, расположенных по

нарастанию адресов. Но для их хранения

на кристалле нужна память, поэтому

начали выполнять отдельный третий

кристалл «кэш» память. Таким образом,

микропроцессор стал состоять минимум

из 3 частей. Такая конструкция размещается

на посадочном месте в корпусе ИМС и

коммутируется между собой локальной

шиной в корпусе. Это же идея развита на

кристалле основного, где дополнительно

РОН выполняется буферная память данных

с тем, что бы снизить число обращений

процессора во внешнюю память данных.

Т.о. введение в буферной памяти команд

и данных позволило заметно повысить

производительность схемы. Команды

загрузки выполняются традиционно, а

процедуры преобразования – данные не

выходят на ШД. Буферная память приводит

к тому, что программа располагается

сегментами. Переход внутри сегментов

не проводит к смене содержимого буферной

памяти. Выход за пределы сегмента –

перезапись нового сегмента в буферную

память команд. Разработаны схемы с

коротким набором команд RISC

микропроцессор. В них введет конвейерный

подход к преобразованию. Одновременно

несколько команд выполняются в различных

фазах. Самая первая команда заканчивается

–последняя, начинается. Те же команды

разбиты на простые фрагменты.

о

не передается, т.к. процессор выполняет

текущую команду. Чтобы повысить

производительность, предложено в

«свободные окна» на ШД передавать коды

следующих команд, расположенных по

нарастанию адресов. Но для их хранения

на кристалле нужна память, поэтому

начали выполнять отдельный третий

кристалл «кэш» память. Таким образом,

микропроцессор стал состоять минимум

из 3 частей. Такая конструкция размещается

на посадочном месте в корпусе ИМС и

коммутируется между собой локальной

шиной в корпусе. Это же идея развита на

кристалле основного, где дополнительно

РОН выполняется буферная память данных

с тем, что бы снизить число обращений

процессора во внешнюю память данных.

Т.о. введение в буферной памяти команд

и данных позволило заметно повысить

производительность схемы. Команды

загрузки выполняются традиционно, а

процедуры преобразования – данные не

выходят на ШД. Буферная память приводит

к тому, что программа располагается

сегментами. Переход внутри сегментов

не проводит к смене содержимого буферной

памяти. Выход за пределы сегмента –

перезапись нового сегмента в буферную

память команд. Разработаны схемы с

коротким набором команд RISC

микропроцессор. В них введет конвейерный

подход к преобразованию. Одновременно

несколько команд выполняются в различных

фазах. Самая первая команда заканчивается

–последняя, начинается. Те же команды

разбиты на простые фрагменты.

Первые применения RISC архитектуры совмещались с традиционной. Структура RISC микропроцессоров более регулярна, но устройствам управления – сложнее.

Структуры вычислителей

вычислитель на ОМП

структура на СМП

организация шин в вычислителях на МП.

(1)

Вариации в структуре вычислителя возможны в организации ША и ШД. Так, например ША формируется из старших разрядов по ША и младших по ШД. Чтобы адрес сохранялся, цикл процессора введен регистр адреса, содержимое которого фиксируется по сигналу синхронизации. ШД сформирована через буфер данных (ВА) двунаправлена. Управление буфером данных – сигналом запись/чтение процессора. Схема ОЗУ ПЗУ порт I/Out выбираются адресными дешифраторами, поэтому при проектировании структуры все адресное пространство делят на области. Как правило самая большая – ОЗУ. Например: она занимает32К. Это половина. Рекомендуют размещать ее в верхней части ОЗУ – 8К, чтобы разделить дешифратором, необходимо определить число частей. В простейшем варианте всю область памяти делим на 4 равных части: 16К-ПЗУ, 16К- ПОРТ, 32К – ОЗУ. С этой целью используем дешифратор 2 в 4. На вход подаем А15,А14 – два старших разряда.

А14 |

А15 |

|

0 |

0 |

ПЗУ |

0 |

1 |

Порт в/выв |

1 |

0 |

ОЗУ |

1 |

1 |

ОЗУ |

С соответствующих выходов дешифратора согласно таблице подаем сигналы на входы разрешение выборки кристалла. Для ОЗУ необходима схема И объединяющая два вы хода дешифратора. Управляющие сигналы r/w берутся с выхода процессора либо с системного контроллера и подаются на соответствующие входы блоков. Возможна ситуация, когда объем ОЗУ ПЗУ превышает 64К. в этом случае рассматривается два адресных пространства: первое для ОЗУ, второе – ПЗУ, порты и тд. Переключение адресных пространств – сигналами контроллера – фаза выборки, чтение/запись и т.д.

В реальных схемах число порто I/Out может быть значительно, поэтому число областей в адресном пространстве 6-10.поэтому можно применить двойной дешифратор. Первый «грубый», у которого один выход обращения к ВУ, второй включается этим выходом и обеспечивает разделение с помощью младших разрядов адреса.

Для ОМП с общей шиной (К1801) необходимо сформировать адресные дешифраторы и адресные регистры на каждом функциональном блоке. Каждый блок имеет на входе адресный регистр с дешифрацией. Если адресное пространство его в регистр записывается – адрес и блок становится активными. Все остальные блоки не выбраны. Однокристальные микроЭВМ имеют в своем составе порты и некоторую память, поэтому структура контроллера отличается лишь блоком процессора. Способы подключения ВУ аналогичны. Контроллер на основе ОМП используют в промышленных системах управления, отображения информации ввода вывода. Их относительная черта – невысокая производительность, при несложных аппаратных затратах.

(2) Основное отличие этой структуры в том, что процессор имеет более сложное построение чем, в первом варианте. Это связано с тем, что необходимо обеспечить работоспособность секций и связь их между собой. Кроме этого блок микропрограммного управления также имеет немалые аппаратные средства.

Четыре секции включены параллельно: младшая, старшая – по краям, на входе каждой секции поступает часть разряда, например 4. Выходные разряды секций также компенсируются, обеспечивая выходную разрядность равную входной. ШД образуется двумя регистрами входом и выходом. Причем, регистр входа должен третье состояние. ША формируется отдельным регистром, при разрядность ее зависит от задания. Если разрядность ША<ШД используются младшие выходные разряды секции, если разрядность ША>ШД – он выводится из внутренних регистров секций за два такта, младшие и старшие части. В секциях нет отдельно выделенных регистров адреса, поэтому в качестве него применяют одну из РОН секций. Между собою секции объединяются через выходы сдвиговых разрядов. Краткие выводы этих разрядов коммутируются через мультиплексор. С помощью отдельных разрядов микрокоманды мультиплексора настаиваются на левые или правые сдвиги. Для организации ускоренного переноса используют блок ускоренного переноса (СУП). На ее выходы подключают сигналы распространения и генерации переноса. Выходы СУП – на входной перенос следующей секции. Одна такая схема работает с 4 секциями. Со старшей секцией снимают признаки, причем, признак Z объединяется со всеми секциями. Признаки хранятся в регистре. Блок микропрограммного управления имеет типовую структуру. Управляющая часть – форматы микрокоманд распределяется между регистрами, мультиплексорными ключами, обеспечивая синхронизацию во времени. Непосредственно микрокоманды поступают на каждую секции параллельно. Одни и те же разряды на каждую секцию. Это схема позволяет выполнять операции как над одинарной длины так и над операндами.

Процессорный блок на СМП отличается большей аппаратной сложностью, но позволяет гибко изменять разрядность адреса и данных процессора.

(3) Контроллеры имеют простейшую архитектуру т.к. ориентированы на режим программного обмена, невысокую скорость. В вычислителях стремятся разделить информационные потоки между процессором - памятью, и памятью – ВУ. При передаче информации из памяти в ВУ процессор может выполнять внутренние пересылки, арифметику. В связи с чем применяют разделение ША и ШД на : локальную, системную, шину памяти , расширения.

Примером структурной организации является построение IBM PC

Как и в типовой структуре контроллера здесь используется системный (шинный ) контроллер, формирующий сигналы управления, включения и выключения блоков. Локальная шина L объединяет процессор, сопроцессор, кэш и в старших моделях МП находится внутри корпуса. Буферы между шинами разрывают связи, чтобы обеспечить требуемое направление передачи. Причем буфер связывающий L и S шины включается в режиме ПДП.