- •Содержание

- •История развития микропроцессорной техники Классификация микропроцессорных средств

- •Основные определения

- •Архитектура cpu

- •Программная модель cpu.

- •Организация памяти базового мк. Память данных (пд) Карта памяти данных

- •Внешняя память мк

- •Карта памяти программ (пп)

- •Расширенная память

- •Организация sfr регистров

- •Система команд микроконтроллеров семейства mcs-51 Режимы адресации

- •Встроенные периферийные устройства мк

- •Альтернативные функции

- •Архитектура таймеров-счетчиков.

- •Форматы регистров управления. (sfr)

- •Tmod – режим (sfr)

- •Последовательный порт uart (асинхронный приёмопередатчик)

- •Форматы регистров управления Регистр управления последовательным портом scon

- •Регистр управления мощностью pmod

- •Скорость обмена данными для последовательного порта

- •Система прерываний

- •Особенности системы прерываний

- •Ie(разрешение прерываний)

- •Особенности системы прерываний мк Infineon 80c535

- •Дополнительный регистр запроса прерываний

- •Регистры приоритетов прерываний

- •Узел генератора

- •Регистры специального назначения.

- •Порты ввода-вывода

- •Цифровой коммутатор и приоритетный дешифратор

- •Форматы регистров конфигурирования

- •Особенности работы cpu. Особенности центрального процессорного устройства cip51.

- •Архитектура и программирование аналого-цифрового преобразователя(ацп)

- •Устройство выборки и хранения на входе ацп

- •Форматы регистров конфигурирования

- •Калибровка

- •Узел прямого доступа к памяти (dma)

- •2 Режима работы dma

- •2 Регистра управления dma

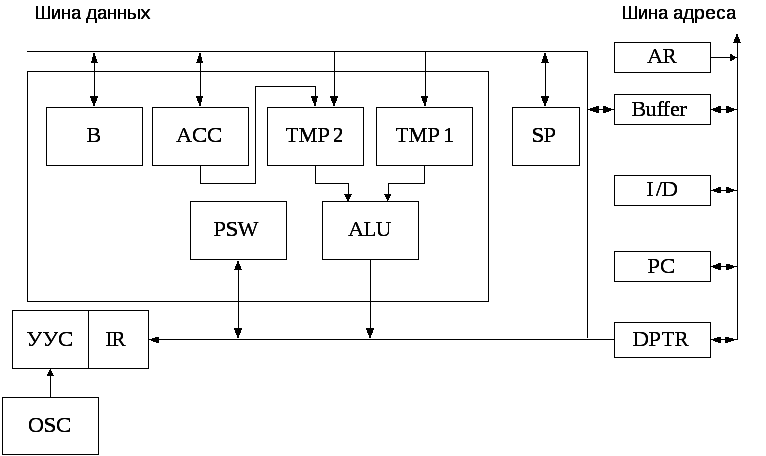

Архитектура cpu

Рассмотрим CPU семейства микроконтроллеров MCS-51.

Схема 5. Архитектура центрального процессора базовой модели МК I8051

В данной архитектуре присутствуют:

два регистра временного хранения – TMP;

ALU – комбинационная схема без элементов памяти;

В – регистр расширения аккумулятора (дополнительный регистр), служит для хранения старшего байта результата операций;

PSW – регистр состояния процессора («регистр флагов условий»), позволяет выполнять условные переходы в программе;

SP – стек (организуется в памяти данных);

OSC – осциллятор;

DPTR – указатель данных;

IR – регистр инструкций;

PC – адрес команды;

УУС – устройство управления и синхронизации.

Программная модель cpu.

Программная модель показывает только те регистры, которые доступны программисту.(PSW, SP, TMP, PC, DPTR, IR).

Модель поддерживает аккумуляторно-ориентированную архитектуру : первый операнд должен быть размещён в аккумуляторе, откуда он автоматически копируется в TMP1, второй операнд находится с помощью режима адресации памяти и помещается в TMP2. Далее результат из АЛУ по шине данных передается в аккумулятор. Если аккумулятор двухтактовый, то на Схеме 3 регистр TMP1 не обозначается.

Рассмотрим регистр PSW, в котором устанавливаются флаги логических и арифметических операций.

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

С |

AC |

F0 |

RS0 |

RS1 |

OV |

F1 |

P |

C – перенос для беззнаковой арифметики(С = 1, значит вышли за пределы 255)

OV – флаг перехода для знаковой арифметики

AC – дополнительный перенос, фиксирует перенос из 3 разряда в 4ый(из младшей тетрады в старшую). Позволяет использование BCD (binary coded decimal) формата

P – флаг паритета (четный и нечетный паритет)

Сумма единиц в регистре и флаге Р должна быть четной, это позволяет контролировать результат.

F0, F1 – флаги пользователя

RS0, RS1 – позволяют выбрать 1 из 4х банков регистров в RAM-памяти.

|

RS1 |

RS0 |

Bank |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

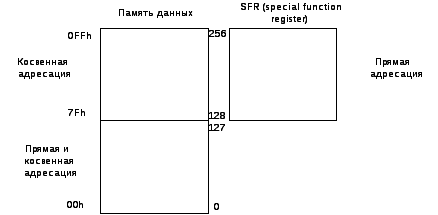

Организация памяти базового мк. Память данных (пд) Карта памяти данных

Карта памяти данных показывает конкретную организацию внутренней и внешней памяти, а также регистров общего (GPR – general purpose register)и специального назначения (SFR – special function register)

ОЗУ 256 Б (RAM)

Схема 6. Карта памяти данных

RAM(0÷127)

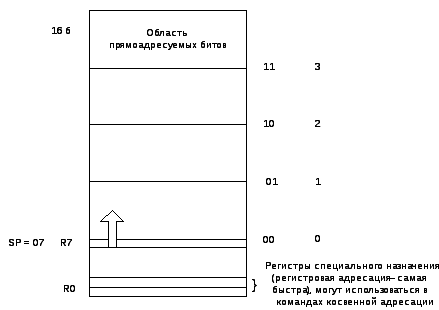

Схема 7. Область памяти данных

4 банка, 8 регистров

C адреса 20h по 2Fh – пространство адресуемых бит, дальше RAM память данных.

Пример команд косвенной адресации:

mov A, @R0

mov A, @R1

Стек памяти работает с прединкрементом, т.е. первый элемент хранится по адресу 08h. Стек можно установить где угодно, важно знать его глубину.

В SFR области есть регистры, к которым можно адресоваться побитно. Регистры специального назначения представляют собой регистры управления, предназначенные для программирования узлов МК. Их количество определяется количеством узлов.