- •Содержание

- •14 Устройства преобразования сигналов……………………...68

- •23 Последовательностные логические устройства……..102

- •Модуль 1. Элементная база электронных устройств

- •1 Современные методы проектирования электронных устройств и пассивные элементы

- •1.1 Основные этапы проектирования электронных устройств и параметры электрических сигналов

- •Частота сигнала будет

- •Резисторы, варисторы и конденсаторы. Условное графическое обозначение, виды, параметры и маркировка

- •1.3 Катушки индуктивности, трансформаторы и электромеханические элементы (переключатели, разъемы и т.Д.)

- •2 Полупроводниковые диоды

- •2.1 Принцип действия полупроводникового диода, его условное обозначения, характеристики и параметры

- •2.2 Математические модели диодов и их применение для анализа электрических схем

- •Обратное включение

- •Для расчета схем с диодами применяют часто графо – аналитический метод который представляет графическое решение систем уравнений. Пример образованный параметрами схемы графо-аналитическим методом.

- •2.3 Разновидности полупроводниковых диодов, их классификация и система обозначений

- •3 Биполярные транзисторы

- •3.1 Устройство и принцип действия биполярных транзисторов различного типа проводимости. Условные графические обозначения, классификация и маркировка

- •Структура биполярных транзисторов

- •3.2 Схемы включения биполярного транзистора

- •3.3 Математические модели биполярного транзистора для различных схем включения

- •Свойства

- •4 Полевые транзисторы и приборы с отрицательным сопротивлением.

- •4.1 Устройство и принцип действия полевых транзисторов с p-n переходом и с изолированным затвором

- •4.2 Схемы включения и математические модели полевых транзисторов

- •4.3 Тиристоры. Принцип действия, параметры и маркировка

- •4.4 Однопереходные транзисторы и туннельные диоды

- •5 Полупроводниковые датчики и индикаторные приборы

- •5.1 Полупроводниковые датчики температуры и усилия

- •5.2 Магнитно-полупроводниковые приборы

- •5.3 Источники и приёмники оптического излучения

- •Полупроводниковые лазерные диоды(аналогичны излучающим диодам, только после Iпр.Граничное происходит излучение когерентное и значительно увеличивается его мощность.)

- •5.4 Индикаторные приборы и их применения

- •Модуль 2. Схемотехника аналоговых и импульсных электронных устройств

- •6 Электронные усилители

- •6.1 Назначения усилителей, их параметры и характеристики

- •6.2 Обратная связь в усилителях и её разновидности

- •7 Усилительный каскад на биполярном транзисторе по схеме с общим эмиттером

- •7.1 Анализ работы усилительного каскада в режиме покоя

- •7.2 Эквивалентная схема замещения каскада. Расчет параметров усиления

- •8 Схемотехнические усилители каскадов на биполярных и полевых транзисторов

- •8.1 Усилительные каскады с общими коллектором и базой

- •8.2 Особенности применения полевых транзисторов усилительных каскадов

- •8.3 Пути повышения коэффициента усиления усилительных каскадов

- •9 Схемотехника Усилителей постоянного тока

- •9.1 Усилители постоянного тока на транзисторах с непосредственной связью и особенности его проектирования

- •9.2 Дифференциальные каскады на полевых и биполярных транзисторах

- •10 Усилители мощности

- •10.1 Общая характеристика и основные параметры

- •10.2 Двухтактный усилитель

- •11 Операционные усилители (оу)

- •11.1 Назначение, структура и основные характеристики операционного усилителя

- •11.2 Схемотехника усилителей на оу

- •12 Активные фильтры

- •12.1 Общие математические описания и классификация фильтров. Пассивные фильтры

- •12.2 Схемотехника активных фильтров

- •13 Работа полупроводниковых приборов в ключевом режиме

- •13.1 Ключевой режим

- •14 Устройства преобразования сигналов

- •14.1 Схемы положительных и отрицательных сигналов

- •14.2 Схемотехника нелинейных преобразователей аналоговых сигналов

- •15 Источники вторичного электропитания

- •15.1 Структурные схемы

- •15.2 Однофазные выпрямители

- •16 Непрерывные стабилизаторы постоянного тока

- •16.1 Общие положения

- •16.2 Компенсационные стабилизаторы

- •17 Импульсные и ключевые регуляторы и стабилизаторы постоянного напряжения

- •17.1 Основные требования ир. Статические и динамические потери

- •17.2 Режимы импульсного регулирования мощности и схемы импульсных усилителей

- •17.3 Схемотехника ключевых стабилизаторов им методика их расчёта

- •Квыпр c1

- •18 Многофазовые выпрямители и сглаживающие фильтры

- •18.1 Трёхфазные выпрямители и их схемотехника

- •18.2 Сглаживающие фильтры и особенности работы выпрямителя на ёмкостную нагрузку

- •18.3 Внешние характеристики и методика расчётов выпрямителя

- •19 Электронные регуляторы переменного напряжения

- •19.1 Способы изменения переменного напряжения

- •19.2 Схемотехника электронных регуляторов переменного напряжения

- •19.3 Энергетические характеристики вентильных преобразователей и их влияние на питающую сеть

- •20 Транзисторные преобразователи напряжения

- •20.1 Схемы преобразователей

- •20.2 Расчет преобразователей

- •22 Комбинационные логические устройства

- •22.1 Синтез логических устройств

- •22.2 Типовые комбинационные устройства

- •23 Последовательностные логические устройства

- •23.1 Триггеры

- •23.2 Регистры

- •23.3 Счетчики

- •24 Аналого – цифровые и цифро – аналоговые схемы

- •24.1 Компаратор

- •24.2 Интегральный таймер

- •24.3 Цифро – аналоговые преобразователи (цап)

- •24.4. Аналого – цифровые преобразователи (ацп)

- •Литература

22 Комбинационные логические устройства

22.1 Синтез логических устройств

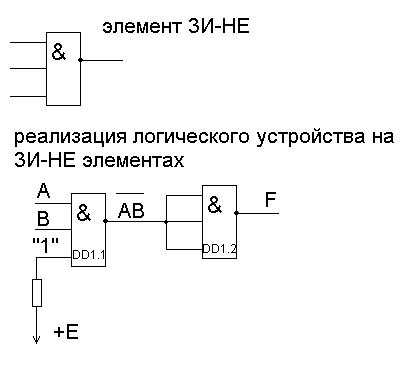

Любое логическое устройство выполняется на конкретной элементной базе. Перед проектированием составляется алгоритм работы и записывается ФАЛ устройства. Для построения любых устройств достаточно иметь:

2И – HЕ, Переход

При реализации логического f встречаются случаи когда логические элементы имеют больше входов, чем число переменных, поэтому некоторые входы остаются свободными. В реальных условиях свободные входы оставлять не допускается. Два способа подключения неиспользованных входов:

-

неиспользованный вход соединяется со входом на который подается переменная.

-

на неиспользованный вход подается пассивный уровень для данного логического элемента.

Пассивным – называется логический сигнал (о или t), который не меняет состояние элемента.

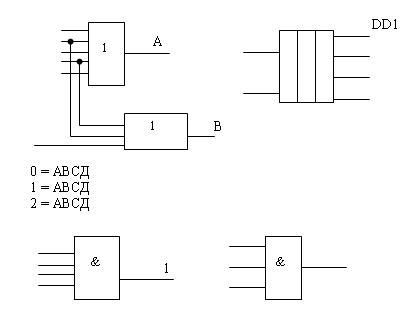

22.2 Типовые комбинационные устройства

|

Дес. Код |

Д |

С |

В |

А |

|

0 1 2 3 |

0 0 0 0 |

0 0 0 0 |

0 0 1 1 |

0 1 0 1 |

|

4 5 6 7 |

0 0 0 0 |

1 1 1 1 |

0 0 1 1 |

0 1 0 1 |

|

8 9 |

1 1 |

0 0 |

0 0 |

0 1 |

А = 1+3+7+9+5=25

В = 2+3+6+7=18

С = 4+5+6+7=22

Д = 8+9=17

Избыточные состояния можно использовать для минимизации.

Шифратор – преобразователь кодов

Дешифратор – выполняет обратную операцию

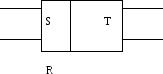

Мультиплексор – устройство выполняющие коммутацию (соединение нескольких входов на один выход), при нем номер входа определяется адресом, например, нам необходимо

F = до * А0 * А1 + Д1 * А0 * А1 + Д2 * А0 * А1 + Д3 * А0 * А1

MX

F

F

Демультиплексор – устройство которое подключает единственный вход на множество выходов.

23 Последовательностные логические устройства

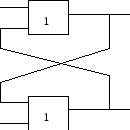

23.1 Триггеры

Триггерные устройства (триггеры) предназначены для запоминания цифровой информации. Могут быть построены на транзисторах, логических элементах, операционных усилителях и других устройствах. Обычно триггер имеет как минимум одно устойчивое состояние. Триггер строится на двух усилительных каскадах, которые охватывают полож. обр. св. Триггеры бывают асинхронные и синхронные. Триггеры имеют один либо два выхода, один – прямой, другой – инверсный. Входы триггера определяют его функциональные возможности.

RS- триггер, который служит как ячейка памяти. Вход S – вход установки (на прямом выходе устанавливает логич. 1.. 2ой входы.). R- вход сброса, на прямом выходе – логич. 0. Выход триггера обозначается Q.

Q-прямой

![]() -

инверсный

-

инверсный

Состояние триггера характеризует его таблица состояния. Указанный триггер может находиться в двух устойчивых или неустойчивых состояниях.

R Q

R Q

(0)

1 (1)

![]()

0 1 (0)

S

R S

R S

![]()

![]()

0 0 0 0

0 0 0

0 1 0 1

1 0 0 0

1 1 0 *

0 0 1 1

0 1 1 1

1 0 1 0

1 1 1 *

1 1 *

*запрещённое состояние для этого триггера.

DD1

RS - триггер является асинхронным.

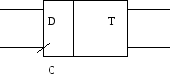

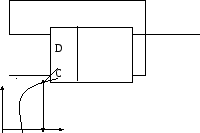

D - триггер синхронный.

Информация на входе D появляется.

D0

C0

Q0

T-триггер

Q 01

10

вход

10

U

0

Tтр – делитель частоты, на Ттр строятся пересеченные схемы.

0

Q

0