- •Кафедра Автоматизированные и вычислительные системы курсовой проект

- •Факультет автоматики и электромеханики Кафедра Автоматизированные и вычислительные системы

- •Замечания руководителя Содержание

- •Введение

- •1 Обобщённая структура и принцип функционирования суа

- •1.1 Функции блока памяти

- •1.2 Функции логического преобразователя

- •1.3 Программируемые логические матрицы

- •1.4 Последовательность синтеза синхронных управляющих автоматов

- •2 Анализ граф схемы алгоритма суа и детализация бп

- •2.1 Разметка граф-схемы алгоритма

- •2.2 Составление структурной таблицы переходов и выходов

- •2.3 Структурное кодирование внутренних состояний суа

- •2.4 Детализация блока памяти

- •3 Структурный синтез логического преобразователя

- •3.1 Разработка расширенной структурной таблицы переходов и выходов

- •3.2 Составление логических уравнений для выходных сигналов и функций возбуждения триггеров

- •3.3 Минимизация логических уравнений

- •4 Разработка схемы электрической функциональной суа

- •Заключение

- •Список литературы

2.4 Детализация блока памяти

Целью данного этапа является разработка схемы электрической функциональной блока памяти синтезируемого автомата, который должен быть реализован заданном типе триггерных схем. По сути, блок памяти представляет собой r триггеров, электрически соединённых определенным образом, или, иначе говоря, представляет одну r – разрядную ячейку памяти. В вычислительной технике такую организацию триггеров принято называть r – разрядным регистром.

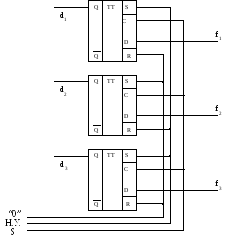

Для реализации блока памяти заданы комбинированные JK-триггеры, которые можно преобразовать в D – триггеры или в Т – триггеры. Модификация JK - триггеров позволяет не только уменьшить сложность логического преобразователя, но и повысить надежность синтезируемого автомата, так как устраняются запрещенные входные комбинации на информационных входах триггеров. Реализованная схема БП представлена на Рисунке 6.

Рисунок 6

3 Структурный синтез логического преобразователя

3.1 Разработка расширенной структурной таблицы переходов и выходов

Исходными данными для составления расширенных структурных таблиц переходов и выходов являются данные Таблицы 1 и Таблицы 2.

Расширенные структурные таблицы переходов и выходов отличаются от таблицы 1 введением дополнительных граф, содержащих информацию о структурном коде состояния автомата в текущий момент времени К(аm), о структурном коде автомата в последующий момент времени К(аs), а также структурный код функции возбуждения блока памяти F(аm,аs), который должен формироваться логическим преобразователем для подготовки перехода автомата из состояния аm в состояние аs. В зависимости от используемых триггерных схем функция возбуждения F(аm,аs) определяется различным образом.

При использовании D – триггеров функция возбуждения блока памяти находится на основании следующего уравнения:

![]() . (6)

. (6)

Из уравнения (6) следует следующая система уравнений:

(7)

(7)

Для исходного синхронного управляющего автомата структурная расширенная таблица переходов и выходов представлена Таблицей 3.

Таблица 3

|

am |

K(am) |

as |

K(as) |

X (am, as) |

Y (am, as) |

F(am, as) |

|||||||||

|

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

Q2 |

Q1 |

Q0 |

f3 |

f2 |

f1 |

f0 |

||||

|

a1 |

1 |

0 |

1 |

0 |

a7 |

0 |

1 |

0 |

0 |

|

- |

0 |

1 |

0 |

0 |

|

a2 |

0 |

1 |

1 |

0 |

|

|

0 |

1 |

1 |

0 |

|||||

|

a2 |

0 |

1 |

1 |

0 |

a3 |

0 |

0 |

1 |

0 |

|

|

0 |

0 |

1 |

0 |

|

a3 |

0 |

0 |

1 |

0 |

|

- |

0 |

0 |

1 |

0 |

|||||

|

a8 |

1 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

1 |

|||||

|

a9 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

|||||

|

a3 |

0 |

0 |

1 |

0 |

a4 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

|

a4 |

0 |

1 |

0 |

0 |

а5 |

0 |

1 |

0 |

1 |

|

|

0 |

1 |

0 |

1 |

|

а9 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

|||||

|

a5 |

0 |

1 |

0 |

1 |

a6 |

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

|

a6 |

1 |

0 |

0 |

0 |

a7 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

a7 |

0 |

1 |

0 |

0 |

а1 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

Продолжение Таблицы 3

|

am |

K(am) |

as |

K(as) |

X (am, as) |

Y (am, as) |

F(am, as) |

|||||||||

|

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

Q2 |

Q1 |

Q0 |

f3 |

f2 |

f1 |

f0 |

||||

|

a8 |

1 |

0 |

0 |

1 |

a3 |

0 |

0 |

1 |

0 |

|

|

0 |

0 |

1 |

0 |

|

a3 |

0 |

0 |

1 |

0 |

|

- |

0 |

0 |

1 |

0 |

|||||

|

a9 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

|||||

|

a9 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

|||||

|

a9 |

0 |

0 |

0 |

1 |

а9 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

|

a10 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

1 |

1 |

|||||

|

a10 |

0 |

0 |

1 |

1 |

a10 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

1 |

1 |

|

а6 |

1 |

0 |

0 |

0 |

|

|

0 |

1 |

1 |

1 |

|||||