- •Архитектура пэвм

- •Пользовательские регистры

- •Регистры общего назначения

- •Сегментные регистры

- •Регистры состояния и управления

- •Регистры защищенного режима:

- •Организация памяти (реальный режим)

- •Элементы синтаксиса Ассемблера

- •Операторы

- •Директивы сегментации

- •Модели памяти

- •Идентификаторы, создаваемые директивой Model:

- •Этапы создания программы на ассемблере

- •2. Создание объектного модуля (трансляция программы)

- •3. Создание загрузочного модуля (компоновка программы)

- •4. Отладка программы

- •Определение простых типов данных:

- •Способы адресации Регистровая адресация

- •Непосредственная адресация

- •Способы адресации памяти

- •Переопределение сегмента

- •Особенности пересылки данных

- •Xch ax, bx ; команда двунаправленного обмена

- •Команды работы с адресами и указателями

- •Команды сдвига

- •Команды линейного сдвига

- •Команды циклического сдвига

- •Команды сдвига двойной точности

- •Примеры работы с битовыми полями

- •Команды преобразования данных

- •Xor ax, ax ; очистка регистра ax

- •Int 21h ;ожидание вода с клавиатуры

- •Команды обработки строк

- •Команды пересылки строк

- •Команды сравнения строк

- •Пример.

- •Сканирование строки

- •Загрузка элемента строки в аккумулятор

- •Перенос элемента из аккумулятора в строку

- •Ввод элемента цепочки из порта в строку

- •Вывод элемента цепочки в порт

- •Пример использования вложенных циклов

- •Массивы

- •Логические команды

- •Xor операнд1,операнд2

- •Логические команды поиска

- •Структуры

- •Описание шаблона структуры:

- •Заполнение шаблона:

- •Работа с полями структуры

- •Пример:

- •Шаблон записи:

- •Xor bl, mask i2 ; обнуление

- •Команды передачи управления

- •Безусловные переходы

- •Межсегментные переходы

- •Второй сегмент

- •Команды условного перехода

- •Команды условного перехода и флаги

- •Процедуры

- •Процедура в начале кодового сегмента

- •Процедура в конце кодового сегмента

- •Процедура в теле сегмента

- •Вызов процедуры

- •Ret [число]

- •Способы вызова процедуры

- •Прямой ближний вызов

- •Прямой дальний вызов

- •Косвенный ближний вызов

- •Косвенный дальний вызов процедуры

- •Организация интерфейса между процедурами, расположенными в разных модулях

- •Передачи параметров в процедуру через регистры

- •Фрагмент модуля 2

- •Возврат результата из процедуры

- •Макрокоманды и макроопределения

- •Особенности трансляции при получении объектного модуля

- •Где можно разместить макроопределение?

- •Связь Assembler с языками высокого уровня

- •Операторы типа inline

- •Ассемблерные вставки

- •Внешние процедуры Операторы типа inline

- •Ассемблерные вставки

- •Требования к программе на языке Assembler

- •Требования к программе на языке Pascal

- •Передача параметров из Pascal-программы в программу на ассемблере

- •Использование директивы model для организации взаимодействия программ

- •Int 10h; вывод символа

- •Возврат данных в вызывающую программу

- •Пример взаимодействия программ

- •Особенности com-программы

- •Пример программы типа .Com

- •Резидентные программы

- •Формат резидентной программы

- •Собственно программу.

- •Функцию записи в оп адреса точки входа программы для последующего вызова.

- •Функцию, которая оставляет программу резидентной.

- •Пример резидентной программы типа .Com

- •Iret ;возврат из процедуры

- •Int 27h ; оставляем программу резидентной

- •Вызов резидентной программы

- •Запись адреса резидентной программы в область межзадачных связей

- •Iret ;возврат из процедуры

- •Int 27h ; оставляем программу резидентной

- •Вызов резидентной программы через область межзадачных связей

- •Передача параметров в резидентную программу

- •Замена существующего вектора прерывания

- •Динамическое распределение памяти

- •Пример выделения и освобождения блока памяти

- •Int 21h ;блока памяти

- •Дочерние процессы

- •Особенности структуры материнской программы

- •Активизация дочернего процесса

- •Пример материнской программы

- •; Запуск дочернего процесса

- •Int 21h ; запуск дочернего процесса

- •Int 21h ; выход в ос (завершение программы)

- •Получение и анализ кода возврата в материнской программе

- •Int 21h ; код возврата передается через регистр al

- •Передача кода возврата из дочерней программы

- •Прерывания

- •Программируемый контроллер прерываний

- •Прохождение запроса на прерывание через контроллер

- •Программирование контроллера прерываний

- •Формат приказов icw

- •Формат приказов ocw

- •И f спользование таймера в программах на Assembler

- •Формирование задержки

- •Использование прерываний 8h для управления запуском программ

- •Программирование коммуникационного порта (com)

- •Микросхема uart 8250

- •Инициализация порта

- •Пример программы инициализации порта

- •Регистр статуса линии (порта)

- •Работа порта без использования механизма прерываний

- •Получение данных

- •Передача данных

- •Алгоритм работы программы приема /передачи без прерываний

- •Текст программы

- •Работа com – порта в режиме прерываний

- •Регистр разрешения прерываний

- •Регистр идентификации прерывания

- •Вызов обработчика прерывания

- •Управление модемом через порт

- •Пример установления связи через порт и модем

- •Защищенный режим микропроцессора

- •2. Регистры отладки

- •3. Регистры управления Регистры системных адресов

- •Структура дескрипторных таблиц

- •Локальная дескрипторная таблица (ldt)

- •Структура дескриптора:

- •Структура байта ar

- •Обработка прерываний в защищенном режиме

- •Особенности обработки ловушек

- •Шлюз задачи

- •Дескриптор tss

- •Структура шлюза вызова

-

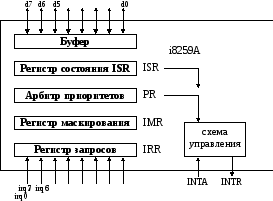

Программируемый контроллер прерываний

irq0 … irq7 – выводы запросов на прерывания для входных сигналов от внешних устройств

IRR – регистр фиксации запросов на прерывание от внешних устройств (соответствующий разряд регистра устанавливается в 1)

IMR –регистр маскирования прерываний от устройств, подключенных к контроллеру. Единицы, установленные в разрядах регистра, запрещают прерывания от соответствующих устройств.

PR – определяет приоритетность обслуживания одновременно поступивших запросов на прерывание

ISR – фиксирует уровень приоритета прерывания, которое в данный момент обрабатывается микропроцессором

Буфер – к нему подключаются входы/выходы системной шины. По ним передается номер вектора прерываний и принимается управляющая информация.

Таблица соответствия уровней irq , номеров прерываний и приоритетов:

|

|

Уровень |

Приоритет |

Номер прерывания |

|

Таймер |

irq0 |

2 |

8h |

|

Клавиатура |

irq1 |

3 |

9h |

|

Выход INT ведомого |

irq2 |

|

0Ah |

|

Часы реального времени |

irq8 |

4 |

70h |

|

|

irq9 |

5 |

71h |

|

|

irq10 |

6 |

72h |

|

|

irq11 |

7 |

73h |

|

|

irq12 |

8 |

74h |

|

Ошибка процессора |

irq13 |

9 |

75h |

|

Контроллер жесткого диска |

irq14 |

10 |

76h |

|

|

irq15 |

11 |

77h |

|

COM2 |

irq3 |

12 |

0Bh |

|

COM1 |

irq4 |

13 |

0Ch |

|

LPT2 |

irq5 |

14 |

0Dh |

|

Контроллер гибкого диска |

irq6 |

15 |

0Eh |

|

LPT1 |

irq7 |

16 |

0Fh |

Прохождение запроса на прерывание через контроллер

-

Сигнал запроса поступает на вход irqx и устанавливает соответствующий бит регистра IRR в «1».

-

Регистр маски IMR определяет, какие прерывания разрешены (0 – разрешены, 1- запрещены).

-

Если бит IMR=0, то сигнал поступает к регистру приоритета PR. Самый высокий приоритет у уровня irq0. Конфликт возникает, если на входах регистра PR одновременно несколько запросов.

-

Регистр PR выбирает запрос на прерывание с наивысшим приоритетом и предает сигнал на схему управления, которая формирует сигнал INT, поступающий на вход INTR микропроцессора.

-

Если прерывания разрешены (IF=1, TF=0), то микропроцессор сбрасывает флаг (IF=0) (запрещает аппаратные прерывания) и передает контроллеру сигнал подтверждения INTA.

При поступлении сигнала INTA контроллер выполняет следующее:

-

Сбрасывает бит в регистре IRR,

-

Устанавливает бит в регистре ISR, соответствующий входу irq (фиксирует факт обработки прерывания с данным приоритетом),

-

формирует номер вектора прерываний в виде кода на выходах d0 … d7.

Далее происходит обработка прерывания.

Если во время обработки прерывания поступит другой сигнал запроса прерывания того же уровня, то обслуживание запроса будет отложено.

Если поступит запрос более высокого уровня, то текущая процедура обработки остановится, а поступивший запрос вызовет свою процедуру обработки.

Любая процедура, закончив работу, сбрасывает свой бит в регистре ISR, разрешая тем самым обработку прерываний с приоритетами ниже установленного.

Следует помнить, что при запуске обработчика флаг IF будет сброшен и аппаратные прерывания будут запрещены. Обрабатывающая программа должна сама определить, когда внешние прерывания не помешают ее работе. Она может разрешить внешние прерывания (sti) или вновь запретить (cli).