- •Микропроцессоры в технике электросвязи

- •Глава 1. Структура микропроцессорного комплекта 580 серии.

- •Принцип работы

- •1.1. Структура цпэ

- •1.2. Форматы команд

- •1. 3. Виды адресации

- •1.4. Виды выполняемых операций

- •1.5. Примеры программирования микропроцессора

- •1.6. Циклические программы

- •1.7. Система сбора и обработки информации

- •1.8. Система групповой ару аналоговой системы передачи

- •Глава 2. Цифровые развязывающие устройства

- •2.1. Абсолютный компенсационый метод (акм)

- •2. 2. Относительный компенсационный метод (окм)

- •2.3. Структурная схема окм и алгоритм ее работы

- •Глава 3. Однокристалльные микроэвм к 1816 ве 48 (ве 51)

- •3.1. Цифровой цастотный демодулятор (модем)

- •Глава 4. Микропроцессор 1813 ве1

- •Глава 5. Реализация цифровых фильтров (цф) на 1813 ве 1

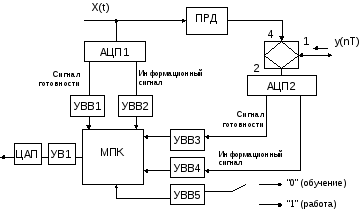

2.3. Структурная схема окм и алгоритм ее работы

Принцип работы.

АЦП 1 включен в тракт передачи для выработки управляющих сигналов адресации.

УВВ1 и УВВ2 вводят сигнал готовности и информационный сигнал соответственно с выхода АЦП1.

УВВ3 и УВВ4 вводят сигнал готовности и информационный сигнал соответственно с выхода АЦП2.

УВВ5 определяет режим работы (рабочий цикл или обучение).

УВ1выводит принимаемый сигнал на ЦАП, откуда он поступает к потребителю.

МПК позволяет организовать принцип относительного компенсационного метода. Алгоритм его работы показан на рис.

Программа работы

К1. М1: IN 1

К2. RLC

К3. JNC M1

К4. IN 2

К5. MOV L, A

К6. MVI H, 0

К7. M2: IN 3

К8. RLC

Алгоритм

К9. JNC M2

К10. IN 4

К11. MOV C, A

К12. IN 5

К13. RLC

К14. JC M3

К15. MOV M, C

К16. MVI A, 0

К17. MVI H, 01

К18. MOV M, A

JMP M1

К19. M3: MOV A, C

К20. SUB A, M

К21. MOV M, C

К22. MVI H, 01

К23. ADD A, M

К24. OUT 1

К25. MOV M, A

JMP M1

Комментарии к алгоритму и программе:

Блоки 1-3: Анализ сигнала готовности с УВВ 1 (АЦП 1)

Блок 4: Ввод информационного сигнала с АЦП 1.

Блоки 5-6: Формирование адреса БП1 и БП».

Блоки 7-9: Анализ сигнала готовности АЦП 2.

Блок 10: Ввод информационного сигнала АЦП 2.

Блок 11: Промежуточное запоминание.

Блоки 12-14: Анализ сигнала с УВВ5: идет рабочий цикл или обучение.

Блок 15: Обучение БП1

Блоки 16-18: Принудительное обнуление БП2.

Блок 19: Промежуточная пересылка.

Блок 20: Работа прямой структуры (ПС)

Блок 21: Обновление БП 1.

Блок 22: Модификация адреса.

Блок 23: Работа ВОС.

Блок 24: Вывод на УВ 1.

Блок 25: Обновление БП 2.

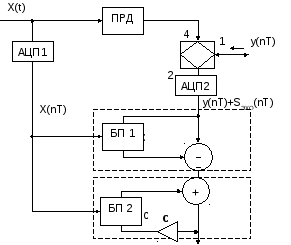

Предложенный алгоритм обладает существенным недостатком: для вхождения в связь необходимо отсутствие сигналов противоположной стороны. Недостаток можно устранить, если во взаимно-обратную структуру включить аттенюатор с коэффициентом передачи близким к 1 (но меньше ее) (рис.2.3.1)

Рисунок 2.3.1. – Структурная схема ОКМ-1.

Рассмотрим работу данной структуры:

n=0 (нулевой цикл): Сигналу на передаче x1(0T) соответствует принимаемый сигнал П1(0Т)+y1(0T):

x1(0T) П1(0Т)+y1(0T). Этот принимаемый сигнал и запишется в БП1.

n=1: x1(1T) П1(1Т)+y2(1T) = П1(0Т)+y2(1T)+1.

На выходе вычитателя будет: y2(1T)+1- y1(0T)

На выходе сумматора будет: y2(1T)+1- y1(0T), т.е. то же, что и на выходе вычитателя, т.к. в нулевом цикле в БП2 был записан ноль.

В БП2 запишется следующее значение: с*[y2(1T)+1- y1(0T)]

n=2: С АЦП2 приходит сигнал П1(2Т)+y3(2T)= П1(1Т)+y3(2T)+2.

На выходе вычитателя: y3(2T)+2- y2(1T).

На выходе сумматора: y3(2T)+2- y2(1T)+ с*[y2(1T)+1- y1(0T)]=

= y3(2T)+2+с*1-(1-с)* y2(1T)-с* y1(0T).

Рассмотрим отдельно каждое слагаемое:

-

с*1 через М циклов обработки превратится в сМ*1. Т. к. с<1, то величина сМ*10.

-

с* y1(0T) через М циклов работы превратится в сМ* y1(0T). Т. к. с<1, то величина сМ* y1(0T) 0.

-

(1-с)* y2(1T)0, т.к. с1.

Таким образом, введение аттенюатора во ВОС позволило выделить новые качества ОКМ: алгоритм стал нечувствителен к появлению принимаемого сигнала с самого начала работы системы. Через М циклов операций дополнительная помеха сМ* yi(0T) 0.

Как реализовать данный алгоритм в цифровой технике?

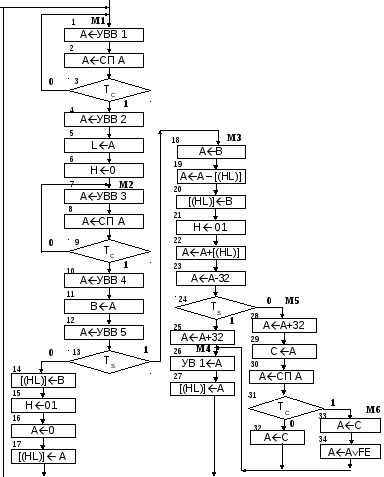

Для реализации функции аттенюатора достаточно проанализировать младший разряд на выходе сумматора. Если величина младшего разряда равна 1, то тогда искусственно обернуть разряд в 0. Если же величина младшего разряда равна 0, то выходной сигнал следует оставить без изменений. Данную операцию можно производить только тогда, когда выходной сигнал представлен как минимум пятью разрядами. Алгоритм ОКМ представлен на рис. 2.3.2.

Программа

К1. М1: IN 1 K30. RRC

К2. RRC K31. JC M6

К3. JNC M1 K32. MOV A, C

К4. IN 2 K33. M6: MOV A, C

К5. MOV L, A K34. ORI A,FE

К6. MVI H, 0 JMP M4.

К7. M2: IN 3

К8. RRC

К9. JNC M2

К10. IN 4

К11. MOV B, A

К12. IN 5

К13. JS M3

К14. MOV M, B

К15. MVI H, 01

К16. MVI A, 0

К17. MOV M, A

JMP M1

К18. M3: MOV A, B

К19. SUB A, M

К20. MOV M, B

К21. MVI H, 01

К22. ADD A, M

К23. SUI A,32

К24. JS M5

К25. ADI A, 32

K26. M4: OUT 1

K27. MOV M, A

JMP M1

K28. M5: ADI A, 32

K29. MOV C, A

Рисунок 2.3.2 – Алгоритм работы ОКМ – 1.

Для более подробного изучения некоторых характеристик ОКМ предлагается выполнить несколько лабораторных работ.