- •Основи наукових досліджень

- •8.160102 "Захист інформації з обмеженим доступом та автоматизації її обробки"

- •8.160105 "Захист інформації в комп'ютерних системах та мережах"

- •Вимоги вак України

- •Организация высокопроизводительных систолических криптографических вычислителей

- •Модель формування нечітких еталонів для систем виявлення атак

- •Домашнє завдання №2.

- •Вимоги до оформлення.

- •Домашнє завдання №3.

- •Вимоги до оформлення.

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Національний авіаційний університет

Факультет телекомунікації та захисту інформації

Кафедра Безпеки інформаційних технологій

Основи наукових досліджень

Методичні вказівки до виконання домашніх робіт для студентів

Інституту інформаційно-діагностичних систем

спеціальностей

8.160102 "Захист інформації з обмеженим доступом та автоматизації її обробки"

та

8.160105 "Захист інформації в комп'ютерних системах та мережах"

Київ 2007

ДОМАШНЄ ЗАВДАННЯ №1.

Завданням до ДЗ №1 є написання наукової статті відповідно до вимог ВАК України.

Вимоги вак України

Приклад 1 написання наукової статті.

УДК 681.511.46

А.Г. Корченко, В.М. Котлярский, В.П. Щербина, Е.В. Пацира

Организация высокопроизводительных систолических криптографических вычислителей

В настоящее время для надежного обеспечения конфиденциальности информации применяются криптографические алгоритмы. Использование процессоров и микроконтроллеров, позволяющих защитить информацию посредством выполнения процедур шифрования, стало одним из наиболее эффективных средств борьбы с несанкционированным доступом. Вопросы реализации в реальном времени криптографических алгоритмов остаются по-прежнему актуальными.

Программное исполнение указанных алгоритмов не позволяет достичь высокой скорости шифрования. Поэтому средства защиты с такой реализацией не всегда можно использовать в системах реального времени, особенно в тех случаях, когда преобразуются значительные объемы данных. В большинстве криптосистем c секретным ключом (Кл), например, таких как DES или ГОСТ, реализуется типовая функция, которая n-кратное (в зависимости от системы) число раз осуществляет обработку исходного текста. Эту особенность можно использовать для повышения производительности цифровых устройств, реализующих криптографические преобразования. Для этого следует составить алгоритм, предусматривающий конвейер данных, и отобразить его на систолическую структуру, в которой очередной блок, исполняющий функцию шифрования, получает данные из предыдущего.

С целью минимизации задержек в разрабатываемых структурах вычислителей некоторые преобразования (перестановка, сдвиг, добавление или удаление битов) необходимо осуществлять путем соответствующих коммутаций сигнальных линий шин данных.

Средняя скорость шифрования одного блока данных в криптографических систолических вычислителях будет расти с увеличением объема обрабатываемой информации.

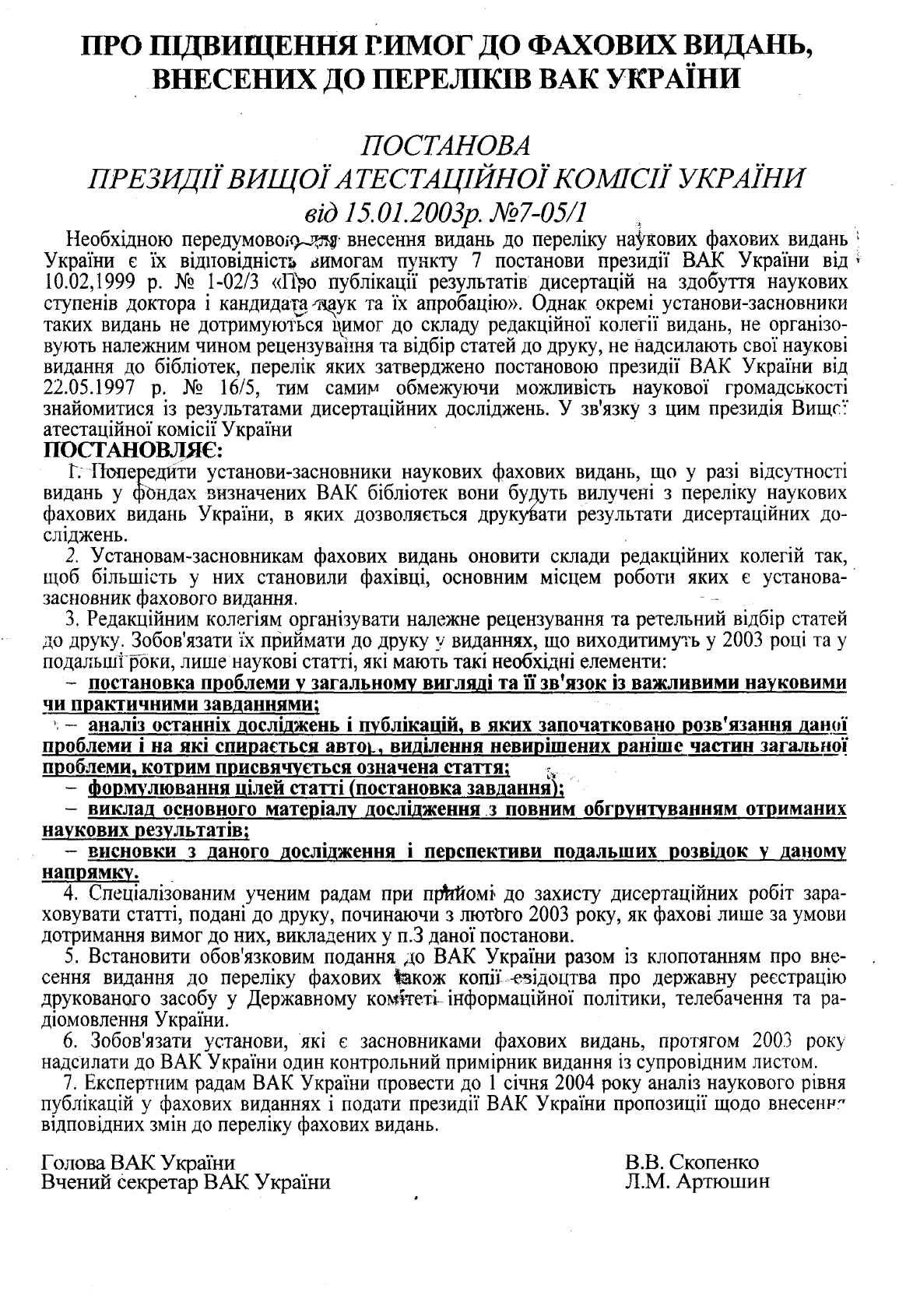

В качестве иллюстрации сказанного построим систолический криптографический вычислитель (КрВ), реализующий систему шифрования DES (рис.1).

Он

содержит модуль (М) начальной обработки

(МНО), 16 М шифрования (МШi,

![]() ),

М формирования результата (МФР), две

64-битовые шины входа (Швх1

и Швх2),

разряды которых представляют собой

массив, упорядоченный в соответствии

с исходной матрицей (ИМ) (рис. 2,а), 64-битную

шину выхода (Швых)

и 2-разрядную шину управления (ШУ), по

первому разряду которой поступает

стробирующий сигнал записи результата

i-й итерации (И) шифрования или дешифрования

(Ш/Д), второй - определяет режим работы

КрВ Ш/Д.

),

М формирования результата (МФР), две

64-битовые шины входа (Швх1

и Швх2),

разряды которых представляют собой

массив, упорядоченный в соответствии

с исходной матрицей (ИМ) (рис. 2,а), 64-битную

шину выхода (Швых)

и 2-разрядную шину управления (ШУ), по

первому разряду которой поступает

стробирующий сигнал записи результата

i-й итерации (И) шифрования или дешифрования

(Ш/Д), второй - определяет режим работы

КрВ Ш/Д.

Рис.1.

В МНО входят блок начальной подготовки Кл (БНПК), блок начальной перестановки данных (БНПД) и блок выбора режима (БВР).

Блоки

БНПК и БНПД содержат группу контактов

(ГК), коммутирующих разряды Швх1

и Швх2

соответственно на базе матрицы начальной

подготовки Кл (МНПК) (рис.2,б) и матрицы

начальной подготовки данных (МНПД)

(рис.2,в) относительно ИМ. Блок БВР

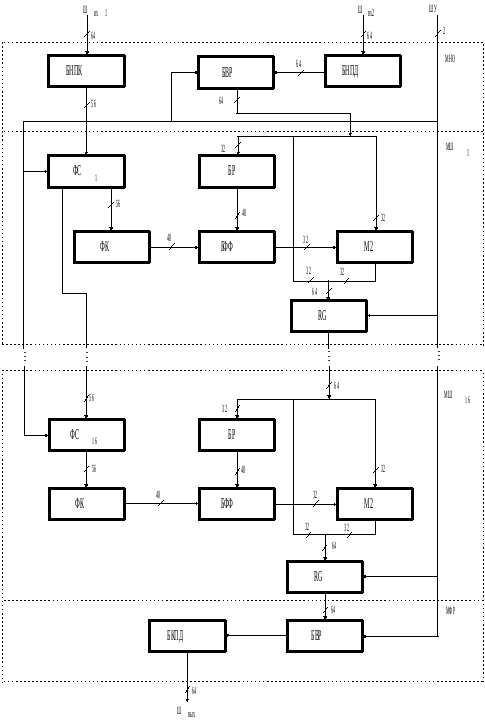

(рис.3,а) состоит из узла перестановок

(УП), содержащего ГК, коммутирующих выход

БНПД в соответствии с матрицей связей

(МС) (рис.4,а) и мультиплексора (MUX). На

выходе MUX в зависимости от режима работы

Ш/Д формируется либо значение, поступившее

на вход данного узла, либо преобразованное

с помощью УП. Циклы Ш/Д реализуются с

помощью 16 МШi

(![]() ),

состоящих из формирователей сдвигов

(ФС) (ФСi,

),

состоящих из формирователей сдвигов

(ФС) (ФСi,

![]() )

и формирователей Кл (ФК), блоков расширения

(БР) и формирования функции (БФФ), схем

совпадения (М2) и регистров (RG). Модули

МШi

(

)

и формирователей Кл (ФК), блоков расширения

(БР) и формирования функции (БФФ), схем

совпадения (М2) и регистров (RG). Модули

МШi

(![]() )

отличаются от ФСi

(

)

отличаются от ФСi

(![]() ),

которые в очередной И Ш/Д формируют

новое значение для ФК, генерирующего

Кл шифрования (Клi,

),

которые в очередной И Ш/Д формируют

новое значение для ФК, генерирующего

Кл шифрования (Клi,

![]() ).

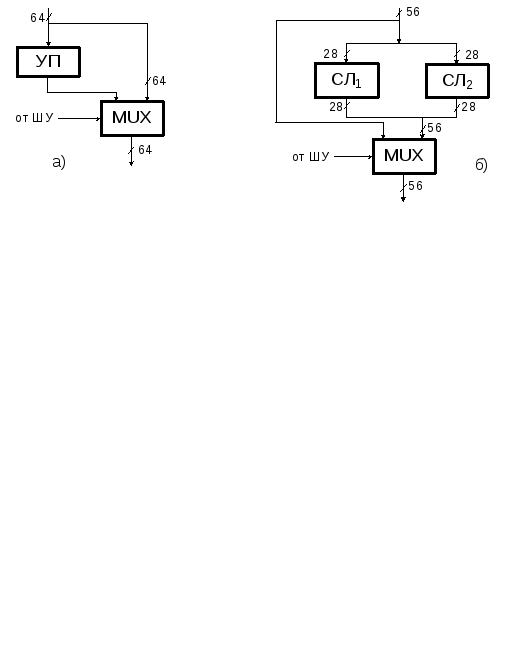

Организация сдвигов в ФС1

(рис.3,б), ФСi

(

).

Организация сдвигов в ФС1

(рис.3,б), ФСi

(![]() )

(рис.3,б), ФСi

(i=3,8,10,15) (рис.3,в), осуществляется с помощью

сдвигателей влево (СЛ) (СЛi,

i=1,2) или вправо (СП) (СПi,

i=1,2) на основе матриц сдвигов, показанных

на рис.4,б, рис.4,в, рис.4,г и 4,д соответственно.

Мультиплексоры формирователей ФСi

(

)

(рис.3,б), ФСi

(i=3,8,10,15) (рис.3,в), осуществляется с помощью

сдвигателей влево (СЛ) (СЛi,

i=1,2) или вправо (СП) (СПi,

i=1,2) на основе матриц сдвигов, показанных

на рис.4,б, рис.4,в, рис.4,г и 4,д соответственно.

Мультиплексоры формирователей ФСi

(![]() )

предназначены для коммутации 56-битового

кода, образуемого СПi

(i=1,2)

и СЛi

(i=1,2).

Формирователь ФК содержит ГК, коммутирующих

выходы БФФ в соответствии с матрицей

завершающей обработки Кл (МЗОК) (рис.4,е),

а БР включает ГК, коммутирующих выходы

БВР в соответствии с матрицей распределения

(МР) (рис.2,г). Блок БФФ (рис.3,д) состоит из

М2, постоянного запоминающего устройства

(ПЗУ), хранящего матрицу преобразования

(МП), узла формирования (УФ), содержащего

ГК, коммутирующих выходы ПЗУ в соответствии

с матрицей перестановок (рис.2,д). В RG

хранятся результаты Ш/Д, получаемые на

каждой И в МШi

(

)

предназначены для коммутации 56-битового

кода, образуемого СПi

(i=1,2)

и СЛi

(i=1,2).

Формирователь ФК содержит ГК, коммутирующих

выходы БФФ в соответствии с матрицей

завершающей обработки Кл (МЗОК) (рис.4,е),

а БР включает ГК, коммутирующих выходы

БВР в соответствии с матрицей распределения

(МР) (рис.2,г). Блок БФФ (рис.3,д) состоит из

М2, постоянного запоминающего устройства

(ПЗУ), хранящего матрицу преобразования

(МП), узла формирования (УФ), содержащего

ГК, коммутирующих выходы ПЗУ в соответствии

с матрицей перестановок (рис.2,д). В RG

хранятся результаты Ш/Д, получаемые на

каждой И в МШi

(![]() ).

С помощью RG в структуре КрВ формируется

конвейер данных, благодаря которому

эффективно реализуется функция

шифрования. В модуль МФР включены БВР

и блок конечной перестановки данных

(БКПД), содержащий ГК, коммутирующих

выходы БВР в соответствии с матрицей

завершающей обработки данных (МЗОД)

(рис.2,е).

).

С помощью RG в структуре КрВ формируется

конвейер данных, благодаря которому

эффективно реализуется функция

шифрования. В модуль МФР включены БВР

и блок конечной перестановки данных

(БКПД), содержащий ГК, коммутирующих

выходы БВР в соответствии с матрицей

завершающей обработки данных (МЗОД)

(рис.2,е).

Полученная

систолическая структура КрВ функционирует

следующим образом. Содержащий 64 бита

Кл через Швх1

поступает в БНПК, где удаляются контрольные

разряды (8,16,24,32,40,48,56,64) ИМ. Полученное

56-битовое значение поступает в МШ1.

Подвергаемый Ш/Д исходный текст в виде

64-битовых блоков данных (БД) через Швх2

поступает параллельным кодом в БНПД.

Преобразованное в БНПД 64-битовое слово

поступает в БВР и передается на выходы

его MUX, управляемого сигналом Ш/Д,

поступающим с ШУ. Подготовленные к Ш/Д

64-битовые БД поступают потактно в МШi

(![]() ),

в которых указанные данные разделяются

на два БД: БД1

и БД2

по 32 бита каждый.

),

в которых указанные данные разделяются

на два БД: БД1

и БД2

по 32 бита каждый.

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

57 |

49 |

41 |

33 |

25 |

17 |

09 |

|

||

|

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

01 |

58 |

50 |

42 |

34 |

26 |

18 |

|

||

|

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

10 |

02 |

59 |

51 |

43 |

35 |

27 |

|

||

|

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

|

19 |

11 |

03 |

60 |

52 |

44 |

36 |

|

||

|

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

|

63 |

55 |

47 |

39 |

31 |

23 |

15 |

|

||

|

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

|

07 |

62 |

54 |

46 |

38 |

30 |

22 |

|

||

|

49 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

|

14 |

06 |

61 |

53 |

45 |

37 |

29 |

|

||

|

57 |

58 |

59 |

60 |

61 |

62 |

63 |

64 |

|

21 |

13 |

05 |

28 |

20 |

12 |

04 |

|

||

|

а) |

|

б) |

||||||||||||||||

|

58 |

50 |

42 |

34 |

26 |

18 |

10 |

02 |

|

32 |

01 |

02 |

03 |

04 |

05 |

||

|

60 |

52 |

44 |

36 |

28 |

20 |

12 |

04 |

|

04 |

05 |

06 |

07 |

08 |

09 |

||

|

62 |

54 |

46 |

38 |

30 |

22 |

14 |

06 |

|

08 |

09 |

10 |

11 |

12 |

13 |

||

|

64 |

56 |

48 |

40 |

32 |

24 |

16 |

08 |

|

12 |

13 |

14 |

15 |

16 |

17 |

||

|

57 |

49 |

41 |

33 |

25 |

17 |

09 |

01 |

|

16 |

17 |

18 |

19 |

20 |

21 |

||

|

59 |

51 |

43 |

35 |

27 |

19 |

11 |

03 |

|

20 |

21 |

22 |

23 |

24 |

25 |

||

|

61 |

53 |

45 |

37 |

29 |

21 |

13 |

05 |

|

24 |

25 |

26 |

27 |

28 |

29 |

||

|

63 |

55 |

47 |

39 |

31 |

23 |

15 |

07 |

|

28 |

29 |

30 |

31 |

32 |

01 |

||

|

в) |

|

г) |

||||||||||||||

|

16 |

07 |

20 |

21 |

|

|

|

40 |

08 |

48 |

16 |

56 |

24 |

64 |

32 |

|

||

|

29 |

12 |

28 |

17 |

|

|

|

39 |

07 |

47 |

15 |

55 |

23 |

63 |

31 |

|

||

|

01 |

15 |

23 |

26 |

|

|

|

38 |

06 |

46 |

14 |

54 |

22 |

62 |

30 |

|

||

|

05 |

18 |

31 |

10 |

|

|

|

37 |

05 |

45 |

13 |

53 |

21 |

61 |

29 |

|

||

|

02 |

08 |

24 |

14 |

|

|

|

36 |

04 |

44 |

12 |

52 |

20 |

60 |

28 |

|

||

|

32 |

27 |

03 |

09 |

|

|

|

35 |

03 |

43 |

11 |

51 |

19 |

59 |

27 |

|

||

|

19 |

13 |

30 |

06 |

|

|

|

34 |

02 |

42 |

10 |

50 |

18 |

58 |

26 |

|

||

|

22 |

11 |

04 |

25 |

|

|

|

33 |

01 |

41 |

09 |

49 |

17 |

57 |

25 |

|

||

|

д) |

|

е) |

|||||||||||||||

Рис. 2

Младшие разряды, содержащиеся в БД1, поступают на вход M2, а старшие, содержащиеся в БД2, - на БР. Разряды БД1, поступившие в блок БР, расширяются до 48 бит, образуя новый код.

Сформированное

в БНПК 56-битовое значение начального

Кл поступает в ФCi

(![]() ),

где разбивается на старшую и младшую

части по 28 бит каждая, обрабатываемые

сдвигателями (рис.3,б, рис.3,в и 3,г

соответственно), выходы которых подключены

к MUX. Сформированное 56-битовое слово на

выходах MUX ФСi

МШi

(

),

где разбивается на старшую и младшую

части по 28 бит каждая, обрабатываемые

сдвигателями (рис.3,б, рис.3,в и 3,г

соответственно), выходы которых подключены

к MUX. Сформированное 56-битовое слово на

выходах MUX ФСi

МШi

(![]() )

поступает в ФСi+1

МШi+1

(

)

поступает в ФСi+1

МШi+1

(![]() )

и ФК МШi

(

)

и ФК МШi

(![]() ).

).

Приходящий

в ФК 56-битовый БД преобразуется в

48-битовый, представляющий собой значение

Клi

(![]() )

для i-й И Ш/Д. Ключ, содержащий 48 разрядов,

Клi

(

)

для i-й И Ш/Д. Ключ, содержащий 48 разрядов,

Клi

(![]() )

и 48-битовые данные, сформированные БР,

передаются в БФФ (рис.3,д), преобразуются

на М2 БФФ и поступают на адресные входы

ПЗУ БФФ, с которого считывается БД,

передаваемый в УФ БФФ.

)

и 48-битовые данные, сформированные БР,

передаются в БФФ (рис.3,д), преобразуются

на М2 БФФ и поступают на адресные входы

ПЗУ БФФ, с которого считывается БД,

передаваемый в УФ БФФ.

Рис. 3

С

УФ БФФ 32-разрядный код поступает на

первый вход М2 МШi

(![]() ),

на второй вход которого передаются

младшие 32 бита БД, образующиеся на выходе

БВР МНО для первой И Ш/Д или RG МШi

(

),

на второй вход которого передаются

младшие 32 бита БД, образующиеся на выходе

БВР МНО для первой И Ш/Д или RG МШi

(![]() )

для i-й операции Ш/Д (

)

для i-й операции Ш/Д (![]() ).

Результирующие 32 бита объединяются со

старшими 32 битами БД БВР МНО для первой

И Ш/Д или RG МШi

(

).

Результирующие 32 бита объединяются со

старшими 32 битами БД БВР МНО для первой

И Ш/Д или RG МШi

(![]() )

- для i-й операции Ш/Д (

)

- для i-й операции Ш/Д (![]() ).

Образованный при этом 64-битовый код

записывается в RG по стробирующему

сигналу, поступающему из ШУ.

).

Образованный при этом 64-битовый код

записывается в RG по стробирующему

сигналу, поступающему из ШУ.

|

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

|

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

||

|

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

|

10 |

11 |

12 |

13 |

14 |

15 |

16 |

23 |

||

|

49 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

|

17 |

18 |

19 |

20 |

21 |

22 |

24 |

25 |

||

|

57 |

58 |

59 |

60 |

61 |

62 |

63 |

64 |

|

26 |

27 |

28 |

1 |

|

|

|

|

||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

|

|

|

б) |

|

|

|

|

||

|

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

||

|

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

||

|

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

|

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

||

|

|

|

|

|

|

|

|

|

|

27 |

28 |

1 |

2 |

|

|

|

|

||

|

а) |

|

в) |

|

|

||||||||||||||

|

28 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

14 |

17 |

11 |

24 |

01 |

05 |

|

|

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

|

03 |

28 |

15 |

06 |

21 |

10 |

|

|

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

|

23 |

19 |

12 |

04 |

26 |

08 |

|

|

24 |

25 |

26 |

27 |

28 |

20 |

30 |

31 |

|

16 |

07 |

27 |

20 |

13 |

02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

г) |

|

|

|

|

|

41 |

52 |

31 |

37 |

47 |

55 |

|

|

27 |

28 |

1 |

2 |

3 |

4 |

5 |

6 |

|

30 |

40 |

51 |

45 |

33 |

48 |

|

|

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

|

44 |

49 |

39 |

56 |

34 |

53 |

|

|

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

|

46 |

42 |

50 |

36 |

29 |

32 |

|

|

23 |

24 |

25 |

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

д) |

|

е) |

|||||||||||||

Рис.4

Результат,

хранящийся в RG МШi

(![]() ),

представляет собой зашифрованное или

расшифрованное сообщение для i-й И

(одного цикла Ш/Д). С помощью МШi

(

),

представляет собой зашифрованное или

расшифрованное сообщение для i-й И

(одного цикла Ш/Д). С помощью МШi

(![]() )

в КрВ реализован 16-ступенчатый конвейер

Ш/Д данных. Полученное в RG МШi

(i=16) 64-битовый БД передается в МФР, где

обрабатывается в БВР и БКПД.

Сформированное 64-битовое сообщение

поступает на 64-разрядную шину выходов

(Швых).

)

в КрВ реализован 16-ступенчатый конвейер

Ш/Д данных. Полученное в RG МШi

(i=16) 64-битовый БД передается в МФР, где

обрабатывается в БВР и БКПД.

Сформированное 64-битовое сообщение

поступает на 64-разрядную шину выходов

(Швых).

При разработке принципиальной схемы КрВ применены микросхемы КР556РТ11, КР531ЛП5, КР1531КП16 и КР1531ИР23, при этом время Ш/Д для одной И составляет 86 нс. При конвейерной обработке среднее время Ш/Д одного блока определим по формуле :

Тср=(n T + 2Tmux + (N-1)T) / N,

где n - число ступеней конвейера; T - время шифрования для одной И; Tmux - время переключения MUX; N - число блоков Ш/Д данных.

Например, для сообщения размером 1024 бита Tср составило 0,168 мкс, при этом производительность КрВ соответствует 45,4 Мбайт/с. Для Ш/Д БД большей длины, например N, Тср будет стремиться к T. В этом случае предельная производительность Ш/Д для данного типа КрВ приближается к 88,7 Mбайт/с.

Таким образом, данное быстродействие достигается за счет использования систолической организации вычислителя для реализации криптографического алгоритма.

Приклад 2 написання наукової статті.

УДК 004.56.021.2: 510.22 (045)

Бабак В. П., Корченко О. Г., Пацира Є. В., Потапов В.Г.