- •Введение

- •Расшифровка и анализ задания

- •2.2 Система команд бис к1810вм86

- •2.3 Генератор тактовых импульсов

- •2.4 Буферные регистры

- •2.5 Шинные формирователи

- •2.6 Контроллер шин к1810вг88

- •2.7 Арбитр шин к1810вб89

- •2.8.2 Формирование магистралей адреса, данных и управления

- •4.3 Разработка контроллера прямого доступа к памяти

- •16К/64к – вход выбора режима. Сигнал высокого уровня на этом входе задает режим работы кдп с озу емкостью 16к слов, а сигнал низкого уровня – режим работы с озу емкостью 64к.

- •6 Организация управления мпс

- •6.1 Сопряжение с клавиатурой

- •6.2 Сопряжение с дисплеем

- •7 Построение мпс

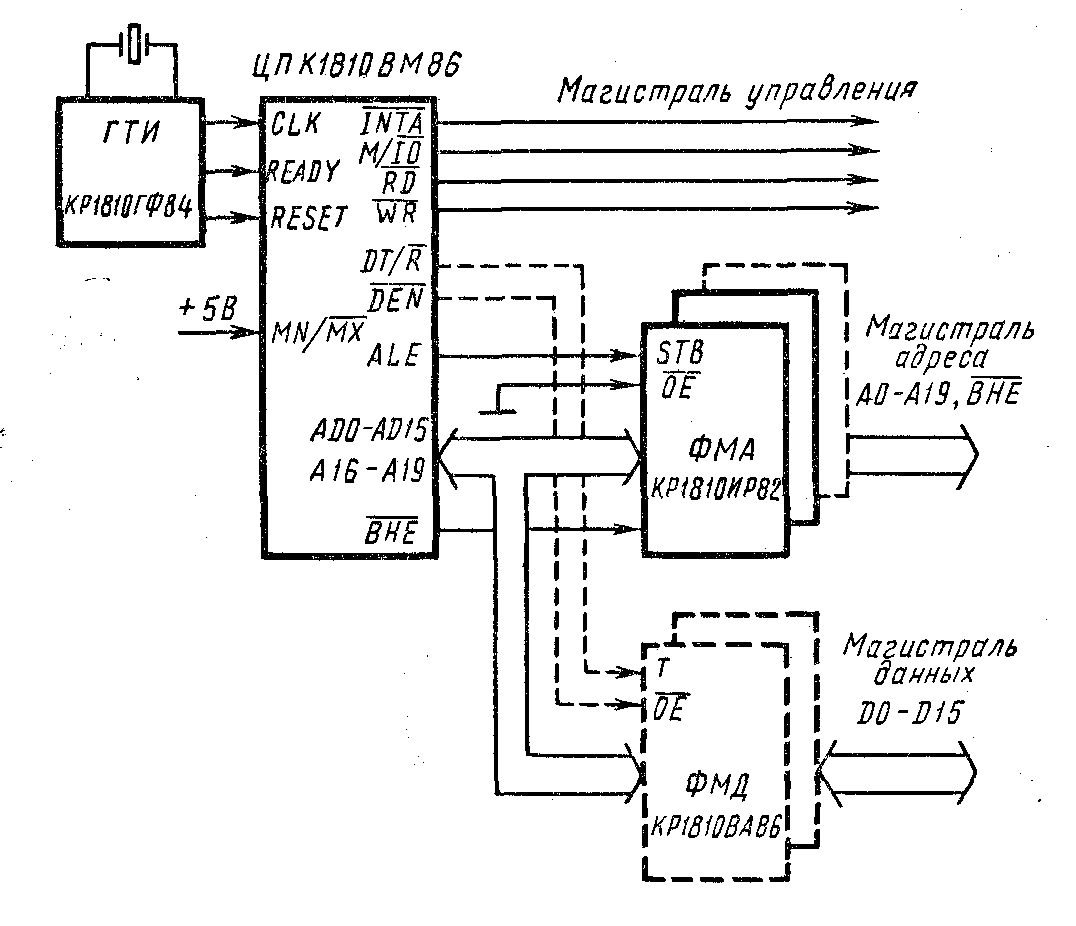

2.8.2 Формирование магистралей адреса, данных и управления

микроЭВМ.

Схемы формирования магистралей адреса, данных и управления различны при включении МП К1810ВМ86 в минимальном или максимальном режиме.

Рисунок 18 - Формирование магистралей адреса и данных при работе

БИС ЦП К1810ВМ86 в минимальном режиме

В минимальном режиме

магистраль управления образуется

сигналами:

![]() — обращение к памяти или к УВВ,

— обращение к памяти или к УВВ,

![]() - строб чтения данных,

- строб чтения данных,

![]() — строб записи данных,

— строб записи данных,

![]() — строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

— строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

![]() и разрешения обмена данными —

и разрешения обмена данными —

![]() (рисунок 18).

(рисунок 18).

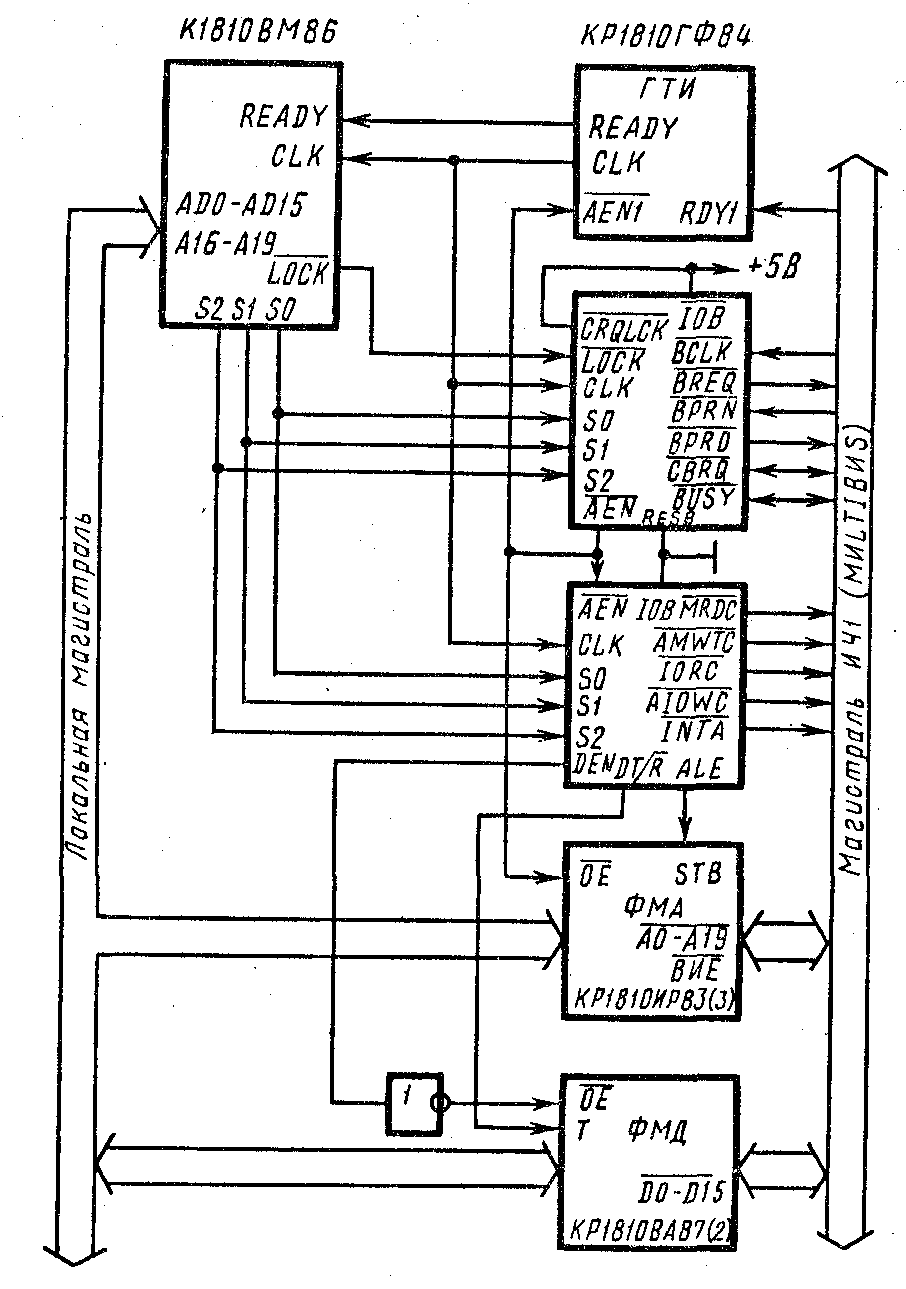

В максимальном режиме для формирования управляющих сигналов применяют системный контроллер КР1810ВГ88, обрабатывающий сигналы SO, SI, S2 состояния МП.

МП К1810ВМ86 можно подключать к общей многопроцессорной магистрали ИЧ1 (MULTIBUS); при этом для арбитража доступа МП БИС к магистрали необходимо использовать арбитр магистрали БИС К1810ВБ89 (рисунок 19).

Рисунок 19 - Подключение МП БИС К1810ВМ86 в максимальном

режиме к мультиплексорной магистрали ИЧ1 (MULTIBUS)

При необходимости захвата

магистрали процессором арбитр вырабатывает

сигналы запроса захвата магистрали

![]() и всеобщего запроса

и всеобщего запроса

![]() .

Если магистраль свободна (

.

Если магистраль свободна (![]() равно 1) и есть разрешение

равно 1) и есть разрешение

![]() с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

![]() и по сигналу

и по сигналу

![]() информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

![]() ,

MWTC,

,

MWTC,

![]() ,

IOWC.

,

IOWC.

Сигнал

![]() используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

![]() (в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

(в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

![]() для дальнейшей обработки.

для дальнейшей обработки.

Для монопольного захвата

магистрали на время выполнения одной

команды (с префиксом

![]() )

процессор может вырабатывать сигнал

)

процессор может вырабатывать сигнал

![]() .

.

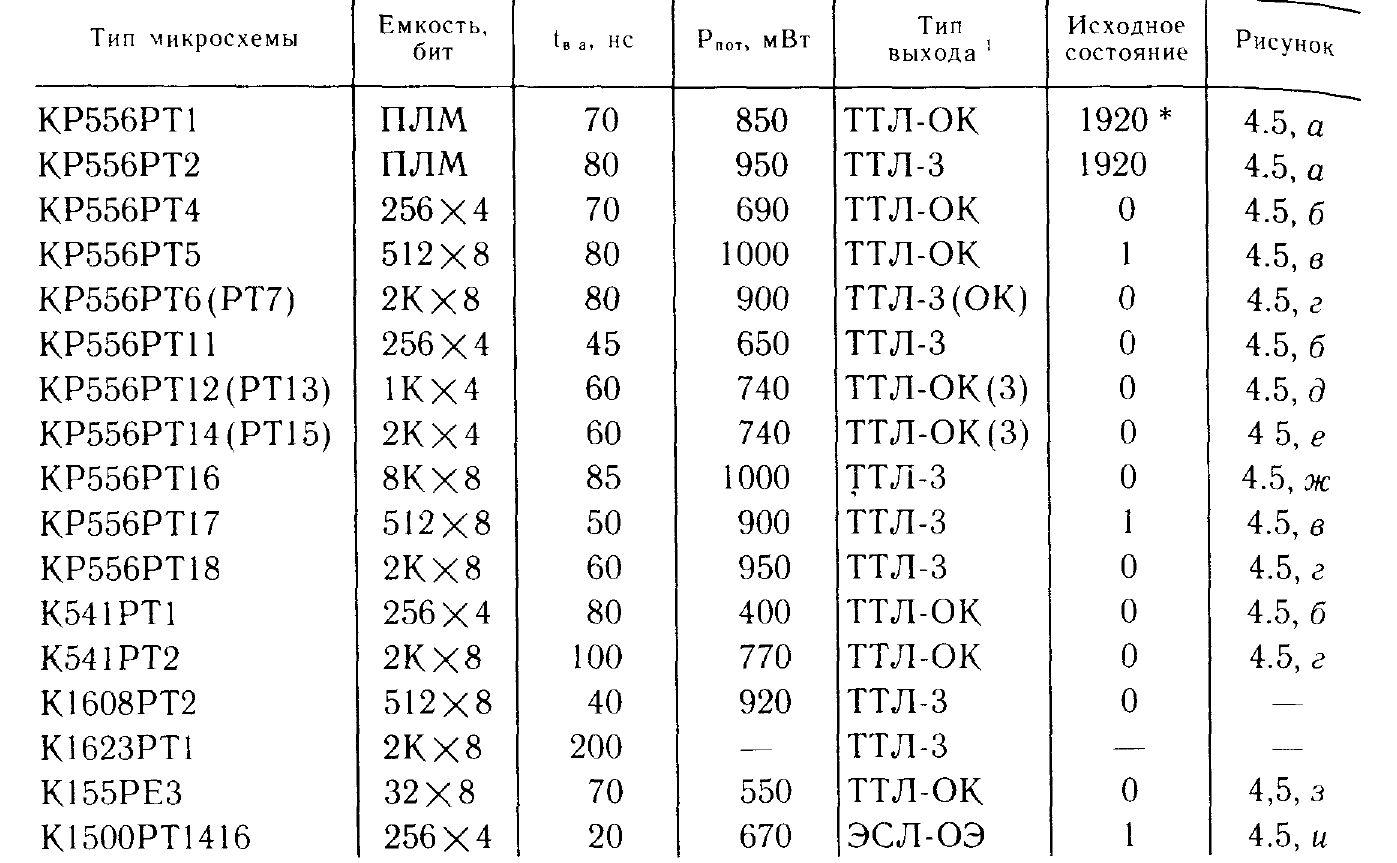

3 Разработка систем памяти

-

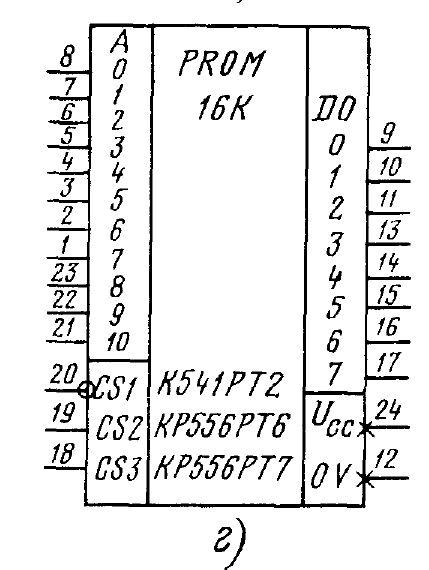

БИС ПЗУ К556РТ6

Микросхемы программируемых ПЗУ по принципу построения и функционирования аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают программирование на месте своего применения пользователем. Операция программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и доступностью микросхем ППЗУ обусловило их широкое распространение в радиолюбительской практике.

Выпускаемые отечественной промышленностью микросхемы ППЗУ в большинстве своем изготовлены по ТТЛ-технологии, и среди них преобладающее положение занимает серия К556. Функциональный состав серии включает микросхемы емкостью до 64К бит со словарной 4- и 8-разрядной организацией с временем выборки 45 ... 85 не и уровнем потребляемой мощности от 0,6 до 1 Вт.

Для микросхем ППЗУ всех серий, кроме К500, К1500, К565, Характерны такие свойства, как единое напряжение питания 5 В, Наличие входных и выходных ТТЛ-уровней напряжения логического 0 (0,4 В) и логической 1 (2,4 В) и, следовательно, полная совместимость микросхем, однотипные выходы: либо с тремя состояниями, либо с открытым коллектором. Микросхемы с выходами ТТЛ требуют подключения к ним внешних резисторов и источника напряжения питания.

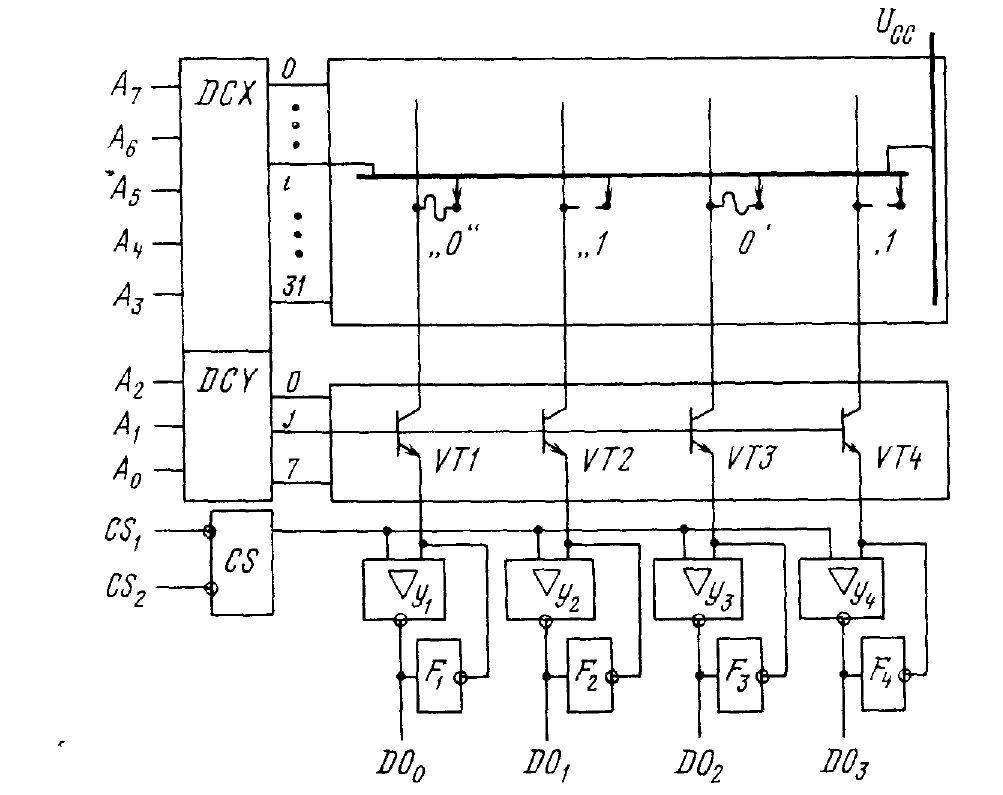

Типичный вариант реализации микросхемы ППЗУ представлен на рис. 4.5. Для конкретности рассмотрения взята структура микросхемы К556РТ4. Во всех основных элементах она повторяет структуру ПЗУМ (см. рис. 4.1), но имеет дополнительные устройства F1—F4 для формирования тока программирования

Таблица - 5 Микросхемы ППЗУ

Матрица до программирования, т. е. в исходном состоянии, содержит однородный массив проводящих перемычек, соединяющих строки и столбцы во всех точках их пересечений. Перемычки устанавливают из нихрома (у микросхем серии К556 и др.), из поликристаллического кремния (К541), из силицида платины (К1608) и других материалов. Перемычка в матрице выполняет роль ЭП. Наличие перемычки кодируют логической 1, если усилитель считывания является повторителем, и логическим О, если усилитель считывания — инвертор, как на рис. 4.4. Следовательно, микросхема ППЗУ в исходном состоянии перед программированием в зависимости от характеристики выходного усилителя может иметь заполнение матрицы либо логическим О, либо логической 1. Информация о принадлежности микросхем ППЗУ к той или другой группе по данному признаку при ведена в табл. 4.2. Если такой информации нет, ее необходимо получить с помощью начального контроля микросхемы: устанавливая разрешающие значения управляющих сигналов (в схеме на рис. 4.4 CS1 = CS2 = 0), следует перебрать адреса, контролируя при этом состояние выходов.

Программирование микросхемы, матрица которой в исходном состоянии заполнена 0, заключается в пережигании перемычек в тех ЭП, где должны храниться 1. Если матрица в исходном состоянии заполнена 1, то пережигают перемычки в ЭП, где должны храниться 0.

Рисунок - 7 Микросхем ПЗУ К556РТ6

.

Рисунок - 8 Устройство микросхемы ППЗУ

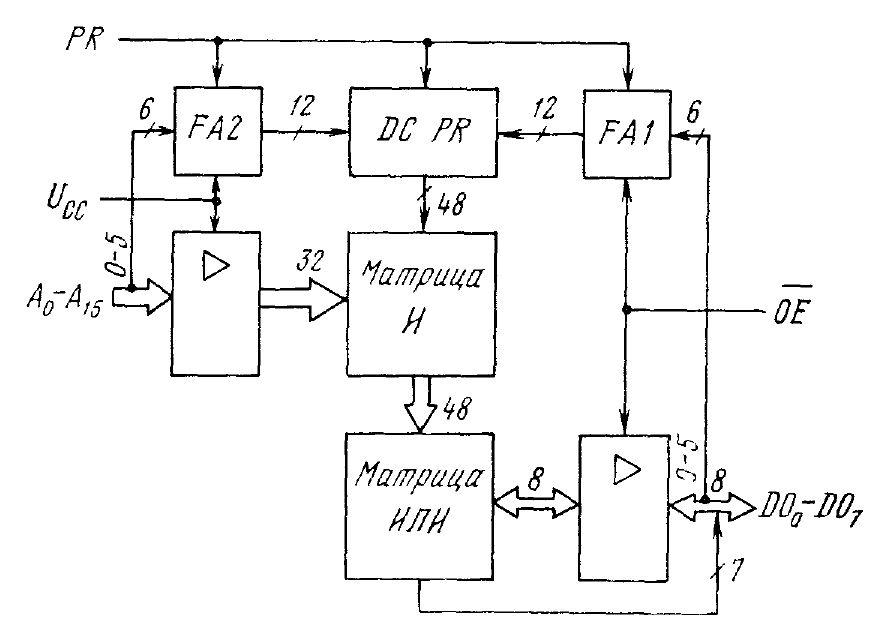

Рисунок - 9 Структура микросхемы К556РТ6

Структура микросхемы включает операционную часть из матрицы И, матрицы ИЛИ, входных и выходных усилителей и программирующую часть из адресных формирователей FA1, FA2 и дешифратора DCPR.

Основу ПЛМ составляют матрицы И и ИЛИ. Матрица И выполняет операции конъюнкции над 16 входными переменными и их инверсными значениями, которые поступают на строчные шины матрицы. Требуемые логические произведения формируют на шинах столбцов путем выжигания ненужных перемычек между строками и столбцами. Число столбцов 48, следовательно, на выходе матрицы И можно получить до 48 логических произведений, в каждое из которых может входить до 16 переменных и их инверсий. Матрица ИЛИ выполняет операцию дизъюнкции над логическими произведениями, сформированными матрицей И. Число выходов этой матрицы 8, поэтому она способна сформировать до восьми логических сумм, в каждую из которых может входить до 48 логических произведений. Таким образом, возможности ПЛМ характеризуются числом .точек коммутации, равным в данном примере 1920. Программирование матрицы ИЛИ выполняется так же, как и матрицы И, путем выжигания «ненужных» перемычек. На выходах матрицы ИЛИ размещены программируемые усилители, которые в зависимости от состояния перемычки могут передавать значение выходной функции в прямой или инверсной форме представления.

Рисунок - 10 Функциональная схема ПЛМ

Для программирования служат встроенные в микросхему узлы программирующей части, которые возбуждает разрешающий сигнал PR. Программирование осуществляют способом, аналогичным программированию ППЗУ, в три этапа: вначале программируют матрицу И, затем матрицу ИЛИ и выходные инверторы .

При использовании импульсного режима питания среднее значение потребляемого тока и, следовательно, уровень потребляемой мощности существенно уменьшаются.

4 РАЗРАБОТКА ПОДСИСТЕМ ВВОДА/ВЫВОДА, ПРЕРЫВАНИЙ, ПДП

4.1 Программируемый параллельный интерфейс подсистемы ввода/

вывода КР580ВВ55

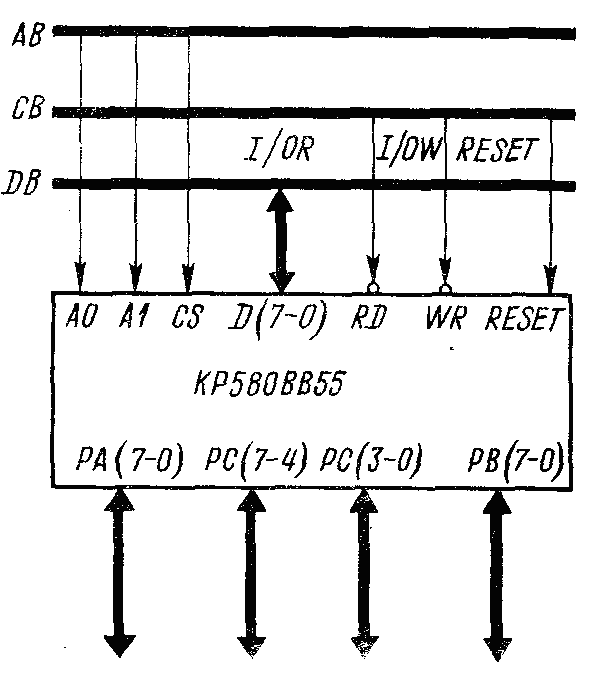

Ммкропроцессорная БИС программируемого параллельного интерфейса КР58ОВВ55 предназначена для организации ввода/вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

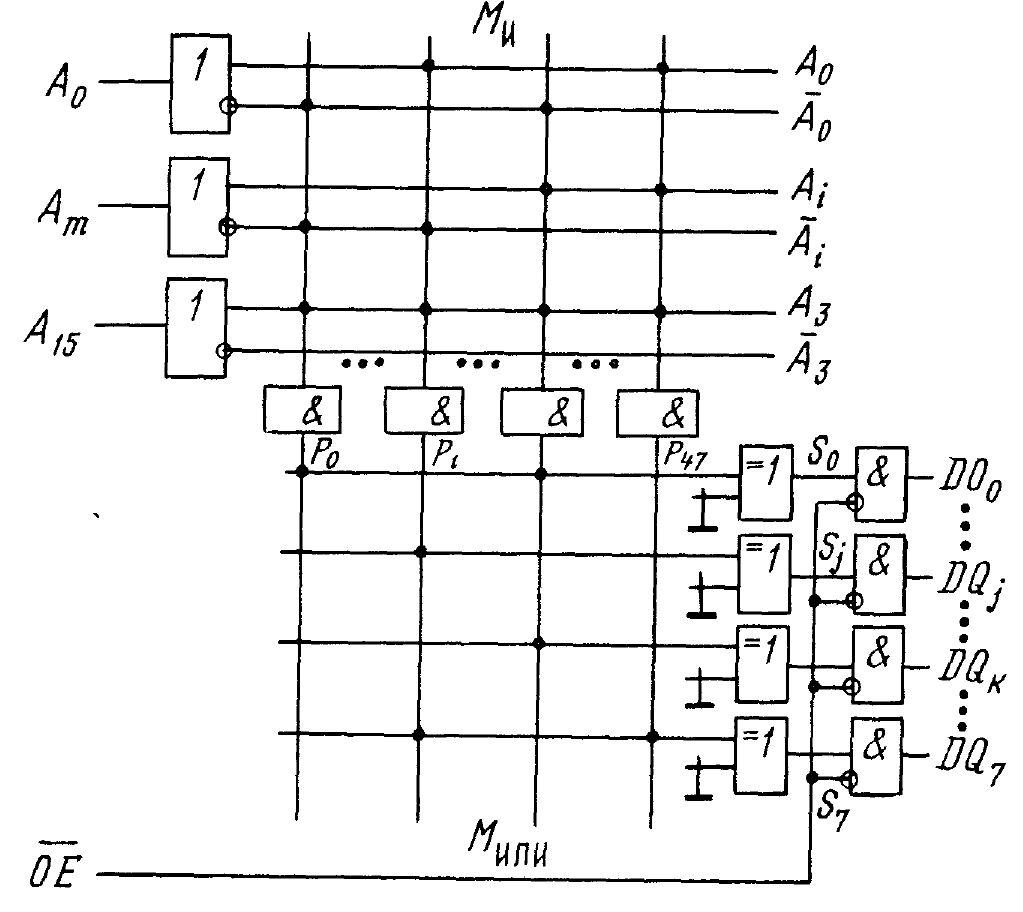

Структурная схема ППИ приведена на рисунке 9.

Рисунок 9 — Структурная схема программируемого параллельного интер-

фейса КР580ВВ55

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С[РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С[РС(3-0)].

Таблица 9 — Описание выводов программируемого параллельного интер-

фейса КР580ВВ55.

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

D(7-0) |

27; 28; 29; 30; 31; 32; 33; 34 |

Вход/выход данных |

|

RD |

5 |

Чтение; L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D(7-0) |

|

WR |

36 |

Запись; L-уровень сигнала разрешает запись информации с шипы D(7—0) в регистр ППИ, адресуемый по входам А0, А1 |

|

АО, А1 |

9; 8 |

Входы для адресации внутренних регистров ППИ |

|

RESET |

35 |

Сброс; H-уровень сигнала обнуляет регистр управляющего слова и уста-навливает все порты в режим ввода |

|

CS |

6 |

Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине |

|

РА(7-0) |

37; 38; 39; 40; 1; 2; 3; 4 |

Вход/выход канала А |

|

РВ(7-0) |

15; 24; 23; 22; 21; 20;19; 18 |

Вход/выход канала В |

|

РС(7-0) |

10; 11; 12; 13; 17; 16; 15; 14 |

Вход/выход канала С |

|

Ucc |

26 |

Напряжение питания ( + 5 В) |

|

GND |

7 |

Напряжение питания (0 В) |

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 9. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 10. Сигналы управления работой ППИ подаются на блок К\УС11 и вместе с адресными входами АО, А1 задают вид операции, выполняемой БИС.

Рисунок 10 — Схема сопряжения программируемого параллельного ин-

терфейса КР580ВВ55 со стандартной системной шиной

Основные электрические параметры микросхемы КР580ВВ55 следующие:

Выходное напряжение логического нуля UOL, В 0,4.

Выходное напряжение логической единицы UOH, В 2,4.

Ток потребления от источника питания ICC, мА 60.

Ток утечки каналов А, В, С, D

при невыбранном режиме IIOZ, мкА 100,...,100;

Ток утечки на управляющих входах IIL, мкА —10,...,10.

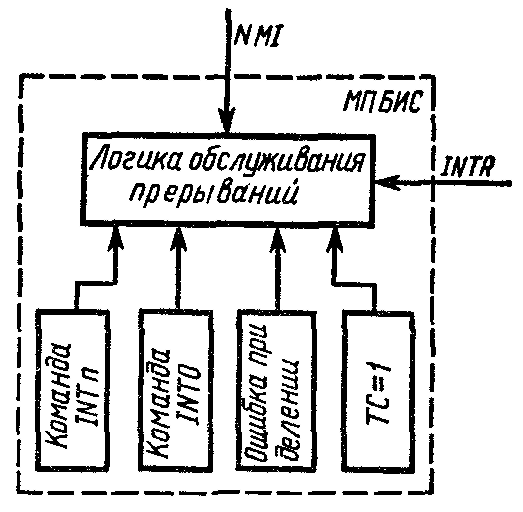

4.2 Подсистема прерываний

Микропроцессорная БИС имеет простую и изменяющуюся систему прерываний. Прерывания могут быть вызваны внешними устройствами, выполнением соответствующих команд, а также инициированы самой МП БИС (внутренние прерывания). Существует 256 различных типов прерываний.

Для подачи прерываний в МП БИС имеются два входа:

INTR – Interrupt Reguest и NMI – Non Masking Interrupt (рисунок 24).

Рисунок 11 – Возможные способы формирования прерываний в МП

К1810ВМ6

Вход INT обычно используется для подключения программируемого блока приоритетных прерываний (БПП). По функциональному назначению микросхема БПП аналогична схеме КР580ИК59 и является дальнейшей ее модификацией. Режимы работы БПП могут быть заданы программно. Основные задачи БПП – получение запросов прерывания от различных внешних устройств, определение сигнала с высшим приоритетом, формирование запроса прерывания на входе МП БИС и сообщение номера текущего обслуживаемого внешнего устройства. Прерывания по входу INT могут быть маскированы путем записи «0» или «1» в разряд 1 флагового регистра МП БИС.

Микропроцессорная БИС реагирует на поступление запроса прерывания по входу INTR последовательным выполнением двух машинных циклов обслуживания прерывания: первый указывает БПП, что запрос прерывания был воспринят, и начинает обслуживаться; на втором БПП выдает на МД байт данных, указывающий тип прерывания (0–255). При работе МП БИС с максимальной конфигурацией системы на интервале двух циклов INTA на выходе LOCK формируется сигнал, запрещающий другим процессорам системы пользоваться магистралями.

Внешние устройства могут подавать запросы прерывания на второй вход NMI МП БИС. На этом входе запрос воспринимается и записывается в МП БИС по фронту поступающего импульса, не может быть маскирован и имеет высший приоритет по отношению к запросам, поступающим на вход INTR. Обычно вход NMI используют для указания МП БИС о каких-либо сбоях в системе (сбоях в источнике питания, ошибках в памяти). При определении наличия сигнала на входе NMl МП БИС нет необходимости получать код для инициализации процесса обслуживания прерывания и соответственно она не формирует два машинных цикла INTA в ответ на запрос по входу NMI.

Внутренние прерывания формируются за счет выполнения МП БИС команды прерывания (тип команды зависит от источника прерывания).

При установке флага переполнения О=1 в результате выполнения какой-либо команды программы формируется команда прерывания – INTO (прерывание по переполнению).

Микропроцессорная БИС формирует прерывание сразу же после выполнения команд DIV или IDIV, если частное от деления больше, чем разрядность используемых регистров.

При установке флага Т=1 МП БИС автоматически формирует прерывание, которое воздействует сразу после выполнения любой текущей команды. Этот тип прерывания называют одношаговым или первым типом, и он является мощным средством при отладке программ. При выполнении одношагового типа прерывания МП БИС производит обычную последовательность операций, а именно записывает в стек флаги МП БИС, содержимое регистров CS и IP. В дополнение к этому очищаются флаги I и Т. В регистры CS и IP записываются соответственно из адресов 00006, 00007 и 00004, 00005 новые значения базового адреса сегмента и смещения для передачи управления на соответствующую подпрограмму обслуживания прерывания. В качестве такой подпрограммы может быть использована подпрограмма выдачи результата выполнения программы на печать, дисплей и т. д. По окончании выполнения подпрограммы после получения команды IRET (возврат из подпрограммы) из стека извлекаются и записываются в МП БИС флаги и содержимое регистров IP и СР. Из приведенных пояснений ясно, что при выполнении одношагового типа прерывания МП БИС обслуживает прерывания обычным способом. Однако обеспечение вывода результатов выполнения отдельных блоков в программе или даже отдельных команд с целью их последующего анализа путем задания в нужном месте программ режима одношаговых прерываний является удобным средством при исследовании работы программ.

Типы внутренних прерываний имеют ряд общих свойств:

1) код прерывания сообщается МП БИС перед командой или включен в команду прерывания;

2) на выходе МП БИС не формируются сигналы INTA;

3) за исключением одношагового типа, внутренние прерывания не могут быть программно отключены;

4) за исключением одношагового типа, любой из внутренних прерываний имеет более высокий приоритет по отношению к внешним прерываниям.

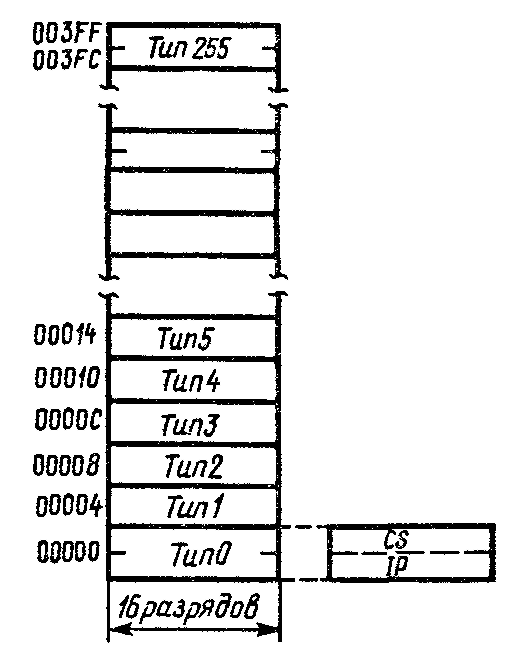

Любой из 256 возможных типов прерывания характеризуется вектором прерывания. Векторы прерывания занимают 1К байт адресного пространства. На рисунке 25 показано распределение начал векторов прерывания по адресам памяти. Как видно из рисунка, каждый вектор занимает четыре ячейки памяти, при этом два младших адреса в векторе используются для записи смещения в сегменте, а два старших — для записи базового адреса сегмента.

Рисунок 12 – Распределение векторов прерываний в памяти микроЭВМ

Формирование адреса передачи управления на соответствующую подпрограмму обслуживания прерывания в BIU происходит так же, как и при обращении к любой ячейке памяти, а именно: содержимое двух младших адресов вектора прерывания записывается в регистр IP, coдержимое старших двух адресов записывается в регистр CS. После этого содержимое CS смещается на четыре разряда влево и откладывается с содержимым IP. Полученное 20-разрядное число определяет адрес начала подпрограммы прерывания.

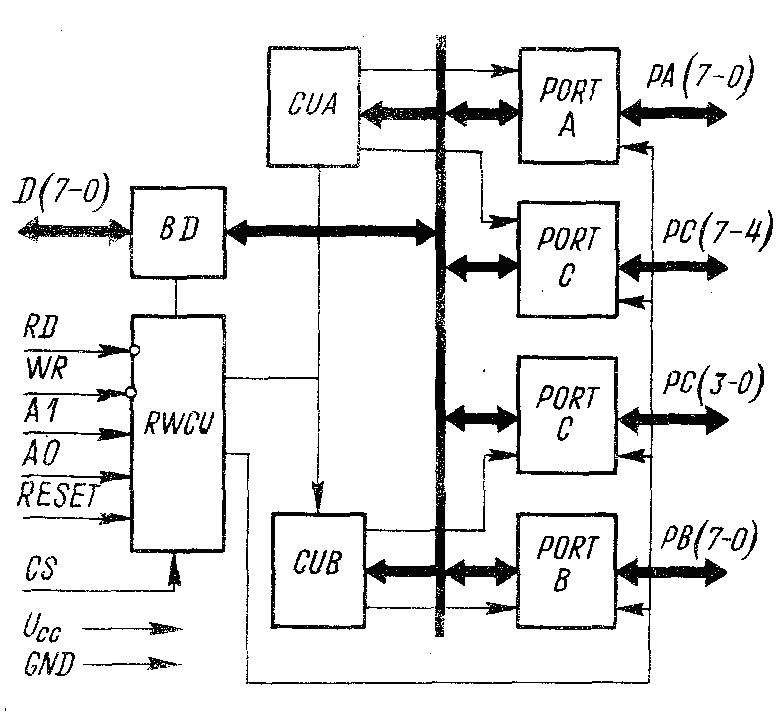

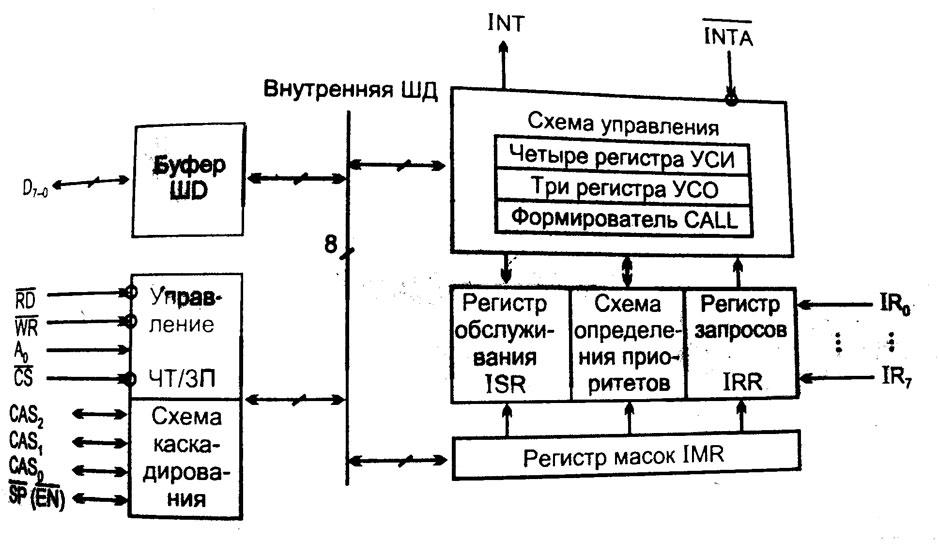

В данной микропроцессорной системе используется контроллер прерываний К1810ВН59А. Структурная схема изображена на рисунке 26.

Рисунок 13 – Структурная схема контроллера прерываний К1810ВН59А

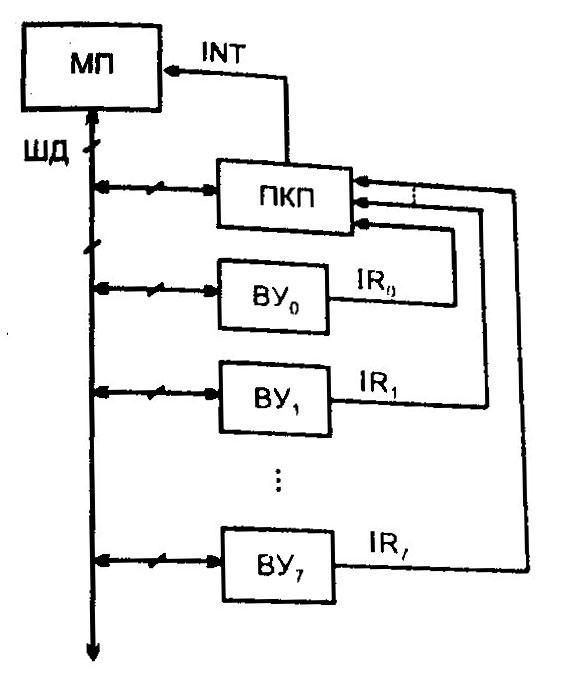

Включение контроллера прерываний в систему показано на рисунке 27.

Рисунок 14 – Включение контроллера прерываний в МПС

Контроллер принимает запросы от внешних устройств, определяет, какой из незамаскированных запросов имеет наивысший приоритет, сравнивает его с приоритетом текущей программы и при соответствующих условиях выдает запрос прерывания INT для МП. После подтверждения запроса МП должен получить от котроллера информацию, которая укажет на подпрограмму, соответствующую данному ВУ.