- •Введение

- •Расшифровка и анализ задания

- •2.2 Система команд бис к1810вм86

- •2.3 Генератор тактовых импульсов

- •2.4 Буферные регистры

- •2.5 Шинные формирователи

- •2.6 Контроллер шин к1810вг88

- •2.7 Арбитр шин к1810вб89

- •2.8.2 Формирование магистралей адреса, данных и управления

- •4.3 Разработка контроллера прямого доступа к памяти

- •16К/64к – вход выбора режима. Сигнал высокого уровня на этом входе задает режим работы кдп с озу емкостью 16к слов, а сигнал низкого уровня – режим работы с озу емкостью 64к.

- •6 Организация управления мпс

- •6.1 Сопряжение с клавиатурой

- •6.2 Сопряжение с дисплеем

- •7 Построение мпс

2.4 Буферные регистры

При разработке функциональной схемы модуля центрального процессора возникает потребность в демультиплексировании шины адреса/данных, буферизации адреса и шин данных. Демультиплексирование осуществляется с помощью двух БИС К580ИР82, которые выполняют функции защелки адреса и буфера шины адреса. Буферизация шин данных создается с помощью двунаправленных шинных формирователей К580ВА86, усиливающих сигналы шины данных.

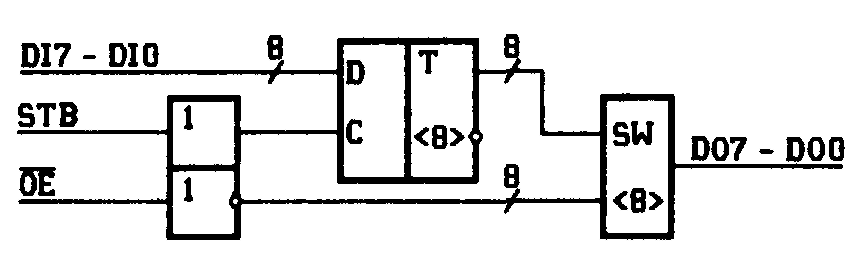

Буферные регистры К580ИР82 состоят из восьми информационных триггеров (Т) с выходными схемами (SW) с тремя состояниями, общими сигналами записи информации STB и управления выходными схемами ОЕ. К выходным схемам буферных регистров подключены прямые выходы информационных триггеров.

Рисунок 7 - Функциональная схема К580ИР82

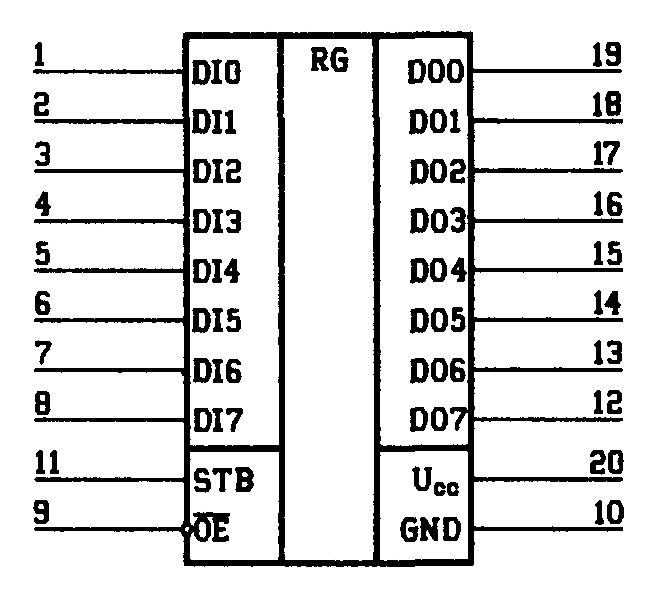

Рисунок 8 - Условно-графическое обозначение К580ИР82

D17-D10 – линии входных данных;

D07-D00 – линии выходных данных;

STB – стробирующий сигнал;

![]() –

разрешение выдачи данных.

–

разрешение выдачи данных.

При сигнале высокого уровня

на входе STB

состояние входных линий D17-D10

передается на выходные линии D07-D00.

Запоминание (защелкивание) в

информационных триггерах осуществляется

при переходе сигнала STB

от высокого уровня к низкому (по срезу

сигнала STB).

Сигнал

![]() управляет выходными буферами: при

управляет выходными буферами: при

![]() =0

буфер отпирается, при

=0

буфер отпирается, при

![]() =1

он устанавливается в

z-состояние.

Сигнал

=1

он устанавливается в

z-состояние.

Сигнал

![]() не влияет ни на состояния информационных

триггеров, ни на функцию записи.

не влияет ни на состояния информационных

триггеров, ни на функцию записи.

2.5 Шинные формирователи

Восьмиразрядные шинные формирователи КР580ВА86 применяют как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. Полная конструктивная совместимость с БР ИР82/83 допускает взаимозаменяемость при однонаправленной передаче.

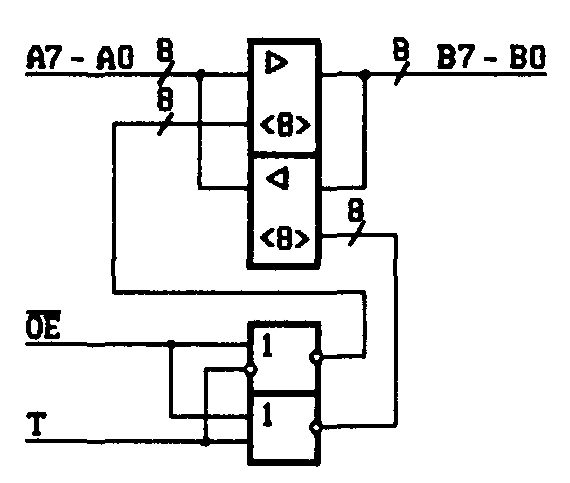

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления Т и ОЕ. Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу. Формирователь ВА86 (рисунок 9, 10) не инвертирует данные.

Рисунок 9 - Функциональная схема К580ВА86

Рисунок 10 - Условно-графическое обозначение К580ВА86

А7-А0 – вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т – сигнал высокого уровня, и выходными, если на Т – сигнал низкого уровня.

В7-В0 – вход/выход линий данных. Они являются входными, если на Т – сигнал низкого уровня, и выходными, если на Т – сигнал высокого уровня.

Т – входной сигнал управления направлением передачи. При Т=0 осуществляется передача от В к А (режим В→А), при Т=1 – от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу.

Основные достоинства шинных формирователей: большой выходной ток при малом входном токе и отсутствие шума на выходе при переключениях.

2.6 Контроллер шин к1810вг88

Микросхема К1810ВГ88 представляет собой контроллер шин (КШ), используемый в сложных системах управления и обработки информации на базе микропроцессора К1810ВМ86. КШ осуществляет генерацию команд и управляющих сигналов для системного и локального каналов микропроцессорных систем.

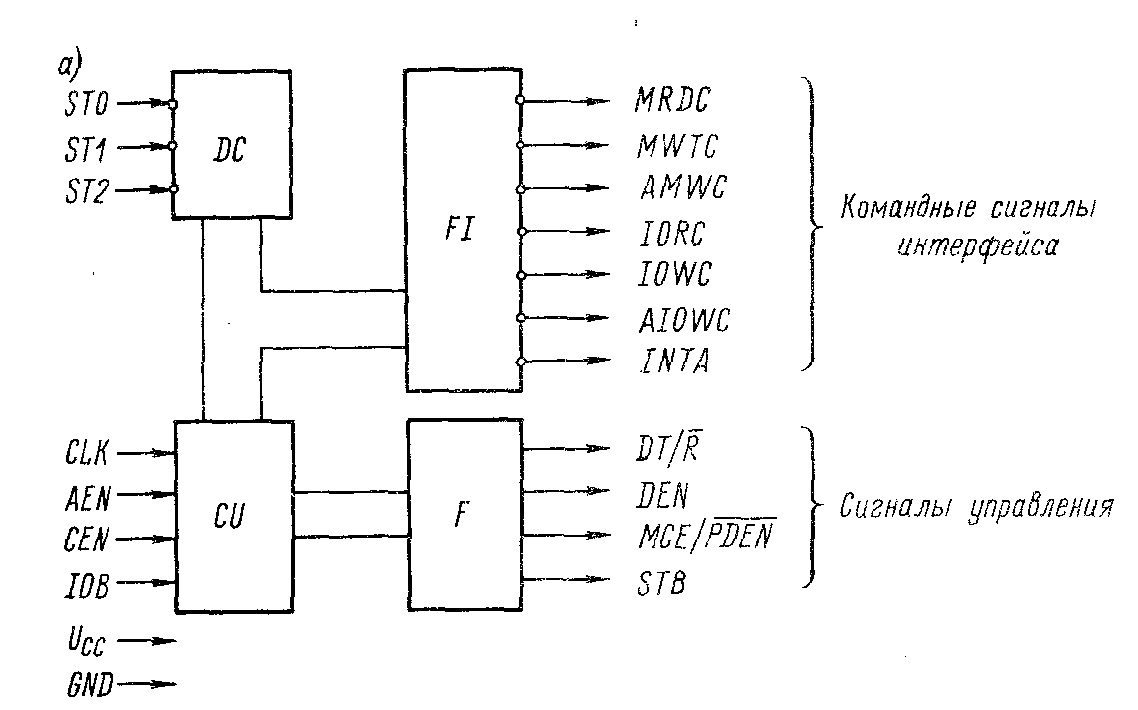

Структурная схема КШ приведена на рисунке 11. В состав микросхемы входят: дешифратор состояния (ВС); схема управления (СU); формирователь командных сигналов (FI); формирователь управляющих сигналов (F).

Рисунок 11 - Структурная схема контроллера шин

Назначения входных, выходных и управляющих сигналов КШ приведены в таблице 7.

Таблица 7 - Описание выводов КШ

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

ST(2-0) |

18; 19; 3 |

Входы сигналов состояния микропроцессора |

|

CLK |

2 |

Вход сигнала от ГТИ |

|

AEN |

6 |

Вход сигнала разрешения адресации, открывающего командные выходы КШ при L-уровне и переводящего их в высокоимпедансное состояние при Н- уровне |

|

CEN |

15 |

Вход сигнала разрешения команды, открывающего командные выходы и управляющие выходы DEN и PDEN ЕШ при Н-уровне и переводящего их в пассивное состояние при L-уровне |

|

IOB |

1 |

Вход сигнала режима управления каналом; при сигнале Н-уровня устанавливается режим управления каналом ввода/вывода, при сигнале L-уровня — режим управления системным каналом |

|

MRDC |

7 |

Вход командного сигнала чтения из памяти

|

Продолжение таблицы 7

|

1 |

2 |

3 |

|

MWTC |

9 |

Вход командного сигнала записи в память |

|

AMWC |

8 |

Вход командного сигнала записи в память с упреждением. (Сигнал AMWC появляется в цикле канала на такт раньше сигнала MWTC) |

|

IORC |

13 |

Выход командного сигнала считывания из УВВ |

|

IOWC |

11 |

Выход командного сигнала записи в УВВ |

|

AIOWC |

12 |

Выход командного сигнала записи с упреждением. (Сигнал является в цикле канала на такт раньше сигнала IOWC) |

|

INTA |

14 |

Выход командного сигнала подтвержде-ния прерывания |

|

|

4 |

Выход сигнала, задающего направление передачи информации через приемопере-датчики (H-уровень сигнала при записи, L-уровень — при считывании) |

|

DEN |

16 |

Выход сигнала разрешения передачи данных, используемый для отпирания приемопередатчиков |

|

|

17 |

Вывод выполняет две

функции: 1) при сигнале IOB

L-уровня

выходной сигнал МСЕ

служит для считывания

адреса из

имеющего наивысший приоритет контроллера

прерываний; 2) при

сигнале IOB

H-уровня

выходной сигнал

|

|

STB |

5 |

Выход сигнала стробирования адреса |

|

UCC |

20 |

Напряжение питания ( + 5 В) |

|

GND |

10 |

Напряжение питания (0 В) |

КШ формирует командные сигналы интерфейса на основании сигналов состояния (типа цикла канала) микропроцессора К1810ВМ86. Сигналы состояний и соответствующие им командные сигналы КШ также приведены в таблице 7.

КШ работает в режиме

управления каналом ввода/вывода,

если сигнал IOB

имеет H-уровень.

В этом режиме все выходы командных

сигналов ввода/вывода (IORС,

IOWС,

ATOWС

и INTА)

находятся в открытом состоянии

независимо от сигнала АЕN.

Если микропроцессору необходимо

выполнить ввод/вывод, КШ переводит

командные сигналы в активное состояние,

а для управления приемопередатчиками

канала ввода/вывода применяются

сигналы PDEN

и

![]() .

Для управления системным каналом в этом

случае выходы командных сигналов

ввода/вывода не используются. Данный

режим позволяет с помощью одного КШ

обслуживать два канала: системный канал

и канал ввода/вывода.

.

Для управления системным каналом в этом

случае выходы командных сигналов

ввода/вывода не используются. Данный

режим позволяет с помощью одного КШ

обслуживать два канала: системный канал

и канал ввода/вывода.

При L-уровне сигнала IOB контроллер работает в режиме управления системным каналом. В этом режиме используется один канал и более одного МП, поэтому для разрешения конфликтов при использовании канала необходим арбитр шины, который формирует сигнал AEN L-уровня, разрешающий обращение к каналу. В режиме управления системным каналом командные сигналы формируются не раньше чем через 85 не после перехода на L-уровень сигнала AEN.

Основные электрические параметры микросхемы К1810ВГ88:

Входное напряжение логического нуля UIL , В 0,8.

Входное напряжение логической единицы UIH, В 2,0.

Выходное напряжение логического нуля UOL, В:

на командных выходах 0,5;

на управляющих выходах 0,5.

Выходное напряжение логической единицы UOH В:

на командных выходах 2,4;

на управляющих выходах 2,4.

Ток потребления источника питания ICC, мА 170.