- •Введение

- •1 Расшифровка технического задания

- •2.1.2 Логическая организация микропроцессора z-80

- •2.1.3 Уго и описание выводов микропроцессора z80

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Системный контроллер и шинный формирователь кр580вк28

- •2.6 Программируемый параллельный интерфейс кр580вв55

- •3.2 Описание бис пзу

- •4.2 Контроллер прямого доступа к памяти кр580вт57

- •4.3 Программируемый контроллер прерываний кр580вн59

- •4.4 Программируемый контроллер клавиатуры и индикации кр580вв79

- •5 Разработка блок-схемы управляющей программы

- •6 Реализация устройства музыкальный звонок на основе мп z80

- •Заключение

2.6 Программируемый параллельный интерфейс кр580вв55

Микросхема КР580ВВ55 представляет собой программируемое устройство, используемое для ввода — вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: А, В, С. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи, как данных, так и управляющих сигналов.

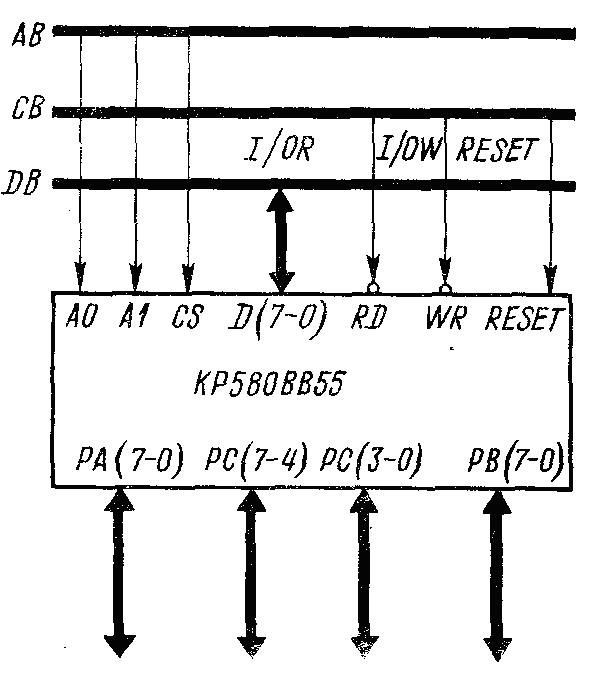

Структурная схема ППИ приведена на рисунке 8.

Рисунок 8 — Структурная схема программируемого параллельного интерфейса КР580ВВ55

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С [РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С [РС(3-0)].

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 5. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 9. Сигналы управления работой ППИ подаются на блок К\УС11 и вместе с адресными входами АО, А1 задают вид операции, выполняемой БИС

Таблица 5 — Описание выводов программируемого параллельного интерфейса КР580ВВ55.

-

Обозначение вывода

Номер контакта

Назначение вывода

D(7-0)

27; 28; 29; 30;

31; 32; 33; 34

Вход/выход данных

RD

5

Чтение; L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D(7-0)

WR

36

Запись; L-уровень сигнала разрешает запись информации с шипы D(7—0) в регистр ППИ, адресуемый по входам А0, А1

АО, А1

9; 8

Входы для адресации внутренних регистров ППИ

RESET

35

Сброс; H-уровень сигнала обнуляет регистр управляющего слова и устанавливает все порты в режим ввода

CS

6

Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине

РА(7-0)

37; 38; 39; 40;

1; 2; 3; 4

Вход/выход канала А

РВ(7-0)

15; 24; 23; 22;

21; 20;19; 18

Вход/выход канала В

РС(7-0)

10; 11; 12; 13:

17; 16; 15; 14

Вход/выход канала С

Ucc

26

Напряжение питания ( + 5 В)

GND

7

Напряжение питания (0 В)

Рисунок 9 — Схема сопряжения программируемого параллельного интерфейса КР580ВВ55 со стандартной системной шиной

Основные электрические параметры микросхемы КР580ВВ55 следующие:

Выходное напряжение логического нуля UOL, В < 0,4

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления от источника питания ICC, мА < 60

Ток утечки каналов А, В, С, D

при невыбранном режиме IIOZ, мкА >100,...,100

Ток утечки на управляющих входах IIL, мкА 10,...,10

Режимы работы каждого из каналов ППИ программируется с помощью управляющего сигнала. Управляющее слово может задать один из трех режимов основной режим ввода/вывода (режим 0), стробируемый ввод/вывод (режим 1) , режим двунаправленной передачи информации (режим 2).Одним управляющим словом можно установить различные режимы работы для каждого из каналов

Канал А может работать в любом из трех режимов, канал B в режимах 0 и 1. Канал С может быть использован для передачи данных только в режиме 0, а в остальных режимах он служит для передачи управляющих сигналов , сопровождающих процесс обмена по каналам А и B.

Режим 0 применяется при синхронном обмене или при программной организации асинхронного обмена. Микросхема может рассматриваться в этом режиме как устройство, состоящих из четырех портов, независимо настраиваемых на ввод или вывод. Вывод информации осуществляется по команде OUT микропроцессора с фиксацией выводимой информации в регистрах каналов, а ввод - по команде IN , без запоминания информации.

Режим 1 обеспечивает стробируемый однонаправленный обмен информации с внешним устройством. Передача данных производится по канал А и В, а линии канал С управляют передачей. Работу канала в режиме 1 сопровождают три управляющих сигнала.

В режиме 1 для ввода информации используют следующие управляющие сигналы: строб приема (STB) - входной сигнал, формируемый внешним устройством, указывает на готовность ВУ к вводу информации; подтверждение приема (IBF) - выходной сигнал ППИ, сообщающий ВУ об окончании приема данных в канал; запрос прерывания (INTER) - выходной сигнал ППИ, информирующий МП о завершении приема информации в канале.

Для вывода информации в режиме 1 используются следующие управляющие сигналы: строб записи (OBF) - выходной сигнал, указывающий внешнему устройству о готовности к выводу, формируется по фронту WR; подтверждение записи (ACK) - входной сигнал от внешнего устройства, подтверждающий прием информации из ППИ; запрос прерывания (INTR) - выходной сигнал ППИ, информирующий МП о завершении операции вывода информации.

Режим два обеспечивает двунаправленную передачу информации по каналу А к внешнему устройству и обратно. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям PC7-PC3. Оставшиеся 11 интерфейсных линий могут настраиваться на режим 0 или режим 1.Управление установкой внутреннего сигнала INTE для операции ввода осуществляется по линии PC4, а для операции вывода по линии PC6.

В режимах 1 и 2 возможно проведение контроля за состоянием работы внешнего устройства и ППИ .Контроль осуществляется чтением слова - состояния канала С по команде OUT.

3 РАЗРАБОТКА ПОДСИСТЕМЫ МАМЯТИ

3.1 ОПИСАНИЕ БИС ОЗУ

Микросхема КP565PУ6 - является динамического типа. В таких микросхемах функции элемента памяти выполняет электрический конденсатор образованный внутри МДП-структуры. В таком элементе памяти информация (один бит) представляется в виде заряда (напряжения) наличие заряда в запоминающем конденсаторе соответствует нулю, его отсутствие единице.

В микросхемах динамических ОЗУ для записи и считывания информации используются процессы перезарядки емкостей запоминающих конденсаторов и разрядных шин кратковременными токами через транзисторные усилители запаси считывания. В режиме хранения эти токи не протекают по тому, что, во-первых, емкостные цепи находятся в установившемся режиме и, во-вторых, снимается питание усилителей.

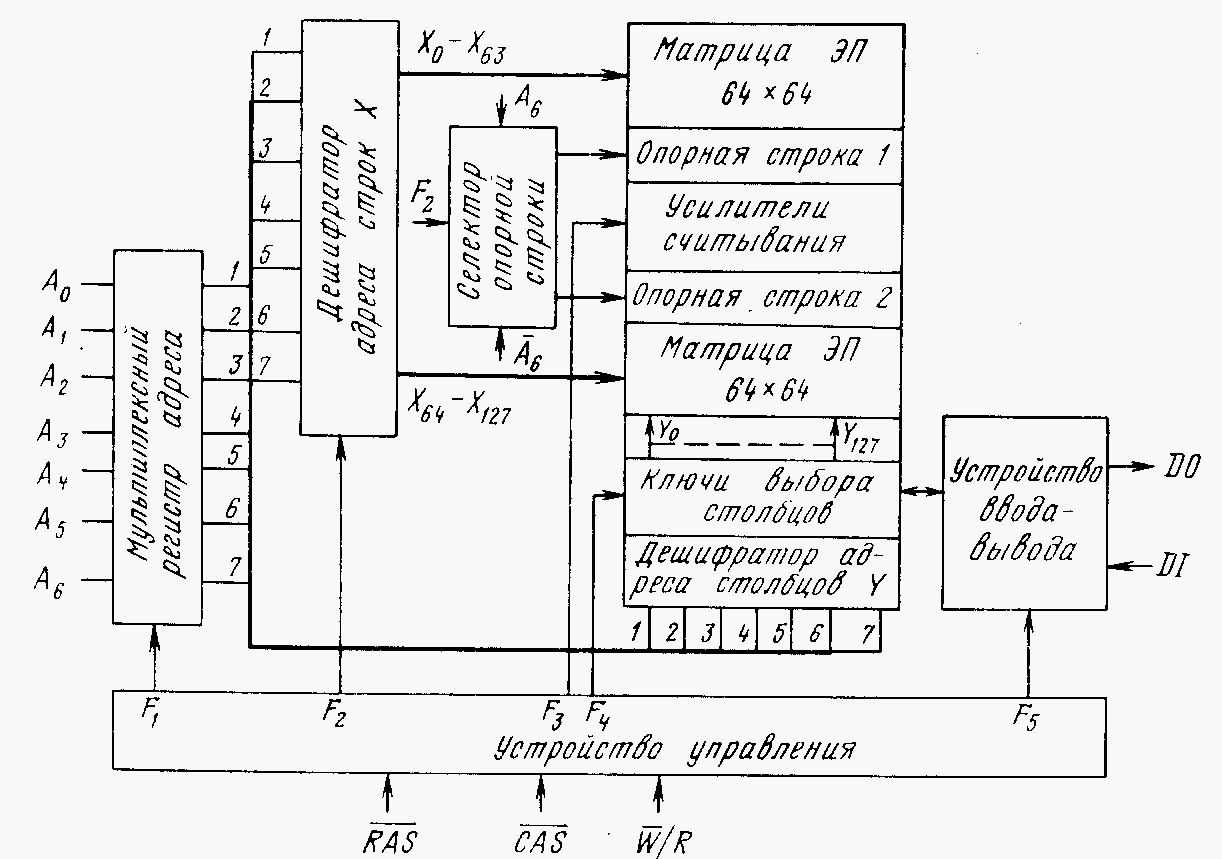

Поэтому для микросхем динамических ОЗУ характерно существенное снижение потребляемой мощности в режиме хранения по сравнению с активным режимом. На рисунке 10 представлена структурная микросхема динамического ОЗУ КP565PУ6.

Рисунок 10 - Структурная микросхема ОЗУ КP565PУ6

В структурную схему входят выполненные в одном кремневом кристалле матрица накопителя, содержащая 16384 элементов памяти, расположенных на пересечениях 128 строк и 128 столбцов, 128 усилителей считывания и регенерации, дешифраторы строк и столбцов, устройство управления, устройство ввода-вывода, мультиплексный регистр адреса.

Матрица накопителя разделена на две части 64 на 64 ЭП в каждой. Между ними размещены усилители, так что каждый столбец состоит из двух секций, подключенных к разным плечам усилителя.

Также матрица имеет опорные элементы. Эти элементы в каждой половине матрицы составляют опорную строку. При каждом обращении к матрице для считывания информации автоматически осуществляется регенерация информации во всех ЭП, принадлежащих выбранной строке. Д

ля адресации 16К элементов памяти необходим 14-разрядный код, а у рассматриваемой микросхемы только семь адресных входов. С целью уменьшения числа необходимых выводов корпуса в динамических ОЗУ код адреса вводят по частям: в начале семя младших разрядов А0-А6 , сопровождая их стробирующим сигналом RAS, затем семь старших разрядов А7-А13 , со стробирующим сигналом CAS. В нутрии микросхемы коды адреса строк и столбцов фиксируются на адресном регистре, затем дешифрируются и осуществляют выборку адресуемого ЭП.

Для формирования внутренних сигналов F1 и F4 управляющих включением и выключением в определенной последовательности функциональных узлов микросхем в ее структуре предусмотрено устройство управления, для которого входными являются сигналы RAS ,CAS ,W/R.

Устройство ввода вывода обеспечивает вывод одного бита информации DO в режиме считывания и ввод одного бита информации DI с ее фиксацией с помощью триггера-защелки в режиме записи.

Условно графическое изображение ОЗУ КP565PУ6 представлена на рисунке 11.

Рисунок 11 - Условно графическое изображение ОЗУ КP565PУ6

Микросхема работает в следующих режимах: записи, считывания, считывания - модификации - записи (RWM), слоговой и страничной записи, слогового и страничного считывания регенерация, хранение с регенерацией.

Внешние сигналы: RAS -сигнал выбора адреса строк, С AS — сигнал выбора адреса столбцов, WE — сигнал записи/считывания, а также сигналы, вырабатываемые схемой управления, обеспечивают работу ОЗУ в режимах считывания, записи, постраничного считывания или постраничной записи, считывания- модификации-записи, регенерации по сигналу RAS.

Рассмотрим названные режимы и условия их реализации.

При обращении к микросхеме для записи информации необходимо подать код адреса строк и одновременно с ним или с некоторой задержкой сигнал PAS ,затем с задержкой на время удержания адреса строк относительно сигнала PAS tн(RAS-A) на эти же выводы поступает код адресов столбцов и с задержкой на время tн(A-CAS) подается сигнал CAS. К моменту подачи кода адреса столбцов на вход D1 подается записываемый байт информации, который сигналом WR/RD при наличии CAS=0 фиксируется на входном триггере - защелке. Сигнал может быть подан уровнем или длительностью tw(WR). Если этот сигнал подан уровнем, то фиксацию входных данных триггер-защелка производит по отрицательному перепаду сигнала CAS при наличии сигнала RAS в активном состоянии. По окончании записи должна быть выдержана пауза между сигналами RAS для восстановления состояния внутренних цепей микросхемы. В режиме считывания порядок следования адресных и управляющих сигналов аналогичен рассмотренному, но при наличии сигнала считывания WR/RD=1

Для оценки быстродействия микросхемы памяти в расчет необходимо принимать время цикла записи (считывания). Микросхемы динамического ОЗУ характеризуются набором временных параметров, регламентирующих длительности импульсных сигналов, интервалы между ними. Взаимный сдвиг во времени. Для обеспечения надежного сохранения записанной в накопителе информации предусмотрен режим принудительной регенерации, которой подвергается каждый элемент памяти в интервале времени. Регенерация выполняется автоматически для всех элементов памяти выбранной строки при каждом обращении к накопителю для записи или считывания информации.

Микросхема КP565PУ6 отличается от других микросхем тем, что обладает более высокое быстродействие, требует для работы один источник питания напряжением 5В. После включения питания нормальный режим функционирования устанавливается после паузы в две миллисекунды и последующих 8-16 циклов в любом режиме.