- •Введение

- •1 Расшифровка технического задания

- •2.1.2 Логическая организация микропроцессора z-80

- •2.1.3 Уго и описание выводов микропроцессора z80

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Системный контроллер и шинный формирователь кр580вк28

- •2.6 Программируемый параллельный интерфейс кр580вв55

- •3.2 Описание бис пзу

- •4.2 Контроллер прямого доступа к памяти кр580вт57

- •4.3 Программируемый контроллер прерываний кр580вн59

- •4.4 Программируемый контроллер клавиатуры и индикации кр580вв79

- •5 Разработка блок-схемы управляющей программы

- •6 Реализация устройства музыкальный звонок на основе мп z80

- •Заключение

2.1.3 Уго и описание выводов микропроцессора z80

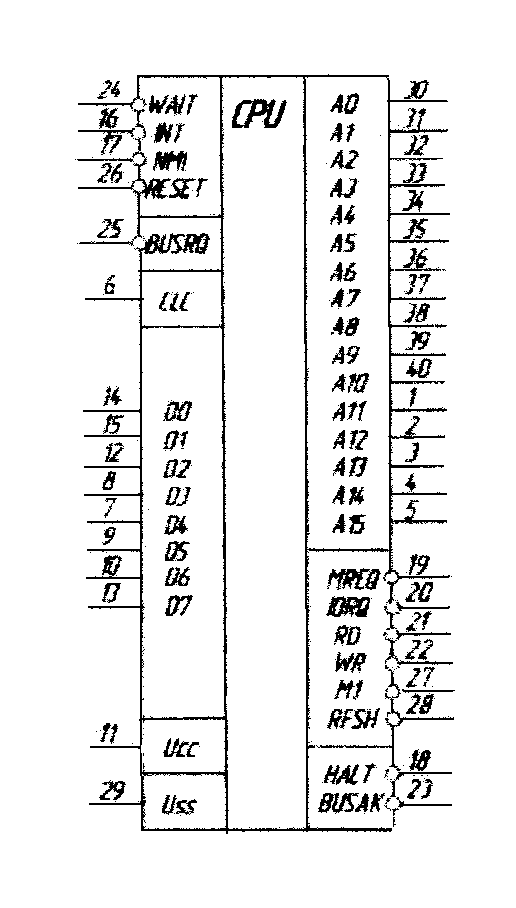

На рисунке 2 представлено условное графическое обозначение микропроцессора Z80

Рисунок 2 - Условное графическое обозначение микропроцессора Z80

Микропроцессор Z80 - это микросхема с 40 выводами, пронумерованными от 1 до 40. Рассмотрим функции выводов и поясним указанные на нем метки.

Описание шин:

- АО — А15 - Adress Bus — Адресная шина АО-А15 образуют 16- разрядную адресную шину — трехстабильная выходная шина адреса Выход с тремя состояниями. Активный уровень - высокий; выдает адреса для обмена с 65536 ячейками памяти (64 Кбайт) или с таким же числом ячеек устройств ввода-вывода;

- DO — D7 - Data Bas - Шина данных — трехстабильная двунаправленная шина данных; осуществляет обмен (принимает или выдает данные) с памятью или устройствами ввода-вывода. Трехстабильный вход-выход. Активный уровень - высокий;

- DO-D7 образует 8-разрядную двунаправленную шину данных, по которой осуществляется обмен между ЦП и памятью, либо между ЦП и устройствами ввода-вывода. Для увеличения нагрузочной способности шина данных выполнена по схеме с открытым коллектором. Поэтому необходимо каждый из 8 выходов шины данных подключить через резистор 2,2-6,8 Ком к потенциалу Ucc =+5V.

- шина управления, сигналы на которой можно условно разделить на системные (MREQ, IORQ, RD, WR, Ml, RFSH), управления процессором (WAIT, INT, NMI, RESET) и управления шинами (HALT, BUSRQ, BUSAK). Все сигналы шины управления имеют низкий активный уровень.

MREQ (MEMORY REQUEST — запрос памяти) — трехстабильный выход, активизирующийся при обращении микропроцессора к ячейкам памяти. Активный уровень - низкий. При активизации сигнала на шине адреса уже установлен адрес требуемой ячейки памяти для ввода или вывода данных.

IORQ (INPUT/OUTPUT REQUEST — запрос ввода-вывода) — трехстабильный выход. Активный уровень - низкий. Сигнал IOREQ указывает, что шина адреса содержит адрес внешнего устройства для операции ввода или вывода. Кроме того, сигнал IOREQ генерируется также совместно с сигналом Ml в цикле подтверждения прерывания. Тем самым устройству, запросившему прерывание, указывается, что вектор прерывания может быть помещен на шину данных.

По комбинациям системных сигналов Z80 активизирует внешние устройства в зависимости от того, какая операция выполняется в текущее время. Например, при чтении данных из памяти одновременно активизируются сигналы MREQ и RD; при чтении кода операции к ним добавляется сигнал Ml; при записи в устройство ввода-вывода активизируются IORQ и WR и т.д. Таким образом, процесс управления внешними устройствами сводится к простому логическому объединению соответствующих сигналов.

Сигналы управления микропроцессором, как говорит само название, предназначены для аппаратного изменения его состояния со стороны внешних устройств. Все сигналы управления являются по отношению к процессору входными, активный уровень — низкий.

WAIT (WAIT - ожидание Запрос ожидания). Этот сигнал поступает от внешнего устройства (памяти или устройства ввода-вывода), При активизации этого сигнала микропроцессор начинает выполнять «холостые» такты, т. е. не изменяет своего состояния до момента снятия сигнала.

Вход. Активный уровень - низкий. Сигнал WAIT указывает ЦП, что адресованная ячейка памяти или устройство ввода-вывода еще не готово к передаче данных. ЦП генерирует состояние ожидания (холостые такты, в которых не происходит никаких изменений с ЦП) до тех пор, пока активен этот сигнал. С помощью этого сигнала с ЦП могут синхронизироваться ЗУ и устройства ввода-вывода практически любого быстродействия. WAIT также может использоваться при отладке для реализации пошагового режима. С помощью сигнала WAIT удается синхронизировать работу микропроцессора с более «медленными» внешними устройствами.

INT (INTERRUPT REQUEST -запрос прерывания). Микропроцессор опрашивает состояние этой линии каждый раз после выполнения текущей команды. При обнаружении на ней сигнала с низким уровнем он переходит к выполнению программы обработки прерывания, расположенной по определенному адресу в памяти. Адрес задается программно-аппаратными средствами с помощью одного из трех режимов прерывания. Возврат из программы осуществляется по команде возврата RET I. Этот вид прерывания называют маскируемым, т. е. он может быть запрещен или разрешен соответствующими командами: D1 (запрещение прерывания) и Е1 (разрешение прерывания). Вход. Активный уровень - низкий. Сигнал INT, формируемый устройством ввода-вывода, анализируется в конце выполнения текущей команды. Запрос учитывается, если триггер прерываний (IFF1), управляемый программно, установлен в состояние «разрешить прерывание», и не активен сигнал BUSRQ.

NMI (NON MASKABLE INTERRUPT — немаскируемый запрос прерывания) — сигнал, аналогичный INT, однако его запуск происходит не уровнем, а спадом импульса, поступающего на вход NMI; прерывание не может быть запрещено программно, возврат происходит по команде RET N и переход осуществляется на фиксированную подпрограмму, начинающуюся в ячейке памяти с адресом 102 (66Н). Сигнал NMI имеет более высокий приоритет по отношению к INT. Данное прерывание используется в Sp-компьютере при работе с накопителем на гибких магнитных дисках.

Вход, запускаемый отрицательным фронтом. Фронт запуска активизирует внутренний триггер NMI. Линия NMI имеет более высокий приоритет, чем INT и всегда распознается в конце выполнения текущей команды, независимо от состояния триггера разрешения прерываний. INT автоматически производит перезапуск (рестарт) ЦП с адреса 66Н. Содержание счетчика команд (адрес возврата) автоматически сохраняется во внешнем стеке. Таким образом, пользователь может возвратиться к прерванной программе.

RESET (RESET - сброс) — сигнал управления сбросом, имеющий самый высокий приоритет. После снятия с линии RESET сигнала низкого уровня (который должен длиться не менее трех периодов тактовой частоты) микропроцессор автоматически переходит к выполнению программы, начинающейся в ячейке памяти с адресом 0, При этом запрещается прерывание INT, устанавливается нулевой режим прерываний (IMO; подробнее об этом будет сказано далее), очищаются регистры регенерации (R) и вектора прерывания (I). Во время действия низкого уровня на выводе RESET линии шин данных, адреса, а также RD, WR, MREQ и IORQ микропроцессора переводятся в третье — выключенное — состояние (Z-состояние).

Вход. Активный уровень - низкий. Сигнал RESET имеет самый высокий приоритет и приводит ЦП в начальное состояние:

-

сброс счетчика команд PC = 0000H;

-

очистка регистров I и R;

-

установка режима прерываний IMO.

Для корректного сброса сигнал RESET должен быть активен не менее 3-х периодов тактовой частоты, В это время адресная шина и шина данных находятся в высокоимпедантном состоянии, а все выходы сигналов управления неактивны.

Сигналы управления шинами предназначены для передачи управления другим устройствам.

HALT (HALT STATE - состояние останова) — выход с низким активным уровнем, извещающий внешние устройства о том, что выполнена команда останова HALT. При этом процессор начинает беспрерывно выполнять «пустую» команду NOP (делается это для продолжения регенерации памяти). Вывести микропроцессор из этого состояния можно только прерыванием.

Выход. Активный уровень - низкий. Сигнал HALT указывает, что ЦП выполняет команду останова программы и ожидает маскируемое либо немаскируемое прерывание, чтобы завершить эту команду и начать обработку подпрограммы прерывания. В состоянии останова ЦП выполняет холостые команды для обеспечения процесса регенерации памяти. В данной схеме этот сигнал не используется.

BUSRQ (BUS REQUEST - запрос доступа к шине) — входной сигнал с низким активным уровнем; анализируется процессором в конце любого машинного цикла, при обнаружении низкого уровня линии шин данных, адреса, а также RD, WR, MREQ и IORQ переводятся в выключенное состояние, и управление шинами передается внешнему устройству.

Вход. Активный уровень - низкий. Сигнал BUSRQ имеет более высокий приоритет, чем NMI и анализируется в конце - каждого машинного цикла. Он делает запрос ЦП на перевод всех его шин в высокоимпедансное состояние для того, чтобы другие устройства смогли управлять этими шинами (например, при прямом доступе к памяти). Если активизирован сигнал BUSRQ, то ЦП переводит шины в высокоимпедансное состояние, как только завершен текущий машинный цикл. В данной схеме этот сигнал не используется. С помощью резистора R20 на нем задана логическая 1.

BUSAK (BUS ASKNOWLEDGE — предоставление доступа к шине) — выход, сигнализирующий внешнему устройству, запросившему доступ к шине, о том, что шины микропроцессора переведены в выключенное состояние, и устройство может ими управлять.

Выход. Активный уровень - низкий. Если был активизирован сигнал BUSRQ, то ЦП переводит свои шины в высокоимпеданcное состояние, как только завершен текущий машинный цикл. После этого ЦП активизирует сигнал BUSAK, который сообщает запрашивающему устройству, что шины адреса и данных, а также трехстабильные сигналы управления находятся в высокоимпедантном состоянии, и внешнее устройство может ими управлять. В данной схеме этот сигнал не используется,

RD (READ — чтение) — трехстабильный выход, активизирующийся во время чтения микропроцессором данных из памяти или устройства ввода-вывода.

Трехстабильный выход. Активный уровень - низкий. Сигнал RD указывает, что ЦП выполняет цикл чтения данных из памяти или устройства ввода-вывода. Адресованное устройство ввода-вывода или память должны использовать этот сигнал для стробирования подачи данных на шину данных (ШД).

WR (WRITE - запись) -трехстабильный выход, активизирующийся при выдаче процессором данных в память или устройство ввода-вывода.

Трехстабильный выход. Активный уровень - низкий. Сигнал WR указывает, что процессор выдает на ШД данные, предназначенные для записи в адресованную ячейку памяти или устройство вывода.

Ml - (MASHINE CYCLE 1 -машинный цикл 1) — выход, активизирующийся при чтении кода операции из памяти. Кроме этого, совместно с выходом IORQ он активизируется в цикле подтверждения прерывания.

Трехстабильный выход. Активный уровень - низкий. Ml указывает, что в текущем машинном цикле происходит чтение кода операции из памяти. При считывании кода операции вида СВ, ЕД, DD, FD вырабатывается еще один Ml для считывания второго байта кода операции, т.е. сигнал Ml активизируется дважды.Ml также активизируется вместе с сигналом IORQ в цикле подтверждения прерывания.

RFSH (REFRESH - регенерация). В микропроцессоре Z80 имеется средство (упущенное разработчиками 8080) для регенерации динамической памяти. В состав процессора включен специальный программно доступный регистр R, называемый счетчиком регенерации памяти, содержимое которого выводится в семи младших адресах каждый раз после чтения кода операции (вслед за сигналом Ml). В этот момент одновременно активизируются только два сигнала: RFSH и MREQ. По этой комбинации сигналов устройство управления памятью определяет, что происходит регенерация памяти. После снятия сигнала RFSH значение содержимого регистра R автоматически увеличивается на 1. (Оговоримся, что в Sp-компьютере этот режим не используется; регенерация памяти в нем осуществляется дисплейным контроллером в моменты вывода информации на экран).

Выход. Активный уровень - низкий. Сигнал RFSH указывает, что младшие 7 разрядов шины адреса содержат адрес регенерации для динамической памяти и текущий сигнал MREQ может использоваться для восстановления информации. В данной схеме этот сигнал не используется.

Кроме названных, Z80 имеет вход CLC (CLOCK — такт), предназначенный для приема однофазной тактовой последовательности, и два вывода питания: Ucc (плюс источника питания) и Uss (минус источника питания, общий провод).

C-Clock —Такт

Вход для однофазной тактовой синхронизации. При управлении от TTL-схемы, вход С дополнительно подключается к линии +5V через внешнее сопротивление 330 Ом.

Ucc- «плюс» источника питания;

GND - потенциал «земли».