- •Содержание

- •1 Расшифровка и анализ задания

- •2.1 Архитектура и режимы работы мп к1810вм86

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •2.8 Разработка обобщенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.1 Контроллер прямого доступа к памяти кр580вт57

- •4.1 Программируемый таймер кр580ви53

- •4.2 Программируемый контроллер прерываний кр580вн59

- •4.4 Разработка уточненной структурной схемы

- •5 Разработка алгоритма работы микропроцессорной системы

- •В ходе курсового проекта разработана управляющая система микро - эвм, реализующая заданные взаимодействия с объектом управления.

- •Блок-схема алгоритма работы устройства позволяет определить момент выдачи управляющего воздействия , заданной длительностью.

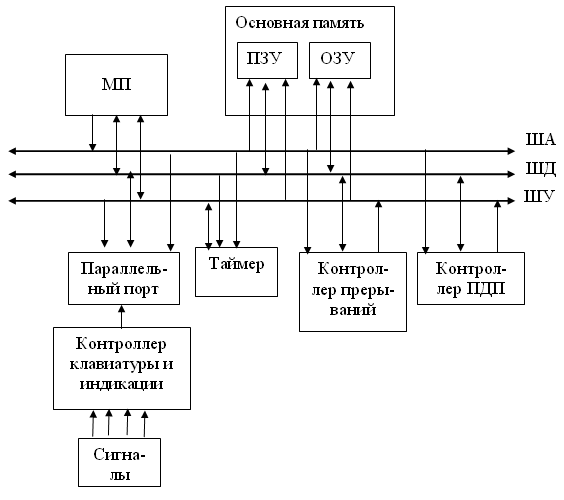

2.8 Разработка обобщенной структурной схемы

Микропроцессорный комплект серии К1810 включает в себя 8- и 16-разрядные МП, позволяющие производить высокоскоростные вычисления и обмен данными; устройства формирования магистралей и арбитража многопроцессорных взаимодействий и универсальные интерфейсные БИС, предназначенные для выполнения широкого набора функций ускоренной передачи информации.

В общем виде разрабатываемый микропроцессорный комплект серии К1810 включает:

– микропроцессор;

– генератор тактовых импульсов;

– шинный формирователь;

– буферный регистр;

– БИС ОЗУ;

– БИС ПЗУ;

– интервальный таймер;

– параллельный порт;

– устройство ввода-вывода;

– контроллер прерываний;

– контроллер ПДП.

Рисунок 2.14 – Обобщенная структурная схема МП БИС К1810ВМ86

3 Разработка подсистемы памяти

3.1 Контроллер прямого доступа к памяти кр580вт57

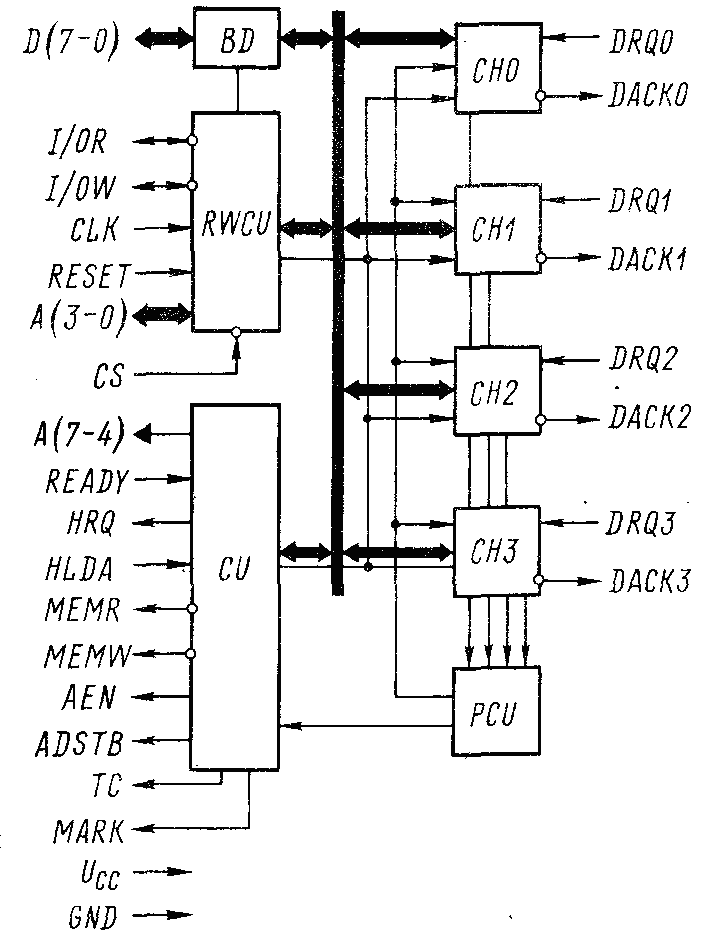

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства.

Рисунок 3.1 – Структурная схема контроллера прямого доступа к памяти КР580ВТ57

Упрощенная структурная схема КПДП приведена на рисунке 3.1. В состав БИС входят: двунаправленный двустабильный буфер данных (ВD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (СU) и обеспечивающий последовательность операций; блок управления приоритетами (РСU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (СН0 – СН3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

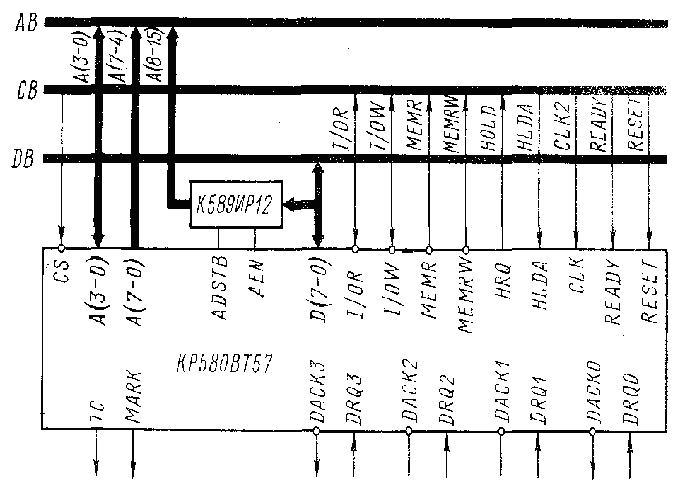

Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12 показана на рисунке 3.2.

Рисунок 3.2 – Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12

Назначение входных, выходных и управляющих сигналов КПДП приведено при описании выводов микросхемы в таблице 3.1.

Таблица 3.1 – Описание выводов контроллера прямого доступа к памяти

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

D(7–0) |

Д(7–0) |

Входы/выходы данных для обмена с МП |

Вход /выход |

H-1,L-0 |

|

|

Чтение ввода /вывода |

Чтение ввода/вывода – двунаправленный тристабильный вход /выход; вх. сигнал L – чтение |

Вход /выход |

L-1, H-0, z |

|

|

Запись ввода /вывода |

Запись ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L- разрешает программирование КПДП |

Вход /выход |

L-1, H-0, z |

|

1 |

2 |

3 |

4 |

5 |

|

Продолжение таблицы 3.1 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

CLK |

синхро |

Вход тактовых импульсов |

Вход |

H-1,L-0 |

|

RESET |

сброс |

Вход установки 0 |

Вход |

H-1,L-0 |

|

A(3-0) |

A(3-0) |

Двунаправленные тристабильные ад. выводы |

|

H-1,L-0 |

|

|

КС |

Выбор микросхемы |

|

L-1,H-0 |

|

A(7-4) |

A(7-4) |

Тристабильные адресные выходы |

Выход |

H-1,L-0 |

|

READY |

Готов |

Готовность – входной сигнал Н- готовность к обмену |

Вход |

H-1 H-1 |

|

HRQ |

ЗЗ |

Запрос захвата – выходной сигнал Н- запрос о доступе КПДП |

Выход |

H-1,L-0 |

|

HLDA |

ПЗ |

Подтверждение захвата – входной сигнал Н- доступа к СШ |

Вход |

H-1,L-0 |

|

|

Чтение из памяти |

Чтение из памяти – тристабильный выход; чтение из ячейки памяти |

Выход |

L-1, H-0, z |

|

|

Запись в память |

Запись в память – тристабильный выход; L- запись в ячейку |

Выход |

L-1, H-0, z |

|

AEN |

РА |

Разрешение адреса – сигнал используется для блокировки |

Выход |

H-1,L-0 |

|

ADSTB |

Ад строба |

Строб адреса – сигнал Н- нахождение D(7 – 0) старшего байта адреса |

Выход |

H-1,L-0 |

|

TC |

КС |

Конец счета – сигнал Н- выполнение последнего цикла |

Выход |

H-1,L-0 |

|

MARK |

Маркер |

Маркер — сигнал Н-ур. выполнить число циклов обмена, кратное 128 |

Вход |

H-1,L-0 |

|

DRQ3-DRQ0 |

СН3-СН0 |

Запросы ПДП каналов СН3-0; сигнал Н – УКазывает на запрос от ВУ |

Вход |

H-1,L-0 |

|

1 |

2 |

3 |

4 |

5 |

|

Продолжение таблицы 3.1 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

DACK3-DACK0 |

СН3-СН0 |

Подтверждение запросов ПДП каналов СН3-СН0 |

Ввыход |

L-1,H-0 |

|

UСС |

Uп |

Напряжение питания ( + 5 В) |

Вход |

|

|

GND |

ОБЩ |

Напряжение питания (0 В) |

Вход |

|

Основные электрические параметры микросхемы КР580ВТ57 при температуре окружающей среды + 25 + 10°С приведены ниже:

Выходное напряжение логического нуля UOL, В < 0,45

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления IСС, мА < 100

Ток утечки на входах IIL, мкА < 1,5

Ток утечки на управляемых выводах IОL, мкА –1,5...1,5

3.2 БИС ОЗУ К134РУ6

К134РУ6 - микросхема статических ОЗУ высокого быстродействия: время цикла обращения лежит в диапазоне значений 55 ... 85 нс. Микросхема выполнена по n-канальной МДП – технологии. Основные электрические параметры микросхемы приведены ниже:

Информационная емкость, бит 1024

Организация 1024 слов на 1 разряд

Время выборки адреса Не более 700 не

Напряжение питания, В 5±10 %

Мощность в режиме обращения, мВт не более 600

Мощность в режиме хранения, мВт не более 300

Диапазон температур, °С – 40... +85

Выход Открытый коллектор

Тип корпуса Металлокерамический, 4112.16—2

Назначение входных, выходных и управляющих сигналов ОЗУ приведено при описании выводов микросхемы в таблице 3.2.

Таблица 3.2 – Описание выводов микросхемы ОЗУ К134РУ6

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

А0…А1 |

А0…А1 |

Адресные входы |

вход |

H-1,L-0 |

|

DI |

ДИ |

Вход данных |

вход |

H-1,L-0 |

|

DО |

ДО |

Выход данных |

выход |

H-1,L-0 |

|

|

КС |

Выбор микросхемы |

вход |

H-1,L-0 |

|

|

З/С |

Сигнал запись – считывание |

вход |

L-1,H-0 |

|

UCC |

Uп |

Напряжение питания |

вход |

H-1,L-0 |

|

0В |

ОБЩ |

Общий |

вход |

H-1,L-0 |

Функциональная схема Оперативного ЗУ представлена на рисунке 3.3.

Рисунок 3.3 – Микросхема ОЗУ К134РУ6

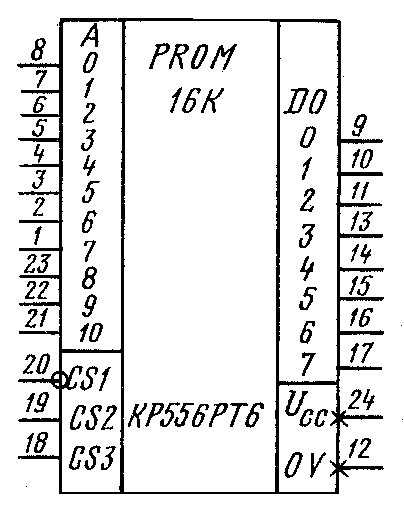

3.3 БИС ПЗУ К556РТ6

Микросхемы программируемых ПЗУ по принципу построения и функционирования аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают программирование на месте своего применения пользователем. Операция программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и доступностью микросхем ППЗУ обусловило их широкое распространение в радиолюбительской практике.

В данном курсовом проекте рассматривается применение микросхемы ПЗУ К556РТ6, представленной на рисунке 3.4.

Рисунок 3.4 – Микросхема ПЗУ К556РТ6

Основные электрические параметры ПЗУ приведены ниже:

Информационная емкость, бит 2К×8

![]() ,

нс 80

,

нс 80

Мощность

потерь

![]() ,

мВт 900

,

мВт 900

Тип выхода ТТЛ – 3 (ОК)

Исходное состояние 4112.16 – 2

Напряжение питания, В +5±0.5

Структурная схема ПЗУ приведена на рисунке 3.5.

Рисунок 3.5 – Микросхема ПЗУ К556РТ6

4 РАЗРБОТКА ПОДСИСТЕМЫ ВВОДА/ВЫВОДА, ПРЕРЫВАНИЙ, ПДП