- •Содержание

- •1 Расшифровка и анализ задания

- •2.1 Архитектура и режимы работы мп к1810вм86

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •2.8 Разработка обобщенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.1 Контроллер прямого доступа к памяти кр580вт57

- •4.1 Программируемый таймер кр580ви53

- •4.2 Программируемый контроллер прерываний кр580вн59

- •4.4 Разработка уточненной структурной схемы

- •5 Разработка алгоритма работы микропроцессорной системы

- •В ходе курсового проекта разработана управляющая система микро - эвм, реализующая заданные взаимодействия с объектом управления.

- •Блок-схема алгоритма работы устройства позволяет определить момент выдачи управляющего воздействия , заданной длительностью.

2.6 Арбитр шин к1810вб89

Арбитр шин К1810ВБ89 предназначен для использования в мультипроцессорных системах на основе микропроцессора К1810ВМ86. Арбитр шины координирует работу различных компонентов мультипроцессорной системы.

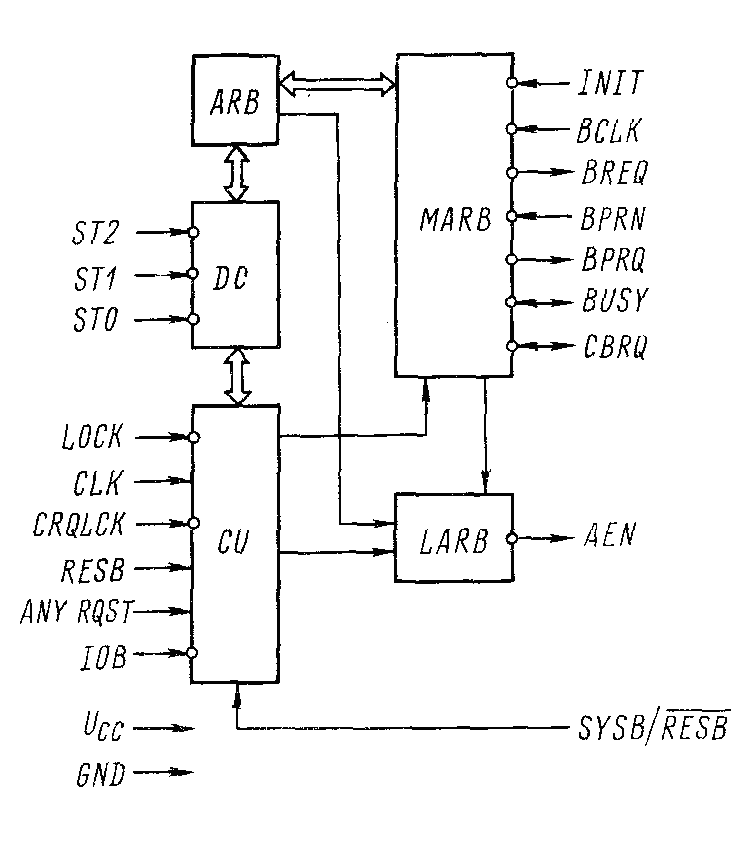

Рисунок 2.9 – Структурная схема арбитра шин

Структурная схема арбитра шины приведена на рисунке 2.9. В состав входят: схема арбитража (АRB); дешифратор состояния (DС); схема управления (СU); интерфейс с MULTIBAS (МАRВ); интерфейс с локальным каналом (LАRВ).

Назначения входных и выходных сигналов арбитра шины приведены при описании выводов микросхемы в таблице 2.8.

Таблица 2.8 – Описание выводов арбитра шин

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

ST(2 - 0) |

ЛС(2 - 0) |

Входы сигналов состояния МП |

Входы |

H-1,L-0 |

|

LOCK |

блок |

Вход сигнала блокировки от МП |

Вход |

H-1,L-0 |

|

CLK |

синхро |

Вход сигнала синхронизации |

Вход |

H-1,L-0 |

|

GND |

ОБЩ |

Напряжение питания (0 В) |

Вход |

|

|

CRQLCK |

БОЗ |

Вход сигнала блокировки об. запр. |

Вход |

H-1,L-0 |

|

|

ЛК |

Вход сигнала, используемого в режиме локал. канала |

Вход |

L-1,H-0 |

|

1 |

2 |

3 |

4 |

5 |

|

Продолжение таблицы 2.8 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

RESB |

ПРК |

Вход сигнала переключения в режим резидентного канала |

Вход |

H-1,L-0 |

|

ANYRQST |

ППУ |

Вход сигнала переключения в режим передачи управления |

Вход |

H-1,L-0 |

|

IOB |

переключения |

Вход сигнала переключения в режим канала ввода/вывода |

Вход |

H-1,L-0 |

|

BPRQ |

ПР |

Выход сигнала приоритетного разрешения канала |

Входы |

H-1,L-0 |

|

BUSY |

ЗСК |

Вывод двунаправленного сигнала занятости системного канала |

Входы |

H-1,L-0 |

|

CBRQ |

запроса шины |

Вывод двунаправленного сигнала общего запроса шины |

Входы |

H-1,L-0 |

|

AEN |

РА |

Выход сигнала разрешения адреса |

Входы |

H-1,L-0 |

|

Ucc |

Uп |

Напряжение питания ( + 5 В) |

Вход |

|

Основные электрические параметры микросхемы К181ОВБ89:

Входное напряжение логического нуля UIL, В < 0,8

Входное напряжение логической единицы UIH, В > 2,0

Выходное напряжение логического нуля UOL, В < 0,45

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления источника питания ICC, мА < 165

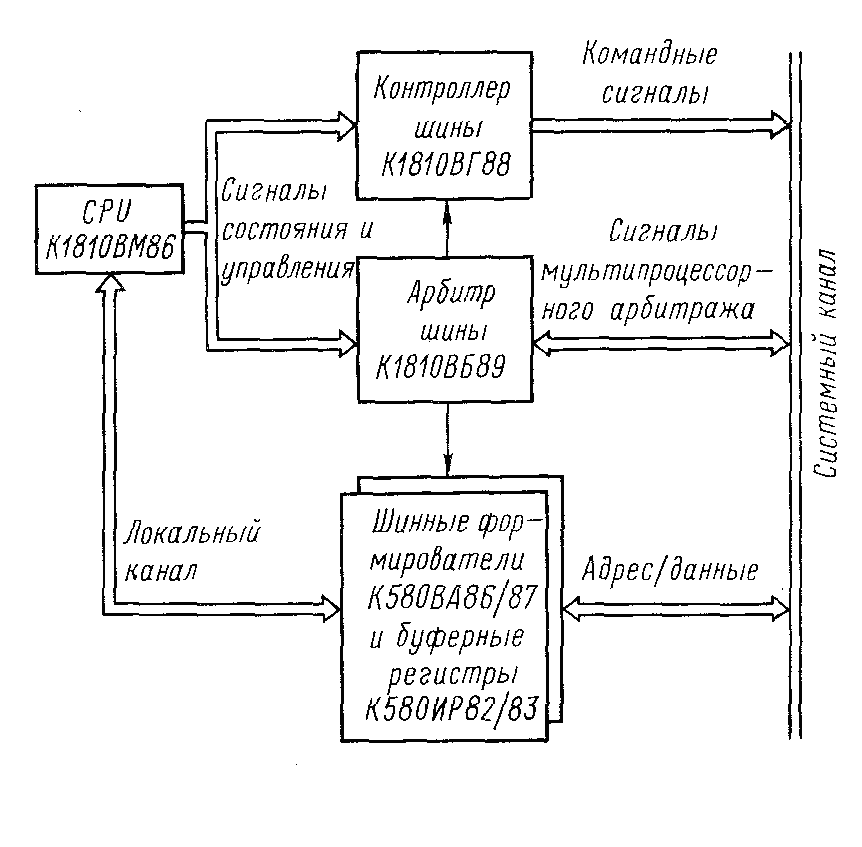

Рисунок 2.10 – Структурная схема микро ЭВМ на основе МП К1810ВМ86

Исходя из описания вышеперечисленных модулей, структурная схема микро ЭВМ на основе МП К1810ВМ86 на начальном этапе примет вид, представленный на рисунке 2.10.

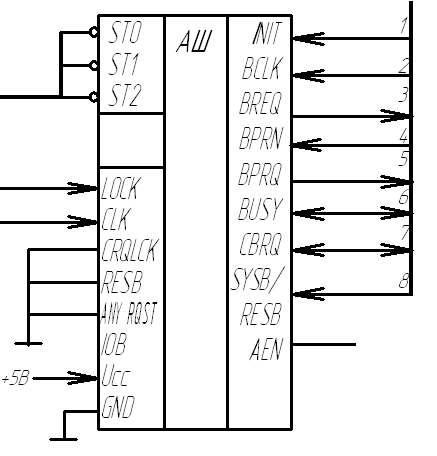

Схема подключения АШ к МП БИС показаны на рисунке 2.11

МП

К1810ВМ86

ШУ

КШ

К1810ВГ88

Рисунок 2.11 – Схема сопряжения арбитра шин К1810ВБ89 с микропроцессорным комплектом К1810

Для организации интерфейса микропроцессора К1810ВМ86 с системным каналом в мультипроцессорной системе арбитр шины К1810ВБ89 используется совместно с контроллером шины К1810ВГ88. Если микропроцессору не разрешается использование системного канала, то арбитр шины запрещает контроллеру шины, адресным регистрам и шинным формирователям доступ к каналу, устанавливая их выходы в высокоимпедансное состояние. Получив доступ к системному каналу, арбитр обеспечивает подключение к нему контроллера шин, адресных регистров и шинных формирователей.