- •Содержание

- •1 Расшифровка и анализ задания

- •2.1 Архитектура и режимы работы мп к1810вм86

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •2.8 Разработка обобщенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.1 Контроллер прямого доступа к памяти кр580вт57

- •4.1 Программируемый таймер кр580ви53

- •4.2 Программируемый контроллер прерываний кр580вн59

- •4.4 Разработка уточненной структурной схемы

- •5 Разработка алгоритма работы микропроцессорной системы

- •В ходе курсового проекта разработана управляющая система микро - эвм, реализующая заданные взаимодействия с объектом управления.

- •Блок-схема алгоритма работы устройства позволяет определить момент выдачи управляющего воздействия , заданной длительностью.

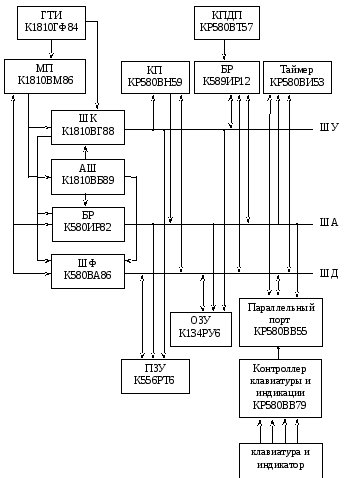

4.4 Разработка уточненной структурной схемы

Подключение устройств памяти и ввода/вывода к магистралям микро ЭВМ. В микропроцессорных системах, построенных на основе МП БИС К1810ВМ86, могут быть использованы 8–и 16–разрядные устройства ввода – вывода и 16–разрядные устройства памяти. С МП К1810ВМ88 используются только 8–разрядные устройства или 16-разрядные с применением специальной схемы преобразования разрядности магистрали.

На рисунке 4.7 изображена уточненная схема микро ЭВМ.

Рисунок 4.7 - Уточненная структурная схема микро ЭВМ

5 Разработка алгоритма работы микропроцессорной системы

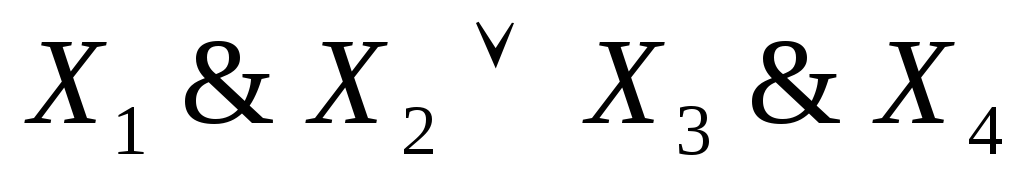

Обработка

информации от цифровых датчиков и выдача

управляющего воздействия y1

производится путем ввода значений x1,

x2,

x3,

x4

и вычисления булевой функции f1(x1,

x2,

x3,

x4)=

![]() .

.

При единичном значении f1 вырабатывается управляющий сигнал y1=1 длительностью t1=100 мкс.

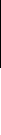

При обработке информации с аналоговых датчиков ПМ принимает коды NU1, NU2 с выходов АЦП и код константы К с регистра пульта управления. Далее вычисляется значение функции NU=f2(NU1,NU2, К)=max(NU1,NU2+К) и сравнивается с константой Q, хранящейся в ПЗУ. В зависимости от результатов сравнения вырабатывается (аналогично y1) один из двух двоичных управляющих сигналов y2 или y3 заданной длительности по следующему правилу: если NU<Q, то выдать y2 длительностью t2=80 мкс, иначе выдать y3 длительностью t3=80 мкс.

Далее формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 и производится вычисление по формуле:

![]()

Значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

Все двоичные переменные и константы, участвующие в вычислениях: NU1, NU2, NU3, К, Q, A0, A1, Y4 рассматриваются как целые без знака.

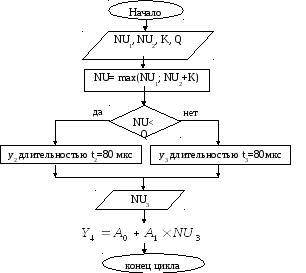

После выдачи всех управляющих воздействий проверяется состояние тумблера «СТОП» на пульте управления. Если СТОП=0, цикл управления начинается с начала, иначе выполняется процедура останова системы, включающая следующие действия: формируется сигнал установки системы в исходное состояние путем подачи на линию начальной установки интерфейса двух прямоугольных импульсов длительностью 30 мкс интервалом 30 мкс, выполняется команда процессора СТОП.

Блок-схема заданного цикла управления разбита на две части (рисунок 5.1 и 5.2), общая блок-схема представлена на рисунке 5.3.

![]()

нет

да

y1

длительностью

t1=100

мкс

Рисунок 5.1– Цикл 1 управляющей программы

В общем виде управляющая программа состоит из двух циклов, по результатам выполнения которых осуществляется выдача управляющих воздействий на индикацию. Управляющая программа выполняется до тех пор пока на пульте управления не будет включен тумблер «СТОП».

Цикл

1 управляющей программы заключается в

вводе в центральный процессор значений

сигналов из цифровых датчиков, вычислении

булевой функции

![]() .

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностью

t1=100

мкс. Если же управляющий сигнал принял

значение 0, то булева функция

.

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностью

t1=100

мкс. Если же управляющий сигнал принял

значение 0, то булева функция

![]() вновь повторяется.

вновь повторяется.

Цикл

2 управляющей программы заключается в

воде в центральный процессор двоичных

кодов с выходов АЦП и констант К и Q,

вычислении значения функции f2(NU1,

NU2,

К), по выражению NU=

max(NU1;

NU2+К).

Если по результатам вычисления получилось,

что NU<Q,

то вырабатывается управляющий сигнал

длительность t2=80

мкс, если же получилось что NU>Q,

то вырабатывается управляющий сигнал,

длительностью t3=80мкс.

Далее осуществляется ввод в центральный

процессор двоичного кода с выхода АЦП

NU3

и производиться вычисление функции

![]() .

.

Цикл 2 изображен на рисунке 5.2.

Рисунок 5.2 – Цикл 2 управляющей программы

Рисунок 5.3 – Общая блок-схема программы

Таблица истинности для определения управляющих воздействий приведена ниже:

Таблица 5.1 – Значения управляющих воздействий

-

X1

X2

X3

X4

Y=

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

1

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

1

1

1

0

0

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

6 РЕАЛИЗАЦИЯ СИСТЕМЫ ТЕСТОВОГО ПРОЦЕССОРА ДЛЯ МУЛЬТИПРОЦЕССОРНЫХ СИСТЕМ НА БАЗЕ МПК БИС К1810ВМ86

Одна из основных задач проектирования высоконадежных МПС – повышение уровня контроля пригодности процессоров – может быть решена введением в состав процессора аппаратно-программных средств контроля. Результаты вычислений могут сравниваться как с помощью специального диагностического процессора, так и самими процессорами диагностируемой структуры. В мультипроцессорных системах с распределенной магистралью – в процессе передачи по магистрали.

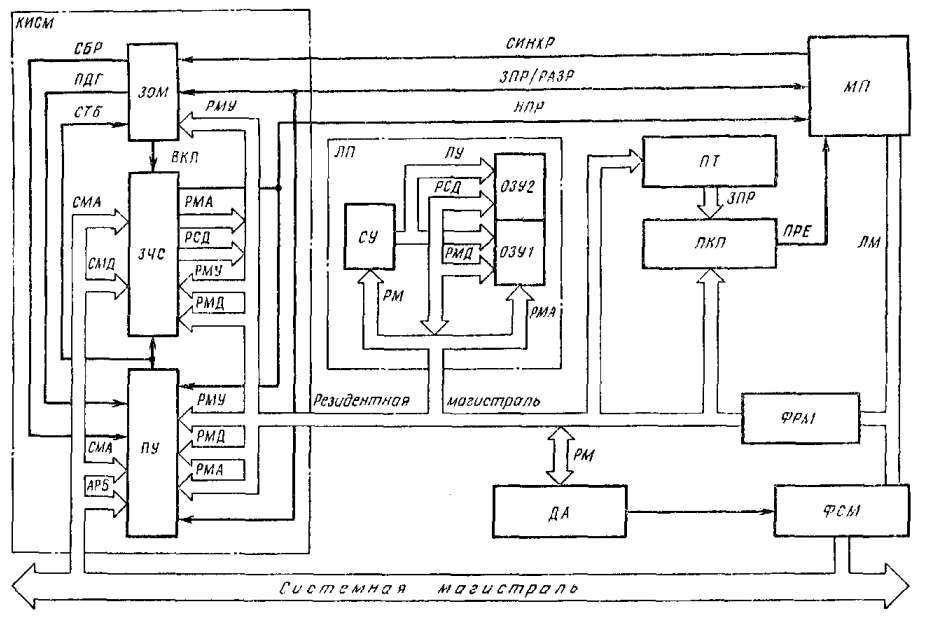

Рисунок 6.1 – Структурная схема тестового процессора на базе БИС К1810

На базе МП К БИС серии К1810 разработан процессор, обеспечивающий селективный контроль информации, передаваемой по распределенной магистрали (рисунок 6.1). Процессор содержит блоки микропроцессоров (МП); формирования системной магистрали (ФСМ); формирования резидентной магистрали (ФРМ); программируемого контроллера прерываний (ПКП); программируемого таймера (ПТ); локальной памяти (ЛП); дешифрации адреса (ДА) и контроля информации, передаваемой по системной магистрали (КИСМ).

Блоки МП, ФСМ и ФРМ объединены вокальной магистралью (ЛМ), блоки ПКП, ПТ, ЛП м ДА – резидентной магистралью (РМ).

КИСМ подключен к резидентной и системной магистралям (СМ) и является наряду с МП ведущим устройством РМ. Доступ ведущих устройств к РМ регулируется с помощью встроенных средств запроса-разрешения РМ МП К1810ВМ86.

Контроль информации, передаваемой по СМ, основан на записи в блок ЛП эталонной информации, программировании КИСМ на слежение за контролируемым пространством адресов и сравнении передаваемой информации с эталонной. При этом процессор использует 16–разрядную РМ данных и контролирует передачу по 8-разрядной СМ данных.

МП содержит микропроцессорные БИС, тактовый генератор и схему формирования сигналов готовности. ФСМ и ФРМ обеспечивают сопряжение МП с распределенной магистралью и резидентными ресурсами процессора. ДА формирует сигналы выбора блоков ЛП, ПКП, ПТ, КИСМ и управления работой блока ФСМ. В качестве ПКП и ПТ могут быть использованы БИС КМ1810ВН59А и КР580ВН53 соответственно.

Блок ЛП содержит два банка памяти ОЗУ1, ОЗУ2 и схему управления (СУ). Младший банк соединен с младшей половиной резидентной магистрали данных (РМД), старший банк со старшей половиной (РСД). Обращение к младшему банку происходит по четным адресам, к старшему по нечетным. Блок МП может одновременно обращаться к обоим банкам, и два байта данных воспринимаются как слово. КИСМ в одном шинном цикле считывает байт данных из младшего банка и записывает байт данных в старший.

В ЛП выделяется обменный сектор, размерность которого равна удвоенной размерности контролируемых по СМ секторов. Каждому байту контролируемого адресного пространства соответствует слово в обменном секторе. Младший байт слова используется для хранения эталонной информации, подлежащей передаче по СЛ1, старший байт для записи информации, переданной по СМ в контролируемый сектор.

Узел ПУ включает программно-доступные регистры номера контролируемого сектора (НКС) и фиксации магистрали арбитража (ФМЛ), схему разрешения-запрета контроля (РЗК) и схему управления (СУ1).

Рассмотрим работу процессора в составе мультипроцессорной системы с распределенной магистралью. В исходном состоянии работа КИСМ запрещена, а блок МП выполняет задания, не связанные с контролем информации, передаваемой по распределенной магистрали. Информационным признаком начала режима контроля является сигнал запроса прерывания (ЗПР), поступающий на блок ПКП. Источником ЗПР при периодическом контроле является блок ПТ или внешние устройства. По сигналу прерывания (ПРЕ) блок МП переходит к выполнению подпрограммы обслуживания прерывания. При этом он определяет номер контролируемого сектора и выделяет в ЛП обменный сектор, в который заносятся результаты вычислений. Размерность обменного сектора равна удвоенной размерности контролируемых по системной магистрали секторов.

ЗАКЛЮЧЕНИЕ