- •Содержание

- •1 Расшифровка и анализ задания

- •2.1 Архитектура и режимы работы мп к1810вм86

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •2.8 Разработка обобщенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.1 Контроллер прямого доступа к памяти кр580вт57

- •4.1 Программируемый таймер кр580ви53

- •4.2 Программируемый контроллер прерываний кр580вн59

- •4.4 Разработка уточненной структурной схемы

- •5 Разработка алгоритма работы микропроцессорной системы

- •В ходе курсового проекта разработана управляющая система микро - эвм, реализующая заданные взаимодействия с объектом управления.

- •Блок-схема алгоритма работы устройства позволяет определить момент выдачи управляющего воздействия , заданной длительностью.

2.3 Буферный регистр кр580ир82

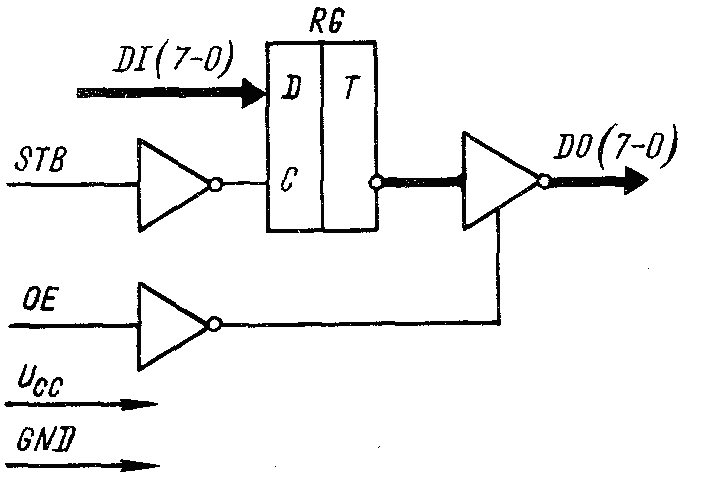

Буферный регистр КР580ИР82 представляет собой 8-разрядные параллельные регистр с тристабильными выходами. Он используется для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорных системах на базе МП К580ИК80А и К1810ВМ86. Назначение входных и выходных сигналов указано при описании выводов микросхем в таблице 2.5.

Таблица 2.5 – Описание выводов буферного регистра КР580ИР82

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

DI(7 - 0) |

ДИ(7-0) |

Входы данных |

Входы |

H-1, L-0 |

|

STB |

строб |

Вход сигнала стробирования |

Вход |

H-1, L-0 |

|

|

РВ |

Вход сигнала разрешения ввода |

Вход |

L -1, H -0 |

|

DO(7 - 0) |

ДО(7-0) |

Выходы данных |

Выходы |

H-1, L-0 |

|

UСС |

Uп |

Напряжение питания ( + 5 В) |

Вход |

|

|

GND |

ОБЩ |

Напряжение питания (0 В) |

Вход |

|

Структурная схема буферного регистра приведена на рисунке 2.5.

Рисунок 2.5 – Структурная схема буферного регистра КР580ИР82

Основные электрические параметры микросхемы КР580ИР82 следующие:

Выходное напряжение логического нуля UOL, В < 0,5

Выходное напряжение логической единицы UOH, В > 2,4

Входное напряжение логического нуля UIL, В < 0,8

Входное напряжение логической единицы UIH, В > 2,0

Ток потребления от источника питания IСС, мА < 160

Выходной ток утечки IOZ, мкА < 50

Время задержки tIO, с инвертированием < 40

без инвертирования < 45

2.4 Шинный формирователь кр580ва86

Шинный формирователь КР580ВА86 представляет 8-разрядные параллельный приемопередатчик с тристабильными выходами.

Структурная схема шинного формирователя представлена на рисунке 2.6.

Рисунок 2.6 – Структурная схема шинного формирователя КР580ВА86

Он используется для реализации различных буферных схем в микропроцессорных системах на базе МП К580ИК80А и К1810ВМ86. На выходах микросхемы КР580ВА86 генерируются неинвертированные выходные данные.

Назначение входных и выходных сигналов указано при описании выводов микросхем в таблице 2.6.

Таблица 2.6 – Описание выводов шинного формирователя КР580ВА86

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

А(7-0) |

А(7-0) |

Выводы данных для локальной шины МП |

Выход |

H-1, L-0 |

|

1 |

2 |

3 |

4 |

5 |

|

Продолжение таблицы 2.6 |

||||

|

1 |

2 |

3 |

4 |

5 |

|

В(7-0) |

В(7-0) |

Выводы данных для системной шины |

Выход |

H-1, L-0 |

|

Т |

управления |

Вход управления направлением передачи |

Вход |

H-1, L-0 |

|

ОЕ |

разрешения |

Вход разрешения передачи |

Вход |

H-1, L-0 |

|

UСС |

Uп |

Напряжение питания ( + 5 В) |

Вход |

|

|

GND |

ОБЩ |

Напряжение питания (0 В) |

Вход |

|

Основные электрические параметры микросхемы К58ОВА86 следующие:

Выходное напряжение логического нуля UOL, В:

для А-выводов < 0,5

для В-выводов < 0,5

Выходное напряжение логической единицы UOH, В:

для А-выводов > 2,4

для В-выводов > 2,4

Ток потребления от источника питания IСС, мА <135

Время задержки tIO:

– с инвертированием <30

– без инвертирования <35