- •Введение

- •Расшифровка и анализ задания

- •2.3 Генератор тактовых импульсов

- •2.4 Буферные регистры

- •2.5 Шинные формирователи

- •2.6 Контроллер шин к1810вг88

- •2.7 Арбитр шин к1810вб89

- •2.10.2 Формирование магистралей адреса, данных и управления

- •4.3 Разработка контроллера прямого доступа к памяти

- •16К/64к – вход выбора режима. Сигнал высокого уровня на этом входе задает режим работы кдп с озу емкостью 16к слов, а сигнал низкого уровня – режим работы с озу емкостью 64к.

- •6 Организация управления мпс

- •6.1 Сопряжение с клавиатурой

- •6.2 Сопряжение с дисплеем

- •7 Построение мпс

2.7 Арбитр шин к1810вб89

Арбитр шины К1810ВБ89 предназначен для использования в мультипроцессорных системах на основе микропроцессора К1810ВМ86. Арбитр шины координирует работу различных компонентов мультипроцессорной системы, а также обеспечивает совместимость микропроцессора К1810ВМ86 со стандартным интерфейсом MULTIBUS.

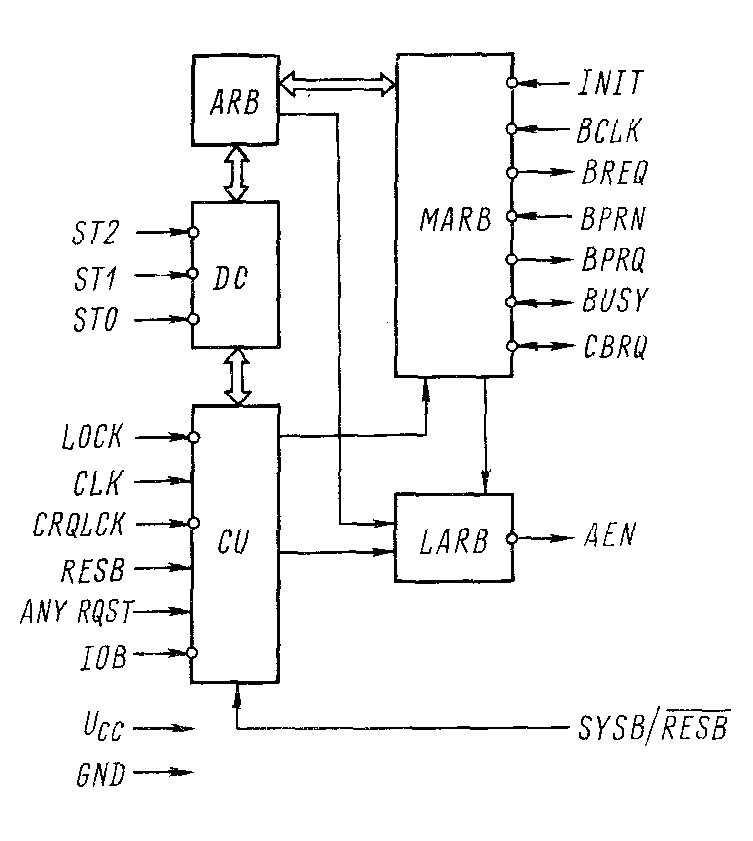

Рисунок 12 - Структурная схема арбитра шин

Структурная схема арбитра шины приведена на рисунке 12. В состав входят: схема арбитража (АRB); дешифратор состояния (DС); схема управления (СU); интерфейс с MULTIBAS (МАRВ); интерфейс с локальным каналом (LАRВ).

Назначения входных и выходных сигналов арбитра шины приведены при описании выводов микросхемы в таблице 8.

Таблица 8 - Описание выводов арбитра шин

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

ST(2 - 0) |

1; 19; 18 |

Входы сигналов состояния МП |

|

LOCK |

16 |

Вход сигнала блокировки от МП |

|

CLK |

17 |

Вход сигнала синхронизации |

|

GND |

10 |

Напряжение питания (0 В) |

|

CRQLCK |

15 |

Вход сигнала блокировки общего запроса; L-уровень сигнала запрещает арбитру шины передавать управление каналом системы другому арбитру |

Продолжение таблицы 8

|

1 |

2 |

3 |

|

|

3 |

Вход сигнала, используемого в режиме локального канала; |

|

RESB |

4 |

Вход

сигнала переключения в режим резидентного

(локального)

канала; при H-уровне

сигнала возможен переход к управлению

мультипроцессорным системным каналом

в зависимости от

состояния сигнала на входе

|

|

ANYRQST |

14 |

Вход сигнала переключения в режим передачи управления по любому запросу, позволяющего передавать управление системным каналом арбитру шины с более низким приоритетом |

|

IOB |

2 |

Вход сигнала переключения в режим канала ввода/вывода, позволяющего арбитру шины работать в системах, имеющих как канал ввода/вывода, так и мультипроцессорный системный канал |

|

BPRQ

|

8 |

Выход сигнала приоритетного разрешения канала, используемого в системе с последовательным приоритетом. (Сигнал BPRQ на вход BPRN последующего арбитра с более низким приоритетом) |

|

BUSY |

11 |

Вывод двунаправленного сигнала занятости системного канала. (Арбитр, захвативший управление каналом, выставляет сигнал BUSY L-уровня, запрещающий другим арбитрам использование канала) |

|

CBRQ |

12 |

Вывод двунаправленного сигнала общего запроса шины, указывающего арбитру шины на запросы управления системным каналом со стороны других арбитров с более низким приоритетом. (Арбитр, работающий в текущем цикле канала, не выставляет сигнал на вывод CBRQ) |

|

AEN |

13 |

Выход сигнала разрешения адреса |

|

Ucc |

20 |

Напряжение питания ( + 5 В) |

Основные электрические параметры микросхемы К181ОВБ89:

Входное напряжение логического нуля UIL, В 0,8.

Входное напряжение логической единицы UIH, В 2,0.

Выходное напряжение логического нуля UOL, В 0,45.

Выходное напряжение логической единицы UOH, В 2,4.

Ток потребления источника питания ICC, мА 165.

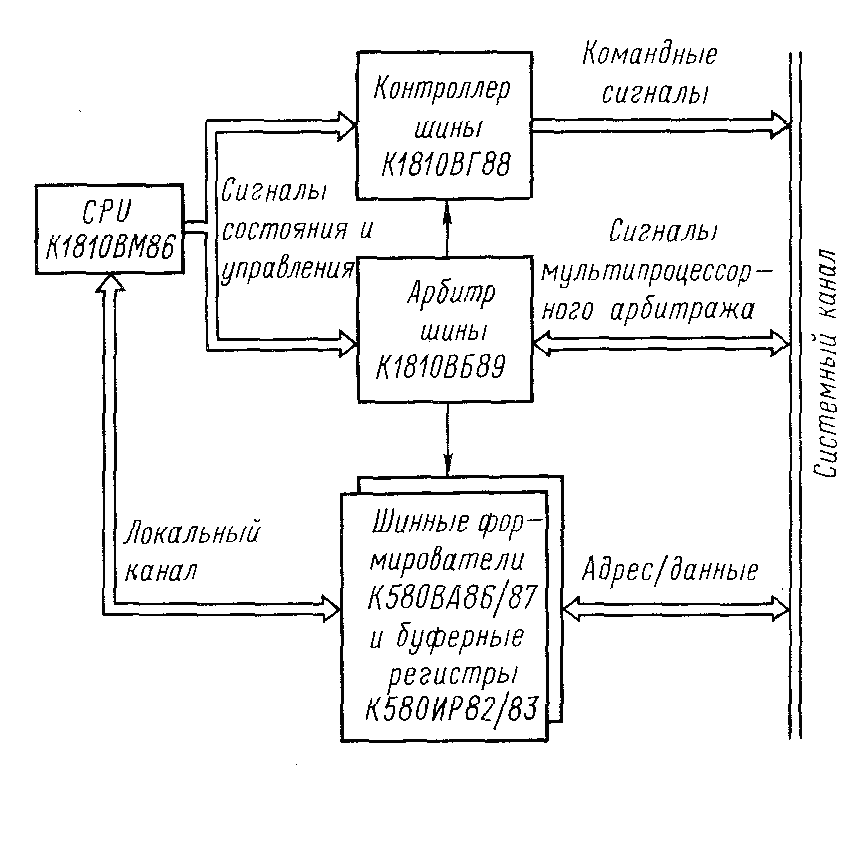

Рисунок 13 - Структурная схема микроЭВМ на основе МП К1810ВМ86

Исходя из описания вышеперечисленных модулей, структурная схема микроЭВМ на основе МП К1810ВМ86 на начальном этапе примет вид, представленный на рисунке 13.

Для организации интерфейса микропроцессора К1810ВМ86 с системным каналом в мультипроцессорной системе арбитр шины К1810ВБ89 используется совместно с контроллером шины К1810ВГ88. Если микропроцессору не разрешается использование системного канала, то арбитр шины запрещает контроллеру шины, адресным регистрам и шинным формирователям доступ к каналу, устанавливая их выходы в высокоимпедансное состояние. Микропроцессор переходит в состояние ожидания и остается в нем до получения сигнала разрешения (по входу RDY) от арбитра. Получив доступ к системному каналу, арбитр обеспечивает подключение к нему контроллера шин, адресных регистров и шинных формирователей. Таким образом, арбитр шины осуществляет мультиплексирование микропроцессоров на системном канале и устраняет конфликты при получении доступа к каналу.

2.8 АЦП К589ПВ2

В схему разрабатываемой системы входит АЦП К589ПВ2, который представляет собой 12-разрядный преобразователь напряжения в двоичный код сравнительно низкого быстродействия. С точки зрения процессора, АЦП представляет собой 16-разрядный порт.

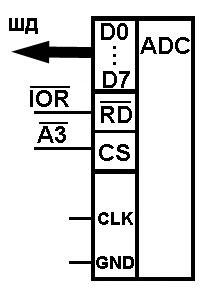

Схема подключения АЦП к МП приведена на рисунке 14.

Рисунок 14 - Подключение АЦП к ВМ86

D0-D7 – линии шины данных, подключаются непосредственно к шине данных,

![]() -

управляющий сигнал считывания,

вырабатывающийся элементами И-НЕ на

выходе МП.

-

управляющий сигнал считывания,

вырабатывающийся элементами И-НЕ на

выходе МП.

CLK – управляющий сигнал неперекрывающихся синхроимпульсов от МП.

GND – общий вывод.

2.9 Программируемый таймер К1810ВИ54

Программируемый таймер (ПТ) К1810ВИ54 предназначен для генерации времязадающих функций, программно-управляемых временных задержек с возможностью программного контроля их выполнения. Программируемые таймеры применяются в МПС, выполненных на базе МПК БИС К580, К1810, К1821, используемых в задачах управления и измерения в реальном масштабе времени с тактовой частотой до 8 МГц. Конструктивно эти ПТ совместимы с ПТ типа К580ВИ53, отличаются от них повышенным быстродействием и расширенными функциональными возможностями.

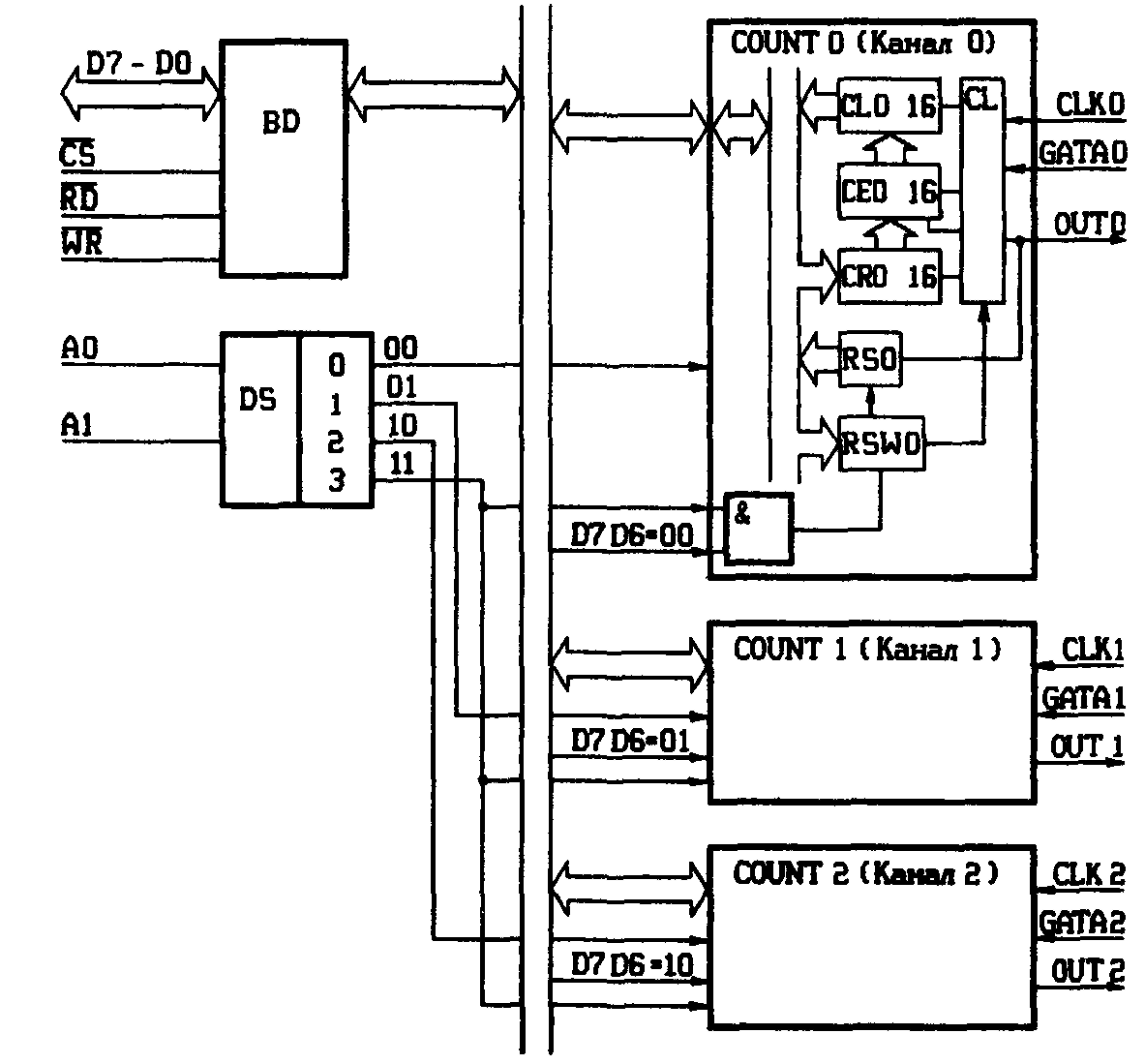

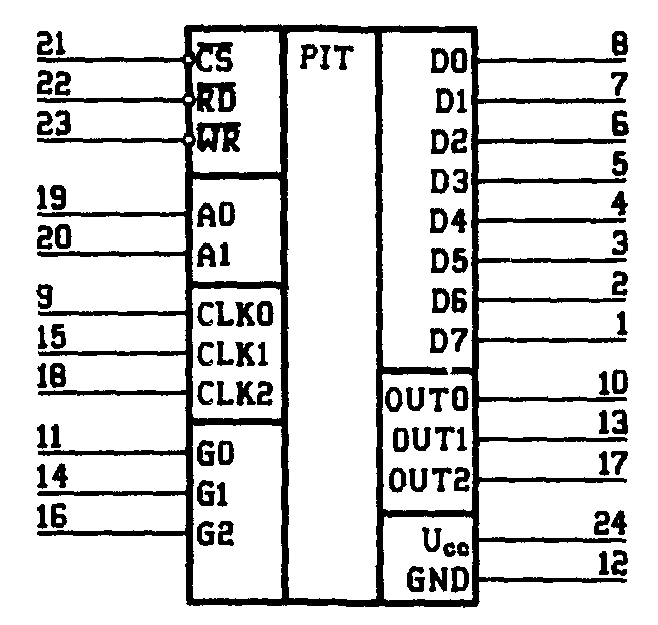

Рисунок 15 - Структура схема ПТ К1810ВИ54

Программируемый таймер К1810ВИ54 включает три независимых канала, каждый из которых может быть запрограммирован на работу в одном из шести режимов для двоичного или двоично-десятичного счета. Структурная схема ПТ показана на рисунке 15, его условное графическое обозначение – на рисунке 16.

Рисунок 16 - Условно-графическое обозначение ПТ К1810ВИ54

Таблица 9 - Назначение выводов ПТ К1810ВИ54

|

Обозначение вывода |

Назначение |

|

|

Сигнал управляет входным буфером BD.

При

|

|

|

Сигнал

|

|

|

Сигнал

|

|

А0, А1 – адресные входы |

По ним осуществляется адресация к одному из каналов: А0=А1=00 – адрес канала 0; А0=А1=01 – адрес канала 1; А0=А1=10 – адрес канала 2; А0=А1=11 – признак загрузки управляющего слова или команд. |

|

CLK2–CLK0 – входы тактовых сигналов для управления счетчиком/таймером |

Срез сигнала на входе CLK приводит к уменьшению содержимого счетчика/таймера СЕ на единицу. |

|

GATA2–GATA0 – входы разрешения счета. |

При GATA=l разрешается выполнение функций; для некоторых режимов работы разрешается поступление тактовых сигналов на вход счетчика/таймера, для других (импульсный генератор и генератор меандра) открывается выходной буфер OUT. |

|

OUT2–OUT0 – выходы счетчика/таймера. |

|

2.10 Разработка уточненной структурной схемы

Микропроцессорный комплект серии К1810 включает в себя 8- и 16-разрядные МП, позволяющие производить высокоскоростные вычисления и обмен данными; устройства формирования магистралей и арбитража многопроцессорных взаимодействий и универсальные интерфейсные БИС, предназначенные для выполнения широкого набора функций ускоренной передачи информации, счета временных интервалов и обработки прерываний от УВВ

В составе микроЭВМ, построенной на основе МПК серии К1810, можно использовать все интерфейсные БИС 8-разряд-ного МПК серии КР580.

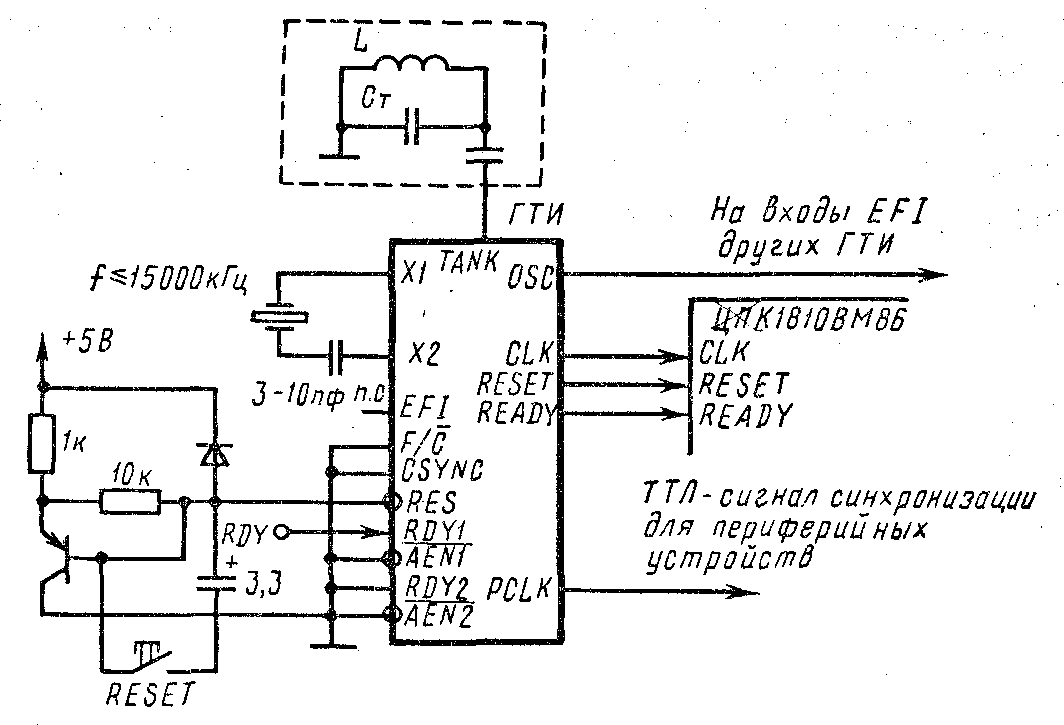

2.10.1 Синхронизация работы МП БИС К1810ВМ86.

Для синхронизации работы МП БИС используется микросхема тактового генератора 1810ГФ84. Схема подключения тактового генератора к МП БИС показаны на рисунке 17.

Основной сигнал синхронизации МП частотой до 5 МГц формируется делением на 3 опорной частоты ОSС кварцевого генератора (вход F/С = 0) или внешнего задающего сигнала, подключенного ко входу ЕР1 (вход F/С = 1), что позволяет использовать один кварцевый резонатор для задания частоты нескольким тактовым генераторам. Их полную синхронизацию можно обеспечить одновременной подачей внешнего сигнала синхронизации СSYNC на вход микросхем КР1810ГФ84.

Рисунок 17 - Схема подключения тактового генератора к МП БИС

Кварцевый резонатор можно возбудить и на более высокой гармонике, для чего ко входу ТANК через разделительный конденсатор подключается LС-контур, настроенный на частоту верхней гармоники генератора.

Сигнал синхронизации периферийного оборудования РСLК для работы с более медленными УВВ вырабатывается путем деления частоты тактового сигнала СLК на 2.

Микросхема К1810ГФ84 вырабатывает также сигнал RESET начальной установки и стробирует внешние сигналы готовности периферийного оборудования READY.

Наличие двух сигналов

готовности RDY1,

RDY2

и разрешения

![]() ;

;

![]() необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.

необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.