- •Основи автоматики

- •Луцьк - 2007 Вступ

- •Цифрові електронно-обчислювальні машини

- •Інформація

- •Електронні ключі

- •Діодні ключи

- •Оптоелектроні прилади. Фотодіоди, фото транзистори, світло діоди, оптрони. Оптоелектроні ключі і схеми гальванічної розв’язки кіл.

- •Фотодіоди

- •Лавинні фотодіоди

- •Фототранзистори

- •Елементи алгебри і логіки.

- •Системи (серії) логічних елементів. Базові елементи інтегральних схем виду ттл і кмон

- •Вивчення тригерів. Їх схемотехнічна реалізація

- •Тригером називається пристрій, що може знаходитися у двох станах стійкої рівноваги й здатний стрибком переходити з одного стану в інший під впливом зовнішнього сигналу керування.

- •Генератори і формувачі імпульсів на логічних елементах (мультивібратори і схеми усунення деренчання контактних датчиків інформації).

- •Регістри (послідовні, паралельні, універсальні). Їх використання в якості запам’ятовуючих пристроїв та перетворювачів інформації.

- •Лічильники (двійкові, з довільним коефіцієнтом рахунку, реверсні, з попередвстановленням). Подання вихідної інформації в позиціонному, двійковиму і двійково-десятковому коді

- •Його часові діаграми та схематичне позначення

- •Перетворювачі кодів шифратори і дешифратори. Мультиплексори, демультиплексори.

- •Суматори. Однорозрядний двійковий суматор. Багаторозрядні війкові суматори паралельного типу.

- •Споживана мікросхемою пам’яті потужність зазвичай вказується, виходячи із розрахунку на 1 біт.

- •Режим зберігання - забезпечується надходженням 0 по адресній шині рядка, при цьому транзистор vt5 закривається й ізолює тригер від розрядної шини.

- •Зовнішні запам’ятовуючі пристрої

- •В радіальних інтерфейсах використовуються індивідуальні для кожного пп лінії, по яких відбувається передача тільки між цим пп і центральним пристроєм (цп).

- •Зовнішні пристрої введення (клавіатура, фото стрічка). Візуалізація інформації (дисплей, друкувальний пристрій).

- •Характеристики мікропроцесорів.

- •Структура мікропроцесора

- •Системи автоматичного контролю, регулювання, керування.

- •Цифро-аналогові та аналого-цифрові перетворювачі.

- •Цифро-аналогові перетворювачі

- •Аналогово-цифрові перетворювачі

- •Перетворювачі інформації в електричний сигнал в приладах автоматики. Фото-, тензо- і терморезистори. Ємнісні і індуктивні перетворювачі.

- •Виконуючі та індикаторні пристрої в автоматичних системах

- •Автоматика в школі. Шкільний кабінет обчислювальної техніки. Вимоги до навчальної обчислювальної техніки та її програмного забезпечення.

- •Обладнання робочого місця учня.

- •Обладнання мережного забезпечення

- •Електронні ключі………………………………………………………………………………….

- •Вивчення тригерів.Їх схемотехнічна реалізація………………………………………………………………….

- •Регістри (послідовні, паралельні, універсальні).Їх використання в якості запам’ятовуючих пристроїв та перетворювачів інформації…………………………………….

- •Виконуючі та індикаторні пристрої в автоматичних системах………………………………………………………..

- •Література………………………………………………………..…..

- •Додаток 1. Функціональна класифікація імс

- •Додаток 2. Елементи цифрової електроніки та їх зарубіжні аналоги

Елементи алгебри і логіки.

Схематична реалізація основних логічних функцій.

Системи (серії) логічних елементів. Базові елементи інтегральних схем виду ттл і кмон

ЛЕ разом із ЗЕ складають основу пристроів цифрової (дискретної) обробки інформації – обчислювальних машин, цифрових вимірю-вальних приладів і пристроїв автоматики. ЛЕ виконують найпростіші логічні операції (ЛО) над цифровою інформацією, а ЗЕ викорис-товуються для її зберігання.

ЛО перетворює за відповідними законами вхідну інформацію у вихідну. ЛЕ частіше всього будують на базі електронних пристроїв, працюючих в ключовому режимі. При цьому цифрову інформацію завжди подають у двійковій формі, в якій сигнали приймають тільки 2 значення: „0” (логічний нуль) і „1” (логічна одиниця), що відповідає двом положенням ключа.

Логічні перетворення двійкових сигналів складаються з трьох елементарних операцій:

1) логічне додавання (дезюнкція), операція АБО, яка позначається знаками „+” або v (vel – або):

F = x1 + x2 + x3 +…+ xn;

2) логічне множення (кон’юнкція), або операція І, яка позначається знаками „.”, чи написанням змінних без знаків множення:

F = x1x2x3…xn;

3) логічне заперечення (інверсія) або операція НЕ, яка позначається рискою над змінною:

__

F = x.

Правила виконання ЛО над двійковими числами для випадку двох змінних мають наступний вигляд:

Таблиця 6

-

Операція АБО

0+0=0

0+1=1

1+0=1

1+1=1

Операція І

0*0=0

0*1=0

1*0=0

1*1=1

Операція НЕ

Самостійне значення має логічна операція ЗАБОРОНА, яка символічно записується у вигляді:

____

![]()

ЛО, що реалізують операцію АБО, називають елементами АБО і позначають на функціональних схемах, як показано на рис. 17а.

Вихідний сигнал F елемента АБО дорівнює одиниці, якщо хоча б на один із n входів подано сигнал “1”.

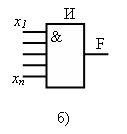

Рис. 33. Позначення логічних елементів

ЛЕ, що реалізують операцію І, називають елементами І або схемами співпадання і позначають, як подано на рис. 17,б. Вихідний сигнал F елемента І дорівнює одиниці, якщо одночасно на всі n входів надходить сигнал “1”.

Операція НЕ реалізується ЛЕ НЕ або інвертором, позначення якого подано на рис. 17,в.

ЛЕ

ЗАБОРОНА

має в найпростішому випадку лише два

входи: дозволяючий (вхід Х![]() )

і забороняючий (вхід Х

)

і забороняючий (вхід Х![]() ).

Вихідний сигнал повторює сигнал на

дозволеному вході Х

).

Вихідний сигнал повторює сигнал на

дозволеному вході Х![]() ,

якщо Х

,

якщо Х![]() =0.

При Х

=0.

При Х![]() =1

на виході виникає сигнал “0” незалежно

від значення Х

=1

на виході виникає сигнал “0” незалежно

від значення Х![]() .

Стандартні умови позначення елемента

ЗАБОРОНА

наведено на рис. 17,г.

.

Стандартні умови позначення елемента

ЗАБОРОНА

наведено на рис. 17,г.

Крім розглянутих ЛЕ на практиці широко використовують комбіновані елементи, які реалізують дві (або більше) ЛО, наприклад, елементи І-НЕ (рис. 1д) АБО-НЕ (рис. 17,е). Перший з них виконує

____________ _____________

операцію

F=x![]() x

x![]() x

x![]() … x

… x![]() ,

а другий

- операцію

F=x

,

а другий

- операцію

F=x![]() +x

+x![]() +…+х

+…+х![]() ,.

,.

ЛО майже завжди виконують на інтегральних мікросхемах.

***

Найпростіші ЛО І чи АБО можуть бути побудовані на основі діодних ключів. В якості елемента НЕ часто використовується транзисторний ключ, оскільки він має інвертуруючі властивості.

На рис. 18 наведена схема елемента із діодних ключів, які можуть бути використані в якості ЛЕ АБО чи І в залежності від увімкнення та кодування сигналів.

Рис. 34. ЛЕ із діодних ключів

При увімкненні за схемою рис. 19,а, елемент із діодних ключів служить елементом АБО, якщо кодування сигналів відповідає рис. 19б.

Рис. 35. ЛЕ АБО Рис. 36. ЛЕ І

Звичайно,

при надходженні сигналу “1”, (- Е

) хоча б на один вхід (наприклад, х![]() =1),

відкривається відповідний діод (VD1)

і вхід з’єднується з виходом (F=1).

Всі інші діоди закриті, таким чином,

вихідний сигнал не попадає на виходи,

на яких Uвх

=0.

=1),

відкривається відповідний діод (VD1)

і вхід з’єднується з виходом (F=1).

Всі інші діоди закриті, таким чином,

вихідний сигнал не попадає на виходи,

на яких Uвх

=0.

Для отримання ЛЕ І діоди вмикають за схемою рис. 20,а, якщо кодування сигналу відповідає рис. 20,б.

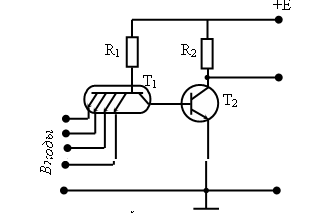

Рис.37. ЛЕ І-НЕ ДТЛ Рис. 38. ЛЕ І-НЕ ТТЛ

Дійсно, при сигналі “0” на всіх виходах всі діоди відкриті, в них і в резисторі R з’являються струми, що створюється джерелом е.р.с. Е1, які замикаються через джерела сигналів, під’єднаних до всіх входів. Оскільки опір резистора R значно більший прямого опору діода, напруга на ньому приблизно рівна E, а напруга на виході виявляється близькою до нуля.

Якщо напруга на одному із входів відповідає логічній одиниці

(E > E1), то відповідний діод закривається, однак решта діодів відкриті і на виході як і раніше залишається сигнал „0”.

Сигнал „1” з’явиться на виході тільки тоді, коли на всі входи буде діяти сигнал „І”, всі діоди виявляться закритими, струм через резистор буде дорівнюватиме нулю і Uвих = E1.

Щоб одержати логічний елемент І-НЕ, до елемента по схемі рис. 18 добавляють інвертор на транзисторі (рис. 21).Операція І відбувається діодною частиною схеми (VD1-VD4, R1), а транзисторний каскад з загальним емітером служать інвертором. Для зв’язку логічного елемента І з інвертором служать послідовно увімкнуті діоди VD5,VD6, забезпечуючи надійне закриття транзистора при невисокому, але позитивному потенціалі точки А, що відповідає логічному „0” елемента І. Потенціал бази транзистора в цьому випадку нище потенціалу точки А на суму прямих напружених діодів VD5,VD6 і достатній для закривання транзистора. Мікросхема здійснює операцію І-НЕ при кодуванні, показаному на рис. 20б.

Дійсно, при сигналі „0” на всіх входах всі діоди відкриті, потенціал точки А близький до нуля. Транзистор закритий, на виході потенціал близький до +Е (сигнал ”І” ). Потенціал точки А і вихідний сигнал не змінюється до того моменту, поки на всі входи не буде поданий сигнал „І”. Тоді діоди VD1-VD4 закриються, потенціал точки А збільшиться, транзистор перейде в режим насичення, а на виході потенціал понизиться до значення „0”.

Рис. 39. ЛЕ із складним інвертором

Елемент І-НЕ за схемою рис. 23 відноситься до так названих ДТЛ- елементів (діодно-транзисторна логіка). Сучасні ЛО виконують у вигляді інтегральних мікросхем і входять в склад серій мікросхем -сукупностей типів мікросхем які можуть виконувати різні функції, мають однакове конструктивно-технічне виконання, призначені для сумісного використання. Наприклад, на основі схеми рис. 21 побудовані елементи І-НЕ серії 156 ДТЛ-типа. Так, мікросхема ІЛБ566А надає собою потужний елемент 4І-НЕ і відрізняється від схеми на рис. 23 більш складним інвертором (на чотирьох транзисторах) і відсутністю діодів VD5, VD6.

Більш високу швидкість порівняно з ДТЛ- елементами мають ТТЛ- елементи (транзисторно-транзисторна логіка).

Рис.40. Схема МОН-елемента АБО-НЕ

На рис. 22 показана схема ТТЛ-елемента І-НЕ з простим інвертором. Операція І реалізується тут багатоемітерним транзистором VT1, а транзистор VT2 служить в якості інвертора. Багатоемітерні транзистори легко реалізуються в інтегральній технології й служать основною ТТЛ елементів.

Коли на всіх виводах (емітерах транзисторах VT1) діє сигнал „1”

(високий потенціал), то всі переходи емітер база транзистора VT1 закриті. Потенціал бази транзистора VT2 близькі до 0, а перехід колектор–база транзистора VT1 відкритий прикладеною в прямому напрямку напругою джерела +Е. Струм колекторного переходу транзистора VT1 проходить через перехід емітер-база транзистора VT2, переводячи його в режим насичення, а на виході появляється сигнал „0” (низький потенціал). Коли на одному із входів появиться сигнал „0”, то відповідний перехід емітер-база транзистора VT1 відкриється і його базовий струм перекинеться із колекторного кола в емітерне. В результаті транзистор VT2 закриється і на виході з’явиться високий потенціал („1”). Таким чином, сигнал „0” може бути на виході тільки при сигналі „1” на всіх входах, що відповідає операції І – НЕ.

На практиці використовують ТТЛ–елементи зі складним інвертором, що дозволяє збільшити навантажувальну здатність елемента.

Рис. 41. Схема інвертора типа КМОН Рис. 42. Схема ЛЕ на комплементарних

парах (КМОН) транзисторів

На рис. 23 подана схема такого елемента І–НЕ. Транзистор VT3 виконує функцію емітерного повторювача з навантаженням у вигляді транзистора VT4. При дії сигналу „1” на всі входи транзистора VT2 насичений, як вказано раніше. Відповідно транзистор VT4 теж насичений через високий потенціал на його вході (точка а), створюючи емітер ним струмом транзистора VT2 на резистори R3. Завдяки низькому потенціалу колектора транзистор VT2 (точка б) транзистор VT3 закритий. При впливі сигналу “0” хоча б на один з входів транзистор VT2 закривається, транзистор VT3 відкривається з-за збільшенню потенціалу точки б і працює як емітерний повторював діод VD служить для забезпечення режиму зміщення транзистора VT3, т. е. для того, щоб цей транзистор був закритий при насиченому транзисторі VT2. пряма напруга на діоді VD складають близько 0,5 В і служить для запирання транзистора VT3 ця напруга створюється навіть при дуже малих (порядка мікроампер) струмів закритого транзистора VT3

За схемою рис. 24 побудований елемент І-НЕ ІЛБЗ44 серії І34. Незначно відрізняються схеми елементів І-НЕ розповсюджених серій 133 і 155.

***

ЛЕ на МОН – транзисторах мають малу потужність споживання й більший вхідний опір. На рис. 24 наведена схема МОН-елемента АБО-НЕ, виконаного на транзисторах з каналом n–типу. Тут транзистор VT4 виконує роль навантажувального резистора, увімкнутого у загальне стокове коло транзисторів VT1, VT2., VT3. При сигналі “0” (низький рівень) на входах всі транзистори закриті й на вході діє сигнал “1” (потенціал + Е). Якщо хоча б на одному із входів діє сигнал “1”, відповідний транзистор переходить в режим насичення й на виході з’являється “0”.

Ще більш економічні логічні КМОН-елементи (тут К-початкова літера в слові “комплементарний”–“доповнюючий”). В них використовуються пари КМОН транзисторів з каналами різних типів (p і n), увімкнутих послідовно з блоком живлення. При цьому затвори парних (комплементарних) транзисторів об’єднуються. В результаті при будь-якому вхідному сигналі (“0” або “1”) один з транзисторів відкритий, а другий закритий і напруга від джерела не відбирається. Струм споживається тільки в момент перемикання, чим й досягається висока економічність.

На рис. 25 подана схема інвертора типа КМОН.

При Uвх. =0 (“0”) відкритий р-канальний МОН-транзистор VT2, n-канальний транзистор VT1 закритий, а Uвих..=E (“1”). Коли Uвх.=Е, транзистор VT2 закритий, а транзистор VT1 відкритий і Uвих=0.

На рис. 26 подана схема КМОН-елемента АБО-НЕ, що складається з двох пар транзисторів: VT1 i VT’1, VT2 i VT’2. При U1=U2=0 n-канальні транзистори VT1,VT2 закриті, а р-канальні транзистори VT’1,VT’2 відкриті й Uвих=Е (“1”). Якщо U1=E, а U2=0, то транзистор VT1 відкритий, транзистор VT’1 закритий, транзистор VT2 закритий, транзістор VT2 відкритий і Uвих=0, тобто схема реалізує операцію АБО-НЕ. За схемою рис. 26 побудований, наприклад, елемент 4АБО-НЕ К176ЛЕ5 серії 176.

КМОН-елементи складаються тільки із МОН-транзисторів, що робить їх дуже технологічними, оскільки вони широко використовуються в великих інтегральних схемах (ВІС). Напруга джерела КМОН-елементів може бути встановлена будь-якою в межах від 3 до 15 В. Недолік КМОН-елементів (так як і МОН-елементів) - порівняльно невелика швидкодія.

Крім розглянутих існують логічні елементи іншіх типів, наприклад ЕЗЛ (еміттерно-зв’язана логіка) І2Л (інтегрально-інжекційна логіка), що мають високу швидкодію.

До основних параметрів ЛЕ відносяться:

-

напруга живлення,

-

потужність споживаної енергії,

-

час затримки розповсюдження – параметр, що визначає швидкодію елемента. Він дорівнює часу затримки перепада напруги при проходженні через елемент,

-

коефіцієнт розгалуження на виході – параметр, рівний числу одиничних навантажень, які можна одночасно під’єднати до виходу. Він визначає навантажувальну здатність логічного елемента,

-

коефіцієнт об’єднання на вході, рівний числу входів, по яких реалізується логічна функція.

Найбільше розповсюдження отримали логічні ТТЛ-, ЕЗЛ- і КМОН-елементи. Технологія -МОН і I2Л використовується тільки у ВІС.

***