- •А.Л. Ахтулов, л.Н. Ахтулова, с.И. Смирнов основы микропроцессорной техники

- •Содержание

- •Глава 1. Структура, архитектура и функционирование Электонных Вычислительных Машин и микропроцессорных систем

- •1.1. История развития информации и вычислительной техники

- •1.2. Этапы развития электронно-вычислительной техники

- •1.3. Классическая архитектура электронной вычислительной машины и принципы фон Неймана

- •1.4. Архитектура мини-эвм и микропроцессора

- •1.5. Принцип работы микро-эвм

- •Глава 2. Числа, кодирование и арифметические операции

- •2.1. Арифметические основы микропроцессорной техники

- •2.2. Двоичная арифметика

- •2.3. Дополнительный код

- •2.4. Арифметика в дополнительном коде

- •2.5. Группировка бит

- •2.6. Буквенно-цифровой код

- •Глава 3. Основные элементы микропроцессорной техники

- •3.1. Логические элементы

- •3.2. Электронные логические вентили

- •3.3. Комбинации логических элементов

- •3.4. Практическая реализация логических вентилей

- •3.5. Задержка на распространение сигнала

- •3.6. Ограничения по входу и выходу

- •3.7. Тристабильные элементы

- •3.8. Мультиплексор и демультиплексоры

- •3.9. Дешифраторы

- •3.10. Модули интегральных микросхем

- •3.11. Триггеры и защелки

- •3.12. Тактирование фронтом сигнала

- •3.15. Триггеры с дополнительными входами для установки и очистки

- •3.16. Регистры и сдвиговые регистры

- •3.17. Счетчики

- •Глава 4. Программируемые логические устройства

- •4.1. Программируемая логическая матрица

- •4.2. Программируемая матричная логика

- •4.3. Сложные программируемые логические устройства

- •4.4. Программируемые вентильные матрицы

- •4.5. Пример счетчика с прямым/обратным счетом

- •4.6. Временные диаграммы

- •4.7. Модель конечного автомата

- •4.8. Синтез конечных автоматов

- •Глава 5. Полупроводниковая память

- •5.1. Микросхемы rom

- •5.2. Затенение rom

- •5.3. Прожигаемая при изготовлении память rom

- •4.4. Память prom

- •5.5. Память eprom

- •5.6. Системная память

- •5.7. Быстродействие озу

- •5.8. Динамическая и статическая память

- •5.9. Память типа dram

- •5.10. Статическая память

- •5.13. Подсистема памяти

- •5.14. Организация кэш-памяти

- •5.15. Принципы организации основной памяти в современных компьютерах

- •5.16. Виртуальная память и организация защиты памяти

- •5.17. Модули памяти

- •5.18. Использование оперативной и постоянной памяти

- •Глава 6. Основы микропроцессорной техники

- •6.1. Архитектура простой микро-эвм

- •6.2. Структура простейшей памяти

- •6.3. Состав команд

- •6.4. Структура элементарного микропроцессора

- •6.5. Функционирование микро-эвм

- •6.9. Код коррекции ошибок

- •Глава 7. Микропроцессорная система

- •7.1. Классификация

- •7.2. Определение понятия микропроцессор

- •7.3. Основные характеристики микропроцессора

- •7.4. Шинная структура связей

- •7.5. Логическая структура микропроцессора

- •7.6. Режимы работы микропроцессорной системы

- •7.7. Архитектура микропроцессорных систем

- •7.8. Типы микропроцессорных систем

- •Глава 8. Организация обмена информацией

- •8.1. Циклы обмена микропроцессорной системы

- •8.2. Шины микропроцессорной системы

- •8.3. Организация циклов обмена информацией

- •8.4. Прохождение сигналов по магистрали

- •8.5. Функции устройств магистрали

- •Глава 9. Функционирование процессора

- •9.1. Адресация операндов

- •9.2. Регистры процессора

- •9.3. Система команд процессора

- •Глава 10. Организация микроконтроллеров

- •10.1. Процессорное ядро и память микроконтроллеров

- •10.2. Классификация и структура микроконтроллеров

- •10.3. Система команд процессора мк

- •10.4. Схема синхронизации мк

- •10.5. Память программ и данных мк

- •10.6. Порты ввода/вывода

- •Библиографический список

- •Основы микропроцессорной техники

- •Издательство государственного образовательного учреждения высшего профессионального образования

- •625000, Тюмень, ул. Володарского, 38

- •6 25039, Г. Тюмень, ул. Киевская, 52

6.4. Структура элементарного микропроцессора

Основным устройством всех информационных систем является центральный процессор (ЦП). Из многочисленных ИС роль ЦП систем выполняют микропроцессоры. Обычно в технологии микроинформационной техники программную память, память данных, интерфейс ввода-вывода, дешифратор адресов выполняют на различных ИС, как это показано на рис. 6.1.

Центральным устройством системы является микропроцессор, который содержит обычно элементы размещения данных, называемые регистрами, и устройство счета, называемое арифметико-логическим устройством (АЛУ). Центральное устройство содержит также цепь декодирования команд и секцию управления и синхронизации. Оно снабжено также необходимыми соединениями с устройством ввода/вывода.

Основными функциями центрального устройства микро-ЭВМ являются следующие:

-

извлечение, декодирование и выполнение команд программы в указанном порядке;

-

передача данных из памяти и в память и из УВВ и в УВВ;

-

ответы на внешние прерывания;

-

установка общей синхронизации и сигналов управления для всей системы.

Большинство центральных устройств содержит по меньшей мере элементы, схематически представленные на рис. 6.5.

Рис. 6.5. Упрощенная архитектура центрального процессора

Наиболее важные секции содержат различные регистры, АЛУ, дешифратор команд, устройства управления и синхронизации, а также УВВ. В настоящее время большинство микропроцессоров содержат множество дополнительных специальных регистров (на рис. 6.5 не показаны).

Арифметико-логическое устройство ЦП выполняет такие операции, как сложение, сдвиг/перестановка, сравнение, инкремент, декремент, отрицание, И, ИЛИ, ИЛИ ИСКЛЮЧАЮЩЕЕ, дополнение, сброс, инициализация.

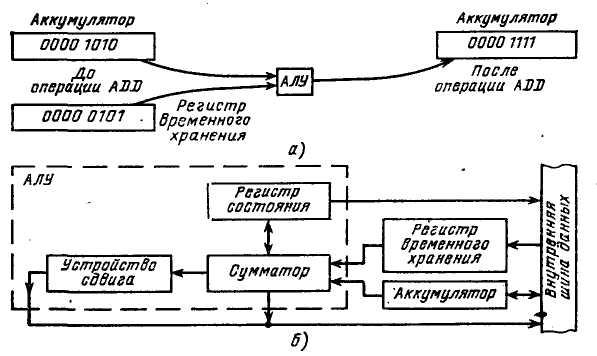

Если АЛУ должно выполнить операцию сложения посредством команды ADD, процедура могла бы быть аналогичной представленной на рис. 6.6, а.

Рис. 6.6. Выполнение операции ADD (а) и структура АЛУ (б)

Здесь содержимое аккумулятора 0АН складывается с содержимым регистра временного хранения данных 05Н. Сумма 0FH помещена в аккумулятор.

На рис. 6.6, б приведены основные функциональные элементы типового АЛУ. Оно содержит сумматор и устройство сдвига, а результаты пересылаются в аккумулятор посредством внутренней шины данных. Регистр состояния слова в АЛУ является устройством чрезвычайно важным (его называют иногда регистром кода условий или индикатором - флажковым регистром. Тогда соответствующие триггеры или индикаторы этого регистра называются флагами — флаг нуля, флаг знака и т. д..). Этот регистр состоит из группы триггеров, которые могут быть установлены или сброшены исходя из результатов последней операции, выполненной АЛУ. Эти триггеры или индикаторы содержат указатели нуля, отрицательного результата, переноса и т. д. Индикаторы используются для принятия решений, когда вводятся команды ветвлений. Аккумулятор обычно используется в ходе большинства операций, выполняемых центральным устройством, например, передачи данных. Устройство управления и синхронизации (см. рис. 4.7) является наиболее сложным в центральном процессоре.

Оно влияет на все события и управляет их протеканием внутри центрального устройства и во всей микро-ЭВМ. Мы упоминали в предыдущей главе, что каждая команда программы может быть разделена на этапы извлечения и выполнения. Каждый из них в свою очередь может быть разделен на элементарные микропрограммы. Микропрограммы каждой команды находятся в секции декодирования и выполняются блоком управления и синхронизации центрального устройства.

Шестнадцатиразрядный регистр, называемый счетчиком команд, представлен на рис. 6.5 как элемент, составляющий часть центрального устройства. Этот регистр служит для хранения адреса следующей команды, чтобы извлечь ее из памяти. Так как команды выполняются последовательно, счетчик команд считает прямым счетом, если только нет контрпорядка. Большая часть выпускаемых микропроцессоров имеет 16-разрядный, счетчик команд, который может адресовать 64 К слов памяти посредством адресной шины. Нормальная последовательность выполнения команд программы может быть изменена специальными командами ветвления, вызова подпрограмм, возврата из подпрограмм или прерывания. Эти команды повлекут переход содержимого счетчика команд на другую величину, отличную от следующего старшего адреса. Чтобы вернуть программу в исходное состояние после последовательности ее запуска, оператор должен восстановить в счетчике команд номер первой команды программы.

Последовательность извлечение-декодирование-выполнение команд является основой функционирования вычислительной машины. Первая команда, извлеченная из памяти программы, определяет код операции первой команды и помещается в регистр команд устройством управления центральным процессором. Код операции истолковывается дешифратором команд, который указывает затем процессору процедуру управления и синхронизации, которой должна следовать программа для выполнения заданной команды.

Центральное устройство, показанное на рис. 6.5, является элементарным. Большая часть центральных устройств МП содержит, по меньшей мере, несколько дополнительных регистров (8 и 16 бит). Существуют очень большие различия в количестве и типе регистров в зависимости от типов МП.