- •А.Л. Ахтулов, л.Н. Ахтулова, с.И. Смирнов основы микропроцессорной техники

- •Содержание

- •Глава 1. Структура, архитектура и функционирование Электонных Вычислительных Машин и микропроцессорных систем

- •1.1. История развития информации и вычислительной техники

- •1.2. Этапы развития электронно-вычислительной техники

- •1.3. Классическая архитектура электронной вычислительной машины и принципы фон Неймана

- •1.4. Архитектура мини-эвм и микропроцессора

- •1.5. Принцип работы микро-эвм

- •Глава 2. Числа, кодирование и арифметические операции

- •2.1. Арифметические основы микропроцессорной техники

- •2.2. Двоичная арифметика

- •2.3. Дополнительный код

- •2.4. Арифметика в дополнительном коде

- •2.5. Группировка бит

- •2.6. Буквенно-цифровой код

- •Глава 3. Основные элементы микропроцессорной техники

- •3.1. Логические элементы

- •3.2. Электронные логические вентили

- •3.3. Комбинации логических элементов

- •3.4. Практическая реализация логических вентилей

- •3.5. Задержка на распространение сигнала

- •3.6. Ограничения по входу и выходу

- •3.7. Тристабильные элементы

- •3.8. Мультиплексор и демультиплексоры

- •3.9. Дешифраторы

- •3.10. Модули интегральных микросхем

- •3.11. Триггеры и защелки

- •3.12. Тактирование фронтом сигнала

- •3.15. Триггеры с дополнительными входами для установки и очистки

- •3.16. Регистры и сдвиговые регистры

- •3.17. Счетчики

- •Глава 4. Программируемые логические устройства

- •4.1. Программируемая логическая матрица

- •4.2. Программируемая матричная логика

- •4.3. Сложные программируемые логические устройства

- •4.4. Программируемые вентильные матрицы

- •4.5. Пример счетчика с прямым/обратным счетом

- •4.6. Временные диаграммы

- •4.7. Модель конечного автомата

- •4.8. Синтез конечных автоматов

- •Глава 5. Полупроводниковая память

- •5.1. Микросхемы rom

- •5.2. Затенение rom

- •5.3. Прожигаемая при изготовлении память rom

- •4.4. Память prom

- •5.5. Память eprom

- •5.6. Системная память

- •5.7. Быстродействие озу

- •5.8. Динамическая и статическая память

- •5.9. Память типа dram

- •5.10. Статическая память

- •5.13. Подсистема памяти

- •5.14. Организация кэш-памяти

- •5.15. Принципы организации основной памяти в современных компьютерах

- •5.16. Виртуальная память и организация защиты памяти

- •5.17. Модули памяти

- •5.18. Использование оперативной и постоянной памяти

- •Глава 6. Основы микропроцессорной техники

- •6.1. Архитектура простой микро-эвм

- •6.2. Структура простейшей памяти

- •6.3. Состав команд

- •6.4. Структура элементарного микропроцессора

- •6.5. Функционирование микро-эвм

- •6.9. Код коррекции ошибок

- •Глава 7. Микропроцессорная система

- •7.1. Классификация

- •7.2. Определение понятия микропроцессор

- •7.3. Основные характеристики микропроцессора

- •7.4. Шинная структура связей

- •7.5. Логическая структура микропроцессора

- •7.6. Режимы работы микропроцессорной системы

- •7.7. Архитектура микропроцессорных систем

- •7.8. Типы микропроцессорных систем

- •Глава 8. Организация обмена информацией

- •8.1. Циклы обмена микропроцессорной системы

- •8.2. Шины микропроцессорной системы

- •8.3. Организация циклов обмена информацией

- •8.4. Прохождение сигналов по магистрали

- •8.5. Функции устройств магистрали

- •Глава 9. Функционирование процессора

- •9.1. Адресация операндов

- •9.2. Регистры процессора

- •9.3. Система команд процессора

- •Глава 10. Организация микроконтроллеров

- •10.1. Процессорное ядро и память микроконтроллеров

- •10.2. Классификация и структура микроконтроллеров

- •10.3. Система команд процессора мк

- •10.4. Схема синхронизации мк

- •10.5. Память программ и данных мк

- •10.6. Порты ввода/вывода

- •Библиографический список

- •Основы микропроцессорной техники

- •Издательство государственного образовательного учреждения высшего профессионального образования

- •625000, Тюмень, ул. Володарского, 38

- •6 25039, Г. Тюмень, ул. Киевская, 52

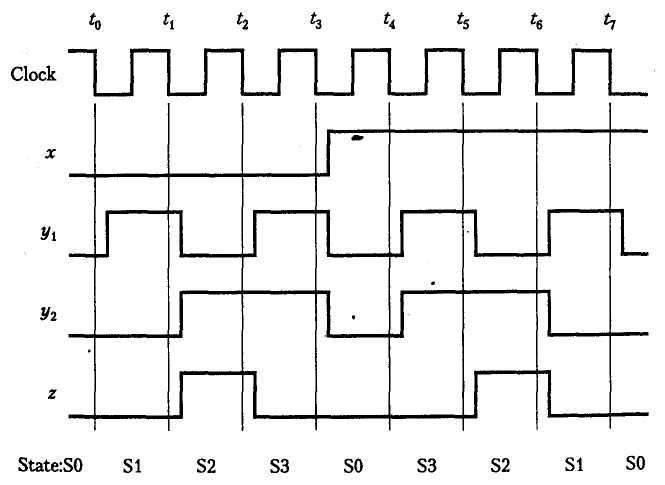

4.6. Временные диаграммы

Для того чтобы полнее представить себе работу схемы счетчика, необходимо рассмотреть его временную диаграмму. На рис. 4.10 приведен пример возможной последовательности событий, происходящих в нашей схеме. Предполагается, что переходы между состояниями (изменения значений триггеров) происходят на отрицательном фронте тактирующего сигнала и что начальным состоянием счетчика является S0. Вначале х = 0. Поэтому в момент времени t0 счетчик переходит в состояние S1, затем, в момент времени t1 он переходит в состояние S2 (и на выходе z является значение 1), а затем, в момент времени t2, — в состояние S3 (на и выходе z мы снова видим 0). Далее, в момент времени t3, счетчик снова переходит состояние S0. Предположим, что в этот момент входное значение х меняется на 1, чего счетчик начинает считать в обратном порядке. Когда в момент времени t5 счетчик снова достигнет состояния S2, на выходе z опять появится значение 1

Рис. 4.10. Временная диаграмма для схемы, приведенной на рис. 4.9

Обратите внимание, что все изменения сигналов происходят сразу после появления отрицательного фронта тактового сигнала, и сигналы больше не меняются до тех пор, пока не появится отрицательный фронт следующего тактового сигнала.

Время задержки между фронтом тактового сигнала и изменением переменной уi- это время задержки на распространение сигнала в триггерах, на основе которых создана схема счетчика. Важно отметить, что вход х управляется тем же тактовым алом и изменяется в начале такта. Схемы, в которых все изменения управляются тактовым сигналом, называются синхронными последовательными схемами.

Еще одно важное наблюдение касается соответствия диаграммы состояний, представленной на рис. 4.8, временной диаграмме. Возьмем, к примеру, тактовый период между моментами времени t1 и t2. В течение этого времени схема находится в состоянии S2 и на ее входе сохраняется значение х = 0. На диаграмме состояний эта ситуация представлена исходящей из узла S2 стрелкой с надписью х = 0. Поскольку эта стрелка указывает на узел S3, на следующем фронте тактового сигнала (t2) переменные у1 и у2 принимают значения, соответствующие состоянию S3. А пока счетчик будет оставаться в состоянии S2, на выходе z будет значение 1.

4.7. Модель конечного автомата

Рассмотренный нами пример счетчика с прямым/обратным счетом, реализованного в виде синхронной последовательной схемы на основе триггеров и вентильной комбинаторной логики (рис. 4.9), легко обобщить до формальной модели конечного автомата, показанной на рис. 4.11.

В этой модели запаздывание при прохождении сигнала через элементы задержки равно длительности такта. Это время между изменениями, происходящими в точках Yi и соответствующими изменениями в точках уi. В данной модели предполагается, что через блок комбинаторной логики сигналы проходят без задержки; поэтому выходные значения z, Y1 и У2 являются мгновенными функциями входных значений х, у1 и у2

Рис. 4.11. Модель конечного автомата

. В реальной схеме все элементы, как показано на рис. 4.10, служат источниками определенных задержек. Схема будет работать правильно лишь при условии, что задержка блока комбинаторной логики не велика по сравнению с длительностью такта. Значения на выходах следующего состояния, Y1 и Y2, должны быть установлены таким образом, чтобы состояния триггеров изменились до окончания такта. Кроме того, в течение некоторого времени на выходе z требуемого значения может не быть, но оно должно появиться задолго до окончания такта.

Входы блока комбинаторной логики соединены с выходами триггеров уi предшествующих текущее состояние, и с внешним входом х. Выходы блока, обозначенные как Yi , соединены со входами триггеров и внешним выходом z. На отрицательном фронте тактового сигнала, соответствующем концу текущего такта, в триггеры загружаются значения выходов Yi которые становятся следующими значениями переменных состояния уi . Поскольку выходы триггеров соединены со входами блока комбинаторной логики, они вместе со следующим значением внешнего входа х определяют новые значения переменных z и Yi . На следующем такте значения Yi передаются на входы yi и процесс повторяется сначала. Таким образом, триггеры образуют обратную связь между выходом и входом комбинаторного блока с задержкой в один такт.

Хотя в рассмотренной нами схеме (рис. 4.11) имелся лишь один внешний вход и две переменные состояния, совершенно очевидно, что в схеме может быть нескольку переменных каждого из трех типов.