- •1.Основные термины определения

- •2.Основные элементы логических функции алгебры логики (или-or,и-and, и- не -and-not, и- или -не-and-or-not)

- •3.Задание логических функции с элементами структурных формул (сднф, скнф).

- •2.Табличное описание (представление) мажоритарного устройства

- •Мажоритарное устройство

- •3. Математическое описание мажоритарного устройства

- •4. Схемное представление мажоритарного устройства

- •5. Физическая реализация мажоритарного устройства

- •1 Вопрос: Синтез шифратора и дешифратора

- •Раздел II

- •Назначение и классификация регистров.

- •Синтез регистров (регистры памяти, сдвига).

-

Назначение и классификация регистров.

-

Синтез регистров (регистры памяти, сдвига).

1-й учебный вопрос.

Регистром называется последовательностное цифровое устройство (ПЦУ), предназначенное для хранения небольших объемов информации и преобразования над n-разрядным двоичным кодом.

Регистр представляет собой упорядоченную последовательность триггеров, как правило D- триггеров, число которых соответствует разрядности регистра.

|

|

|

|

|

|

|

|

|

Восьми разрядный регистр

Преобразования в регистрах:

1. Обмен информации между регистрами(пересылка данных)

2. Поразрядные логические операции

Примечание: Логические операции осуществляются поразрядно

Примеры:

Cдвиг слова влево или вправо

Сдвиг слова влево на 1 разряд-умножение содержимого на 2

Сдвиг слова вправо на 1 разряд- деление содержимого на 2

Рассмотрим примеры.

сдвиг

на 1 разряд влево

сдвиг

на 1 разряд влево

c

c двиг

вправо на 1 разряд

двиг

вправо на 1 разряд

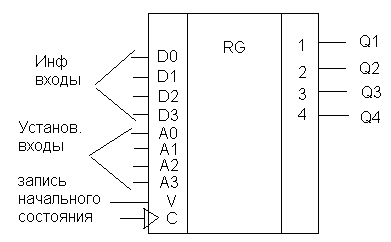

УГО регистра

Классификация регистров.

В зависимости от содержания выполняемых операций в регистре, регистры бывают:

-

С параллельным приемом и параллельной выдачей информации. На этом принципе выполнено ОЗУ.

-

С параллельным приемом и последовательной выдачей информации.

3) С последовательным приемом и параллельной выдачей информации.

2-ой учебный вопрос Синтез регистров

Принцип синтеза регистров: все регистры состоят из одинаковых блоков, количество которых определяется разрядностью регистра. Каждый блок включает триггер (D- триггер) и сравнительно простое КЦУ. Следовательно, синтез регистра сводится к синтезу 1 блока с учетом связей между ними.

регистры памяти (регистры с параллельным приемом и параллельной выдачей информации).

Рассмотрим схему 4-х разрядного регистра памяти:

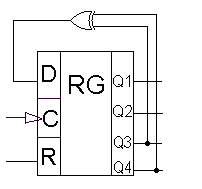

2) Регистры сдвига (регистры с последовательным приемом и параллельной выдачей информации).

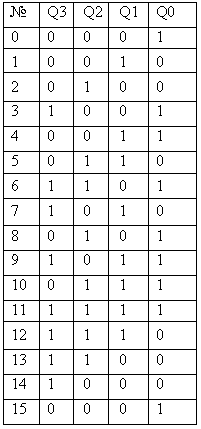

Таблица переключений регистра сдвига без ОС

|

№ |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

1 |

0 |

0 |

0 |

|

4 |

0 |

0 |

0 |

0 |

|

5 |

0 |

0 |

0 |

0 |

|

6 |

0 |

0 |

0 |

0 |

|

7 |

0 |

0 |

0 |

0 |

|

8 |

0 |

0 |

0 |

0 |

Реверсивный регистр

Это регистр, в котором информация сдвигается как влево , так и вправо.

Регистры сдвига с обратными связями.

Если соединить выход любого разряда регистра с входом, то получим кольцевой регистр, в котором информация будет перемещаться по кольцу.

-

УГО регистра с прямой обратной связью

-

Кольцевой регистр с перекрестной обратной связью.

Когда в цепи обратной связи включен инвертор:

-

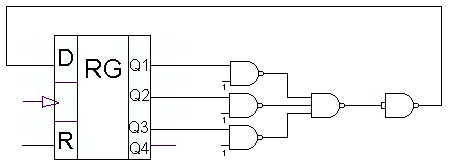

Кольцевой регистр с логической обратной связью

Это регистр, в цепи обратной связи которого включено логическое устройство. В нашем примере логическим устройством является сумматор по модулю 2

УГО регистра с логической обратной связью.

Кцикл=

2N

-1, где N-

разрядность регистра

Кцикл=

2N

-1, где N-

разрядность регистра

Регистр сдвига самовосстановления.

Рассмотрим одну из возможных схем регистра самовосстановления: данная схема обеспечивает перемещение по кольцу 1, т.е. наличие унитарного кода.

Лекция: Двоичные и двоично-десятичные счетчики

Учебные вопросы:

1.определение и классификация счетчиков

2.синтез двоичных и двоично-десятичных счетчиков

1 вопрос:

Счетчик- это последовательное цифровое устройство, которое обеспечивает хранение слова информации и выполнение над ним микрооперации счета.

Микрооперация счета- изменение числа на +-1

Суммирующий счетчик- это то, что было в счетчике +1

С=С+1

Вычитающий счетчик- это то ,что было в счетчике -1

С=С-1

Реверсивный счетчик: С= + -1(и то и другое выполняет)

Счетчики работают в двоичном коде и обеспечивают подсчет импульсов в интервале от 0 до 2N-1, где N- количество разрядов счетчика

Например: 4- х разрядный счетчик обеспечивает значение числа от 0-2(4)-1=15

0 - 15

Примечание : после достижения максимального значения суммирующий счетчик начинает счет с 0.

Пример : 0,…..,C,D,E,F,0,1……

Вычитающий счетчик: …..C,B,A,9…2,1,0,F…

Для построения счетчиков используются Т- триггеры(D,JK триггеры в режиме Т- триггеры)

D- триггер

JK – триггер

УГО счетчика

>15(P) – перенос в старший разряд при суммировании

< 0(CR) – заем из старшего разряда при вычитании

2-й учебный вопрос:

Cинтез двоичных и двоично-десятичных счетчиков

Классификация счетчиков по структуре:

Счетчики с последовательным переносом (асинхронные). У этих счетчиков переключающий сигнал и сигнал управления совмещены.

Тперекл=N×Тперекл 1разр;

где: Тперекл – общее время переключения счетчика;

N - разрядность счетчика;

Тперекл 1разр - время переключения 1-ого разряда счетчика.

Счетчики с параллельным переносом (синхронные), у которых синхросигнал подается одновременно на все триггеры, а сигнал управления от одного триггера к другому. Техническая реализация синхронного намного сложнее асинхронного, но обладает повышенным быстродействием, а именно:

Тперекл=Тперекл 1разр

Быстродействие счетчика с параллельным переносом в N раз больше последовательно.

Рассмотри пример 3-х разрядного суммирующего счетчика с последовательным переносом.

Таблица переключения (истинности):

|

№ наб.

|

Q2 |

Q1

|

Q0 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

Из анализа таблицы переключения следует, что в каждом разряде присутствует чередование 1 и 0 с различной периодичностью

(Т, 2Т, 4Т и т.д.). Следовательно, для физической реализации необходимо выбрать Т-триггеры и учесть их соединение с учетом синхронизации триггеров (передний или задний фронт) и функционального предназначения счетчика (суммирующий или вычитающий).

Соединение для суммирующего счетчика и синхронизации по переднему фронту имеет вид:

Если выходы Qi предыдущего триггера соединить с входом синхронизации следующего триггера, то получим вычитающий счетчик, в котором синхронизация по переднему фронту.

Синтез счетчиков с заданным коэффициентом счета

(двоично – десятичные счетчики)

На практике очень часто создаются счетчики с заданным коэффициентом счета.

Например: двоично – десятичные счетчики, т.е. счетчики, которые обеспечивают счет от 0 до 9 (для часов 0÷59 и т.д.). Для организации таких счетчиков необходимо создать обратные связи, которые обеспечили бы устранение лишних значений счета

0,1,2,3…7,8,9, 0 (вместо 10) ,1,2.. и т.д.

Для двоично- десятичного счетчика необходимо представить число 10 в двоичной системе счисления:1010 и соединить единичные разряды со ЛЭ 2И (2AND). Выход ЛЭ подать на вход R (Reset) 4-х разрядного счетчика.

Аналогично можно синтезировать счетчика для заданного Ксч.

Дисциплина : Вычислительная техника и информационные технологии

Лекция 1: Общие принципы организации МПС

1. Структура, архитектура МПС.

2. Структура, архитектура однокристального восьмиразрядного МП КР580ВМ80.

МПС – микропроцессорная система.

МП – микропроцессор.

Литература : 1. Евриинов Э.В «Цифровая вычислительная техника».

2. Яковлев Л.А , Тимченко В.И «Вычислительная техника» Методические указания к лабораторным работам .

3. Методические указания по курсовому проектированию по дисциплинам «Цифровая и вычислительная техника, …..», Спб ГУТ , 1997г.

1. Структура, архитектура МПС.

МПС – аппаратно-программное устройство, которое осуществляет программную реализацию алгоритмов цифровой обработки информации.

МПС включает 3 основных блока:

Центральный микропроцессор (ЦМП).

Запоминающие устройство (ЗУ), которое включает: оперативное запоминающие устройство (ОЗУ), функционирует только при наличии питания, и постоянное запоминающие устройство (ПЗУ) – жесткие диски , flesch-память, которые хранят информацию в отсутствие электропитания.

Устройства ввода-вывода (мышь, клавиатура, принтер, дисплей)

Объем устройств ввода-вывода = 28= 256.

Объем адресного пространства = 216= 64536 адресов.

Принцип работы МПС состоит в выполнении заранее разработанной программы, которая определяет последовательность выполнения команд (операций).

Ассемблер MOV B,C ; комментарий (B) (C)

Код МП 01000001 - 41 h

Выполнение программы осуществляется последовательным считыванием с ЗУ команды , её дешифрированием и выполнением .

Выполнение команды осуществляется в 2 этапа :

Считывание и дешифрирование команды: ЦМП выставляет на шину адреса (ША) адрес очередной выполняемой команды. Этот адрес по ША поступает в ЗУ. Кроме того, в ЗУ по шине управления (ШУ) подается сигнал чтения содержимого ячейки памяти (ЯП). Содержимое ЯП с кодом операции (КОП) по шине данных (ШД) поступает в ЦМП .

По результатам дешифрирования КОП МП осуществляет выполнение команды.

По окончании выполнения команды на ША выставляется адрес очередной выполняемой команды.

2-й учебный вопрос:

Структура, архитектура однокристального восьмиразрядного МП КР580ВМ80.

МП – программно-управляемое устройство реализуемое на одном чипе , которое осуществляет процесс цифровой обработки информации и управление этих процессов.

МП бывают: 8-, 16- , 32- , 64- разрядныt

Рассмотрим структуру однокристального 8-ми разрядного МП КР580ВМ80

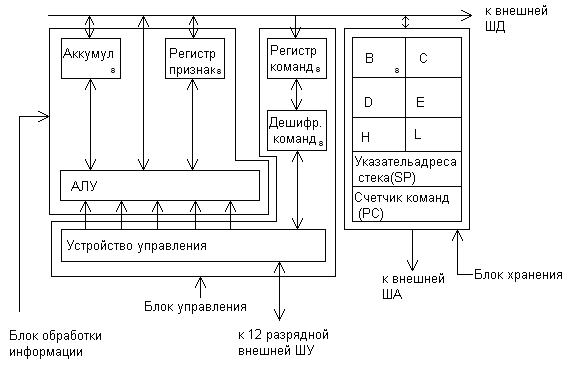

ЦМП состоит из 3-х основных блоков:

1)Блок обработки информации:

8 разрядный регистр – аккумулятор, для хранения 1-го операнда команды и результата выполнения команды.

8 разрядный регистр признаков, для хранения признаков арифметических и логических операций.

|

№ разряда регистра |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

наименование признака |

S |

Z |

0 |

AC |

0 |

P |

1 |

CY |

Признак S – признак отрицательного результата АЛУ (S=1)

Признак Z – признак нулевого результата АЛУ (Z=1)

Признак АС – перенос между полубайтами (АС=1)

Признак Р – признак четного числа нулей в аккумуляторе при выполнении арифметических , логических операций (Р=1)

Признак CY - признак переноса старшего разряда при выполнении АЛУ .

Арифметическое - логическое устройство (АЛУ) – для выполнения арифметических и логических операций.

2) Блок управления включает:

регистр команд, для хранения кода выполняемой команды (операции);

дешифратор команд, для дешифрирования кода операции и формирования сигналов управления при выполнении команды;

устройство управления, для управления процессом обработки информации

3) Блок хранения включает:

Шесть 8-ми разрядных регистров: B,C,D,E,H,L, для временного хранения данных (прототип кэш памяти). Регистры могут использоваться 8-ми разрядными или строго определенными парами: B-C, D-E, H-L (регистры используются? как 16-ти разрядные)/

Указатель адреса стека (SP) 16-ти разрядный регистр, для хранения начального адреса стековой памяти.

Стековая память – область ОЗУ и предназначена для хранения данных при выполнении команд условных переходов, организации прерывания и других данных.

Принцип построения стековой памяти: первым записан – последним прочитан.

Счетчик команд CP (16-ти разрядный регистр) для хранения адреса очередной выполняемой команды.

Функционирование МП

МП последовательно выполняет команду за командой . каждая команда выполняется в 2 этапа:

Выборка команды. Счетчик команд под воздействием сигналов управления По ША команда поступает В ЗУ . Под воздействием сигналов управления поступает по ШУ содержимое выставляет на ША 16-ти разрядный адрес ЯП ЗУ, в которой хранится код команды (КОП). ЯП указанного адреса поступает по ШД в регистр команд МП и дешифрируется.

-

Выполнение команды. Под воздействием сигналов управления осуществляется выполнение по тактам команды, код операции которой в регистре команд. Для арифметических и логических операций формируются признаки в регистре признаков. По окончании выполнения команды счетчик команды (РС) записывает адрес очередной выполняемой команды.

Система команд.

-

Структура команд и способы адресации

-

содержание системы команд

Система команд – перечень команд выполняемых данным МП .

Каждый МП имеет свою систему команд.

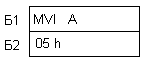

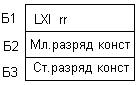

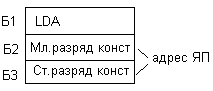

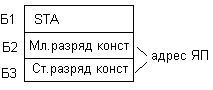

Структура команд : команды бывают 1-о, 2-х и 3-х байтные

-

1-о байтная команда – в одном байте КОП (код операции) и операнд

MOV rd, rs ; (rd) (rs)

MOV rd, rs ; (rd) (rs)

при этом содержание rs не изменяется

-

2-х байтные команды – в первом байте КОП команды и операнды , во втором байте только операнд .

-

3-х байтные команды - в первом байте КОП команды , во втором и

третьем – операнды.

(0106h)

(А)

(0106h)

(А)

Режимы адресации

В системе команд применяют следующие режимы адресации:

1. Прямая адресация – код адреса в команде является исполнительным адресом обращения к памяти.

(A)

([0106h])

(A)

([0106h])

2. Регистровая адресация – операнд содержится в одном из регистров МП.

(B)

(A)

(B)

(A)

3. Непосредственная адресация – операнд задан в команде

MVI A, 05h

(A)

05h

MVI A, 05h

(A)

05h

4.Регистровая косвенная адресация – когда адрес ЯП с операндом хранится в

одной из регистровых пар, например в регистровой паре H-L.

![]() (A)

([HL])

(A)

([HL])

В аккумулятор записывается содержимое ЯП, адрес которой хранится в регистровой паре HL.

Классификация системы команд

Система команд включает следующую группу команд:

-

Команды пересылок данных

-

Команды безусловного и условного переходов.

-

Команды арифметических , логических операций и сравнения

-

Команды ввода-вывода данных

-

Команды операции со стеком и другие команды(команды обращения к подпрограмме, остановок)

Команды пересылок данных

Структура:

![]() (rd)

(rs)

(rd)

(rs)

A, B, C, D, E, H, L

Пример: MOV B, C ; (B) (C)

Пересылка регистровая

Пересылка константы в регистр

(r)

(<Б2>)

(r)

(<Б2>)

Пересылка данных (косвенная адресация)

![]() ([HL])r

([HL])r

Загрузка константы в пару регистров

(rr) (<Б3><Б2>)

(rr) (<Б3><Б2>)

(rr) - B-C, D-E, H-L, PSW

PSW – (регистр аккумулятора и регистр признаков)

Загрузка аккумулятора (прямая адресация)

(A)

([<Б3><Б2>])

(A)

([<Б3><Б2>])

Из аккумулятора

([<Б3><Б2>])

(А)

([<Б3><Б2>])

(А)

При выполнении команд пересылок данных не формируются признаки нулевого результата и положительного отрицательного числа.

Арифметические и логические команды

Арифметические команды сложения.

Сложение содержимого регистра с аккумулятором

![]() (A)

(A) + (r)

(A)

(A) + (r)

Сложение константы с аккумулятором

(А)

(А) + (<Б2>)

(А)

(А) + (<Б2>)

Инкрементные команды (добавление единицы либо к ЯП либо к регистру)

Инкремент регистра

![]() (r)

(r) + 1

(r)

(r) + 1

Инкремент регистровой пары

![]() (rr)

(rr) + 1

(rr)

(rr) + 1

Арифметические команды вычитания

Вычитание содержимого регистра из аккумулятора

![]() (A)

(A) – (r)

(A)

(A) – (r)

Вычитание константы из аккумулятора

(A)

(A) – (<Б2>)

(A)

(A) – (<Б2>)

Декрементные команды (вычитание единицы)

Декремент регистра

![]() (r)

(r) - 1

(r)

(r) - 1

Декремент регистровой пары

![]() (rr)

(rr) - 1

(rr)

(rr) - 1

При выполнении арифметических команд изменяются значения регистров признаков.

Команды ввода-вывода данных

Вводи вывод данных в 8-ми разрядных МП КР580ВМ80, Int 080-085 , Z=80 осуществляется только через аккумулятор.

Команда ввода данных

(A)

([<Б2>])

(A)

([<Б2>])

В аккумулятор вводится содержимое с того устройства , адрес которого находится в <Б2>

Команда вывода данных

([<Б2>])

(A)

([<Б2>])

(A)

Команды логических операций

AND(и), OR (или) , NOT(не), XRA(сложение по модулю 2)

![]() (A) (A) ^ (r)

(A) (A) ^ (r)

(A) (A) ^ (<Б2>)

(A) (A) ^ (<Б2>)

![]() (A) (A) v (r)

(A) (A) v (r)

(A) (A) v (<Б2>)

(A) (A) v (<Б2>)

![]()

![]() инверсия

инверсия

![]()

![]()

Логическое сравнение

Команды используются перед выполнением команд условных переходов.

Изменяется только значение регистровых признаков, например Z, S …

![]() (A) – (r)

(A) – (r)

(A) – (<Б2>)

(A) – (<Б2>)

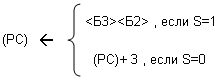

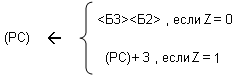

Команды безусловного и условного переходов

(команды управления )

Команды управления предназначены для изменения процессов вычисления.

Все команды управления 3-х байтные.

Безусловный переход.

(PC)

(<Б3><Б2>)

(PC)

(<Б3><Б2>)

(PC) – счетчик команд

Переход если «-» .

Переход если не «0» .

Переход если «0».

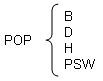

Команды работы со стеком

(стековой памятью)

Стековая память – область ОЗУ, которая формируется по принципу “первым записан – последним прочитан ”. Для организации стековой памяти необходимо сформировать адрес начала стековой памяти. Как правило адрес начала стековой памяти записывается конечный адрес ОЗУ. По мере заполнения стековой памяти значение адресов уменьшается. В стековую память записываются данные только двух байтов (2-х регистров).

|

Адрес ЯП ,h |

Содержимое ЯП |

|||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

0000 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0001 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7770 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8036 |

|

|

|

|

|

|

|

|

|

8037 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FFFF |

|

|

|

|

|

|

|

|

Для задания вершины стековой памяти можно использовать одну из двух команд.

Содержимое HL перемещается в указатель стека SP

![]() (SP)

(HL)

(SP)

(HL)

(SP)

(<Б3><Б2>)

(SP)

(<Б3><Б2>)

Запись и чтение содержимого стековой памяти.

В стековую память записываются данные регистров РОН : (ВС ), (DE), (HL), PSW

Команда записи данных в стековую память

Например : PUSH B ; в стековой памяти запись содержимого ВС.

Команда чтения данных из стековой памяти

Например :РОР D ;запись содержимого стековой памяти в регистровую

пару ( DE).

Обращение к подпрограммам.

При выполнении основной программы можно организовать ветвление программы не только с помощью команд безусловного и условного переходов, но и путем применения команд “обращения к подпрограммам”.

Команда обращения к подпрограмме.

(РС)

ß (<Б3

><Б2>)

(РС)

ß (<Б3

><Б2>)

(SP)ß(SP)- 2

Последней командой в подпрограмме должна быть команда

![]() (PC)L

ß(SP)

(SP)ß(SP)+2

(PC)L

ß(SP)

(SP)ß(SP)+2

(PC)H ß(SP)+1

Последовательность разработки, отладки и выполнения программ на языке “assembler” для симулятора AVSIM 85.

Этапы разработки, отладки и выполнения программ на AVSIM 85.

-

Словесная (вербальная) постановка задачи.

-

Разработка алгоритма программы.

-

Написание программы.

-

Трансляция программы – перевод текста пользователя в код МП (obj)

Компоновка программы (hex)

-

Отладка программы.

-

Выполнение программы.

Рассмотрим последовательность отладки и выполнения программ.

1 этап. Разработать 4-х разрядный двоичный вычитающий счетчик , с произвольными начальными и конечными значениями.

Qнач =5 Qкон = 8

ANI 0F (A)ß(A)^ 0F

2 этап. Разработка алгоритма.

3 этап. Написание программы.

Для написания программы используйте “Блокнот”. Сохранять файл программы с расширением “asm”

Test3.asm

outport equ 1

Qn equ 5

Qk equ 8

Include init .asm

Begin:

MOV C, Qn

M1

MOV A, C

OUT outport

DCR C

MOV A,C

ANI 0F

MOV C,A

CPI 7 ; (Qn-1)

JZ Begin

JMP M1

Include stack.asm

END

Построение счетчика на регистровой паре.

Счетчик на одном регистре обеспечивают к-счета =28=256, поэтому счетчик строится на регистровой паре к-счета =216=65536.

При построении такого счетчика пользователь (разработчик программы) должен на программном уровне сформировать признак нулевого значения в регистровой паре, поскольку на аппаратном уровне в регистре признаков признак нулевого значения , только для одного регистра.

Счетчики на регистровой паре применяются в программах временной задержки.

Рассмотрим фрагмент программы временной задержки

DEL equ 0608C h

Begin :

MOV B,C

CALL DELAY

DELAY LXI B,DEL ;(BC)DEL

NOP

NOP

DCX B ;(BC)(BC)-1

MOV A,C

ORA B

JNZ DELAY

JMP Begin

Построение счетчиков табличным методом

Принцип построения :

В ЗУ формируется таблица в которой по адресу соответствующему текущему состоянию записано число которое формирует следующее значение счетчика.

Рассмотрим пример реализации счетчика табличным методом с произвольным порядком смены значения счетчика.

Счетчик должен выдавать следующие значения

Q0=4

4014128

Построение таблицы заполняющего устройства.

MVI C,Q0 ; (C)(Q0)

M1 OUT OUTPORT3

LXI H,NAT ;(HL)NAT адрес 0 ЯП

MVI B,0 ;(B)0

DAD B ;(HL)(HL) + (BC)

MOV C,M ; (C)([HL])

MOV A,C

JMP M1

NAT db 00 Eh,0,0,0,0,0,0,0,4,0,0,0,8,0,Ch

END

Применение управляющих сигналов для изменения процесса выполнения программы.

Основной задачей МПС является обработка информации , в зависимости от сложившейся ситуации(для системы управления).

Для изменения процесса управления вводятся сигналы управления .В программе необходимо выделить эти сигналы и опознать его значение , и на основе опознания изменить процесс работы прграммы.

Разработать управляемый счетчик на вход МПС подается 2 сигнала.

Х1 – установка счетчика в Q0, если Х1 = 0

Х2 – остановка счетчика , если Х2 = 0

Рассмотрим выделение и опознание этих сигналов

|

_ |

_ |

X2 |

X1 |

_ |

_ |

_ |

0 0 0 1 0 0 0

ANI 0 10h

2. Опознание Х1

JNZ <метка> если Z=0

……………….. если Z=1

3. Выделение Х2

ANI 20h

4. Опознание Х2

JNZ <метка> если Z=0

………………. если Z=1

Микроконтроллеры

-

Определение и общая структура микроконтроллера (МК).

-

Архитектура и работа микроконтроллера AVR «Atmel».

Определение:

Микроконтроллер- это самостоятельная микропроцессорная система (МПС),

которая содержит центральный микропроцессор, вспомогательные схемы и устройства ввода/вывода, размещённые в одном корпусе. Это определение справедливо к 8 разрядным МК.

Классификация микроконтроллеров:

По архитектуре.

1) Принстонская архитектура (фон Неймановскаская )

Пример МК: КР380, Z-80

В данной программе ОЗУ и стек находятся в общем запоминающем устройстве (ЗУ) и считывание происходит по единой шине данных.

Преимущества :

простота реализации и более гибкое применение программных процедур.

Недостатки :

небольшие скорости обработки информации.

-

Гарвардская архитектура.

Хранение RAM и стека в отдельных блоках и подведены отдельные шины к этим блокам.

Преимущества :

быстродействие, т.е. меньшее количество тактов.

Недостатки :

Сложность технической реализации и менее гибкое выполнение некоторых программных процедур.

Классификация по функциональным предназначениям.

-

Встраиваемые МК (как правило 8-и разрядные)

-

16 и 32 разрядные МК (на нескольких чипах)

-

Цифровые сигнальные процессоры (DSP)

Встраиваемые МК – обеспечение управления объектами и связь с внешними устройствами (сотовые телефоны, ТВ пульт, приёмники)

16 и 32 разрядные МК имеют внешнюю память, не только ПЗУ, но и ОЗУ. Эти МК используются там, где требуются большие объёмы памяти, которые как правило поступают с 8 разрядного МК. Они имеют дисплеи и встраиваемые программаторы.

Программное устройство, позволяющее записывать программу с ПК в МК.

DSP процессоры – применяются для программирования цифровых фильтров, а так же в качестве шумоподавляющих устройств.

Состав микроконтроллеров :

-

Блок начального запуска процессора (reset)

-

Генератор тактовых импульсов

-

Центральный процессор. (ПЗУ (EPROM и EEPROM))

-

ОЗУ (память RAM)

-

Устройство ввода/вывода.

-

Таймеры.