- •Раздел 1. Общеобразовательные дисциплины

- •Раздел 2. Специальные дисциплины

- •Раздел 1. Общеобразовательные дисциплины

- •1.Основные понятия теории вероятностей. Случайные события, случайные величины. Функция распределения вероятностей, плотность распределения вероятностей.

- •2.Среднее значение (момента) случайных величин. Математическое ожидание, дисперсия.

- •3. Характеристическая функция случайных величин.

- •4. Нормальное (Гауссовское) распределение случайных величин. Плотность распределения и характеристическая функция момента.

- •5. Независимость случайных величин. Совместное распределение двух случайных величин. Условное распределение.

- •6. Семиуровневая модель osi/iso (гост р исо/мэк 7498-1-99).

- •Взаимодействие уровней модели osi

- •Уровень представления данных (Presentation layer)

- •Сеансовый уровень (Session layer)

- •Транспортный уровень (Transport Layer)

- •Сетевой уровень (Network Layer)

- •Канальный уровень (Data Link)

- •Физический уровень (Physical Layer)

- •7. Технико-экономические аспекты создания программного обеспечения вс. Оценка стоимости программной разработки.

- •8. Распределение затрат по фазам и видам работ программной разработки.

- •9. Компилятор в языках высокого уровня. Функции. Виды компиляторов.

- •Функции

- •Компиляторы

- •10. Ассемблер. Основные языковые конструкции. Необходимость двухпроходной трансляции. Основные работы, выполняемые транслятором. Таблицы транслятора.

- •11. Формальный язык. Грамматика. Сентенциальная форма. Нисходящий и восходящий анализ.

- •Грамматика

- •12. Понятие алгоритма и его свойства. Нормальные алгоритмы Маркова.

- •13. Иерархия запоминающих устройств. Кэш-память. Работа с кэш-памятью.

- •14. Прерывания. Классификация прерываний. Организация обработки прерываний.

- •15. Виды параллелизма. Векторная и конвейерная обработка. Классификация вычислительных комплексов по сочетанию потоков данных и потоков команд.

- •16. Информационная интегрированная среда предприятия. Общая база данных об изделиях (обди). Разделы обди.

- •17. Электронный документ. Технический электронный документ: форма представления, виды, жизненный цикл.

- •18. Электронная цифровая подпись. Суть и процесс использования электронной цифровой подписи.

- •19. Автоматизированные информационные системы. Цели и методы автоматизации.

- •20. Автоматизированные информационные системы. Математическое и программное обеспечение. Математическая модель. Программное изделие.

- •21. Свободное программное обеспечение: суть, области и проблемы использования.

- •22. Жизненный цикл программного обеспечения. Длительность. Состав. Стадии сопровождения.

- •Раздел 2. Специальные дисциплины

- •1. Модуль в языке System Verilog. Определение модуля, его применение. Задание портов и параметров.

- •2. Типы данных. Wire, reg, logic. Массивы. Строковый тип. Задание числе (в двоичном, десятичном, шестнадцатиричном виде).

- •3. Примитивы, типы примитивов. Объявление и применение примитивов.

- •4. Процедурные блоки (initial и always). Операторы управления временем.

- •Управление временем

- •5. Процедурные операторы. Операторы условного перехода. Операторы цикла. Операторы назначения. Оператор непрерывного назначения.

- •6. Маршрут проектирования программ плис. Средства разработки и проверки. Структура плис. Временные задержки сигналов

- •7. Математическое, программное и информационное обеспечение сапр. Математическая модель. Программное изделие.

- •8. Виды обеспечений, типы подсистем сапр. Общие требования к типовым сапр рэа.

- •9. Принципы измерения вектора движения ка

- •10. Геоцентрическая инерциальная система координат. Прямоугольные, сферические и геодезические координаты

- •11. Классификация орбит ка по параметрам движения. Параметры орбиты по Кеплеру.

- •12. Четыре основных свойства по.

- •13. Каскадная и спиральная модель жизненного цикла программного обеспечения

- •V модель (разработка через тестирование)

- •14. Биологический нейрон. Математическая модель нейрона. Связь искусственных нейронных сетей (инс) с другими дисциплинами. Проблемы, решаемые в контексте инс.

- •15. Архитектура нейронных сетей. Однослойный персептрон. Функции активации. Многослойный персептрон.

- •16. Понятие обучения. Методы обучения. Обучение персептрона. Процедура обратного распространения.

- •Метод к- ближайших соседей

- •Процедура обратного распространения

- •17. Гипотеза Хебба. Гипотеза ковариации. Конкурентное обучение.

- •18. Понятие vc-измерения (Вапника-Червоненкиса). Оценки обобщающей способности в задаче классификации. Теорема об универсальной аппроксимации.

- •19. Сети с локальным базисом. Сравнение сетей rbf с многослойным персептроном.

- •20. Сети Кохонена. Формализация задачи классификации для сети Кохонена. Алгоритм классификации для сети Кохонена.

- •21. Обучение Больцмана. Стохастические модели. Правило обучения Больцмана. Машина Больцмана.

- •22. Нейрокомпьютеры. Основные понятия. Классификация нейрокомпьютеров.

- •1. Что такое нейрокомпьютер?

- •2. Нейронные сети - основные понятия и определения

- •3. Модели нейронных сетей

- •3.1. Модель Маккалоха

- •3.2. Модель Розенблата

- •3.3. Модель Хопфилда

- •3.4. Модель сети с обратным распространением

- •4. Задачи, решаемые на основе нейронных сетей

- •5. Способы реализации нейронных сетей

- •6. Выводы

6. Маршрут проектирования программ плис. Средства разработки и проверки. Структура плис. Временные задержки сигналов

Маршрут проектирования цифровых устройств на базе ПЛИС XILINX

Для реализации заданного цифрового устройства комбинационного или последовательностного типа в кристалле ПЛИС XILINX необходимо выполнить следующие этапы проектирования:

1. Создать новый рабочий проект, выбрав семейство и тип ПЛИС, а также средства синтеза.

2. Описать проектируемое устройство в схемотехнической, графической, алгоритмической или текстовой форме.

3. Выполнить синтез устройства.

4. Осуществить трассировку и размещения рабочего проекта в кристалл ПЛИС.

5. Провести проверку проекта методами функционального и временного моделирования.

6. Выполнить загрузку рабочего проекта в кристалл (запрограммировать ПЛИС).

Программные средства разработки и проверки систем на ПЛИС.

Для создания управляющих файлов для программирования ПЛИС можно использовать некоторые из систем схемотехнического проектирования общего назначения, например OrCAD 9.2 фирмы Cadence. Однако ведущие фирмы производители ПЛИС Altera, Xilinx, Actel предлагают свои собственные среды проектирования, причем некоторые их них распространяются свободно, например система проектирования MAX+PLUS II фирмы Altera.

Процедуру разработки нового проекта от концепции до завершения можно упрощённо представить следующим образом:

Создание требуемой структуры проекта можно выполнить следующим образом:

с помощью её описания в схемном редакторе в виде классического представления на основе стандартных логических элементов и устройств;

описания структуры на одном из языков HDL, например, на языке VHDL или Verilog;

с помощью сигнального редактора.

Назначение семейства ПЛИС для проекта;

Компиляция созданного файла описания структуры, в результате которой получаем файл для программирования, выбранной ПЛИС.

В случае успешной компиляции возможен временной анализ.

Программирование ПЛИС, с помощью несложных устройств сопряжения с ПЭВМ.

Проверка работоспособности устройства, в случае ошибок, корректируем структуру и возвращаемся к пункту 3.

Загрузку готового проекта в ПЛИС или конфигурационное ПЗУ выполняют с помощью программатора, в простейшем случае это может быть просто кабель, подключающийся к принтерному порту ПЭВМ.

Структура ПЛИС

Программируемые логические интегральные схемы (ПЛИС)

представляют собой БИС с регулярной структурой, которые могут

программироваться пользователем для выполнения заданной функции. По сравнению с другими микроэлектронными технологиями, в том числе и другими классами СПИС, технология ПЛИС обеспечивает рекордно-короткий проектно-технологический цикл (несколько часов/ дней), минимальные затраты на проектирование, максимальную гибкость при модификации аппаратуры. При этом весь проектно-технологический цикл выполняется разработчиком РЭА на одном рабочем месте.

Структура ПЛИС основана на фундаментальных понятиях алгебры логики (булевой алгебры) и содержит следующие логические элементы:

— логическое «И»(коньюнкторы);

— логическое «ИЛИ» (дизъюнкторы);

— логическое «НЕ» (инверторы);

— буферные элементы с прямыми, инверсными и тристабильными выходами;

— «Исключающее ИЛИ»;

— триггеры D‑ и T‑типа;

— мультиплексоры конфигурации.

Поскольку любая логическая функция может быть представлена в виде суммы произведений —дизъюнктивной нормальной формы (ДНФ), базовыми структурными компонентами ПЛИС являются матрицы элементов «И»и «ИЛИ». На выходе матриц расположены так называемые макроячейки (Macrocells), конфигурация которых зависит от типа ПЛИС. Макроячейки могут содержать различные триггеры, тристабильные буферы, элементы управления полярностью сигнала и др. Пути прохождения сигнала в макроячейке (конфигурация) могут быть жестко заданы структурой ПЛИС или управляться посредством мультиплексоров.

Размерность логических матриц и конфигурация макроячеек определяют степень интеграции и функциональные возможности ПЛИС.

позволяющие использовать текущие состояния и форПЛИС также содержат многочисленные обратные связи (ОС), мировать последовательностные автоматы различных классов.

Обобщенная структура ПЛИС приведена на рис.2.

Надписи: логические матрицы “И” и “ИЛИ”; Макроячейки.

Основным программируемым компонентом ПЛИС являются логические матрицы. Изначально оно обеспечивают соединение любого сигнала со входа или ОС с любым коньюнктором или дизъюнктором. В зависимости от требуемых логических функций некоторые из этих соединений разрываются, а некоторые остаются и служат для коммутации сигналов. Возможность разрыва обеспечивается наличием программируемого элемента (перемычки) в местах соединения сигнальных линий. В зависимости от технологии изготовления ПЛИС перемычка представляет собой плавкую металлическую перемычку или ячейку памяти.

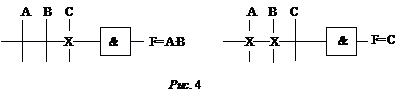

На рис. 3 условно изображен один из коньюнкторов матрицы «И». В ПЛИС такой коньюнктор называется термом. В «чистом» (незапрограммированном) состоянии каждый из сигналов A, B, C является входом коньюнктора, образуя логическую функцию «3И».

Разрывая одну или несколько перемычек (на рисунках они обозначаются символом "X"), можно получить любую коньюнкцию от этих сигналов.

Примеры приведены на рис.4.

В ПЛИС каждый терм содержит не только прямые, но и инверсные линии сигналов (рис. 5). В общей сложности количество входов каждого терма достигает 100 и выше.

Матрицы логического «ИЛИ» в ПЛИС бывают двух видов: программируемые и фиксированные. Программируемые матрицы «ИЛИ» аналогичны матрице «И» и изначально коммутируют любой терм с любым дизъюнктором (рис.6).

Фиксированные матрицы «ИЛИ» обеспечивают соединение каждого дизъюнктора со строго определенными термами (рис.7). Количество таких термов, как правило, составляет от 8 до 16. Фиксированные матрицы «ИЛИ» менее универсальны, но проще и понятнее для проектирования.

Выходной сигнал логических матриц попадает в макроячейку и может быть сохранен в памяти триггера, выведен на контакт или возвращен через ОС в матрицу «И». На рис.8 приведена макроячейка ПЛИС 85C220/85C224 фирмы INTEL.

Символом «P» обозначены программируемые элементы (перемычки конфигурации). В зависимости от состояния перемычкиP1 вход B элемента «исключающее ИЛИ» коммутируется либо с низким (L), либо с высоким (H) логическим уровнем. В соответствии с этим сигнал либо сохраняет свою полярность, либо инвертируется (рис.9).

Перемычка P2 управляет сигналом выхода и ОС: в зависимости от ее состояния этот сигнал снимается либо с комбинационной линии (дизъюнктор- «исключающее ИЛИ»), либо с выхода триггера.

При «закрытом» тристабильном буфере выходной контакт макроячейки можно использовать в качестве входного.

Некоторые другие ПЛИС имеют макроячейки с более сложной и гибкой структурой, содержащие до 5 перемычек конфигурации. Количество макроячеек в ПЛИС составляет от 8 до 100 и более.

Причины временных задержек сигналов в ПЛИС

задержка на элементах

задержка распространения

задержки вх и вых сигналов