- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

Сумматоры

Четырехразрядный и восьмиразрядный сумматоры

(ADD4 и ADD8)

Условные графические обозначения сумматоров ADD4 и ADD8 приведены на рис. П.1.35.

Сумматоры складывают два операнда А и В с учетом состояния входа CI. На выходах сумматоров формируется сумма S, сигнал переноса (CO — carry-out) или сигнал переполнения (OFL — overflow). В зависимости от того, какое толкование пользователь дает операндам А и В, он может использовать или выходы S и CO

или S и OFL (табл. П.1.15).

Рис. П.1.35. Условное графическое обозначение сумматоров ADD4 и ADD8: А, В — входы данных; CI — вход переноса; S — сумма входных сигналов; OFL — выход переполнения (для операндов со знаком, представленных в дополнительном коде); СО — выход переноса (для операндов без знака)

159

|

|

|

Таблица П.1.15 |

Использование выходов CO и OFL сумматоров ADD4 и ADD8 |

|||

|

|

|

|

S |

СО |

OFL |

Режим работы |

A+B+CI |

0 |

X |

Суммирование двоичных кодов (S < 16 для |

|

|

|

ADD4 и S < 256 для ADD8) |

A+B+CI |

1 |

X |

Суммирование двоичных кодов (S ≥ 16 для |

|

|

|

ADD4 и S ≥ 256 для ADD8) |

A+B+CI |

X |

0 |

Суммирование двух операндов со знаком, пред- |

|

|

|

ставленных в дополнительном коде (S > – 9 или |

|

|

|

< 8 для ADD4; S > – 129 или < 128 для ADD8) |

A+B+CI |

X |

1 |

Суммирование двух операндов со знаком, пред- |

|

|

|

ставленных в дополнительном коде (S > 7 или |

|

|

|

< – 8 для ADD4; S > 127 или < – 128 для ADD8) |

Данные сумматоры могут использоваться в двух режимах: или как сумматоры двоичных кодов, или как сумматоры чисел, представленных в дополнительном коде. В последнем случае крайний левый разряд операндов и результата является знаком числа. Функциональное различие между этими режимами состоит в определении «переполнения».

Если интерпретируете операнды как двоичные коды, то переполнение фиксируется на выходе СО, а состояние выхода OFL игнорируется (см. табл. П.1.35).

Если операнды рассматриваюся как числа в дополнительном коде, то переполнение как положительное, так и отрицательное определяется на выходе OFL в виде единичного сигнала, а состояние выхода СО игнорируется (см. табл. П.1.35).

Счетчики

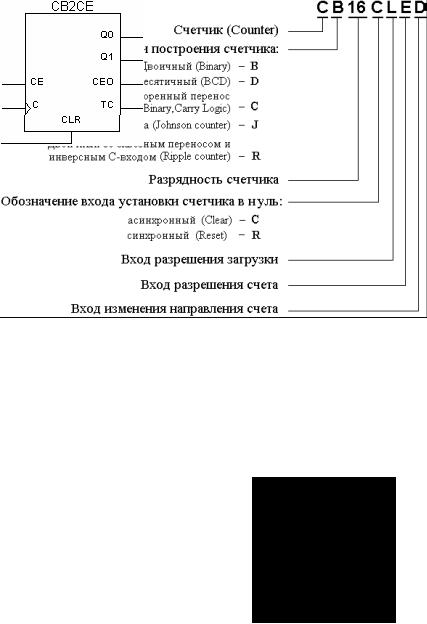

Библиотека элементов содержит большое количество разнообразных счетчиков. Расшифровка обозначения счетчиков приведена на рис. П.1.36.

Двоичные счетчики в библиотеке элементов имеют разрядность 2, 4, 8 и 16. Их построение однотипно, поэтому рассмотрение двоичных счетчиков будет проведено на примере двухразрядных двоичных счетчиков с различным набором микроопераций.

160

Рис. П.1.36. Обозначение счетчиков

Двоичный счетчик с асинхронным сбросом и входом разрешения счета (СВ2СЕ, СВ4СЕ, СВ8СЕ, СВ16СЕ)

Условное графическое обозначение двухразрядного двоичного счетчика СВ2СЕ приведено на рис. П.1.37, а его внутренняя структура — на рис. П.1.38.

Рис. П.1.37. Условное графическое обозначение счетчика СВ2СЕ: С — тактовый вход; СЕ — вход разрешения счета; CLR — вход сброса; Q0 — Q1 — выходы (0 — 1 разряды); ТС — выход переноса (выход завершения счета); СЕО — выход разрешения счета (СЕО = ТС & СЕ)

161

Рис. П.1.38. Внутренняя структура счетчика СВ2СЕ

Вход С является тактовым входом счетчика. У всех библиотечных счетчиков имеется также вход СЕ (разрешение счета). При низком уровне сигнала на этом входе счетчик не изменяет свое состояние при поступлении тактового сигнала. Выход CEO (Clock Enable Output) принимает то же значение, что и вход СЕ и служит для каскадного соединения счетчиков. Выход ТС (Terminal Count) принимает высокое активное состояние в момент перехода счетчика к последнему разрешенному состоянию.

Многоразрядные счетчики получают путем соединения выхода CEO одного счетчика с входом CE следующего и объединением входов C и CLR всех счетчиков соответственно.

Двоичный счетчик с параллельной загрузкой, асинхронным сбросом и входом разрешения счета (СВ2СLЕ, СВ4СLЕ, СВ8СLЕ, СВ16СLЕ)

Условное графическое обозначение двухразрядного двоичного счетчика СВ2СLЕ показано на рис. П.1.39. Микрооперации, выполняемые счетчиком СВ2СLЕ, приведены в табл. П.1.16, а его внутренняя структура — на рис. П.1.40.

162

Рис. П.1.39. Условное графическое обозначение счетчика СВ2СLЕ: С — тактовый вход; СЕ — вход разрешения счета; L — вход разрешения параллельной загрузки; CLR — вход сброса; DO — D1 — параллельные входы данных; Q0 — Q1 — выходы (0 — 1 разряды); ТС — выход переноса (выход завершения счета); СЕО — выход разрешения счета (СЕО = ТС & СЕ)

Таблица П.1.16

Микрооперации счетчика СВ2СLЕ

|

|

|

Входы |

|

Микрооперация |

||

CLR |

|

L |

|

CE |

C |

||

|

|

|

|

||||

1 |

|

X |

|

X |

X |

Асинхронный сброс в нуль |

|

0 |

1 |

|

X |

0/1 |

Параллельная загрузка |

||

0 |

0 |

|

1 |

0/1 |

Счет |

||

0 |

0 |

|

0 |

X |

Хранение |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. П.1.40. Внутренняя структура счетчика СВ2СLЕ

163

Двоичный реверсивный счетчик с параллельной загрузкой, асинхронным сбросом и входом разрешения счета

(СВ2СLЕD, СВ4СLЕD, СВ8СLЕD, СВ16СLЕD)

Условное графическое обозначение двухразрядного двоичного счетчика СВ2СLЕD показано на рис. П.1.41. Микрооперации, выполняемые счетчиком СВ2СLЕD, приведены в табл. П.1.17, а его внутренняя структура — на рис. П.1.42.

|

|

|

|

|

|

Рис. П.1.41. Условное графическое обозначе- |

||

|

|

|

|

|

|

ние счетчика СВ2СLЕD: С — тактовый вход; |

||

|

|

|

|

|

|

СЕ — вход разрешения счета; L — вход раз- |

||

|

|

|

|

|

|

решения параллельной загрузки; UP — вход |

||

|

|

|

|

|

|

изменения направления счета; CLR — вход |

||

|

|

|

|

|

|

сброса; DO — D1 — параллельные входы |

||

|

|

|

|

|

|

данных; Q0 — Q1 — выходы (0 — 1 разряды); |

||

|

|

|

|

|

|

ТС — выход переноса (выход завершения |

||

|

|

|

|

|

|

счета); |

СЕО — выход разрешения счета |

|

|

|

|

|

|

|

(СЕО = ТС & СЕ) |

||

|

|

|

|

|

|

|

Таблица П.1.17 |

|

|

|

|

|

|

|

|

||

|

|

|

Микрооперации счетчика СВ2СLЕD |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Микрооперация |

|

CLR |

L |

CE |

C |

UP |

||||

|

||||||||

1 |

X |

X |

X |

X |

Асинхронный сброс в нуль |

|||

0 |

1 |

X |

0/1 |

X |

Параллельная загрузка |

|||

0 |

0 |

1 |

0/1 |

1 |

Счет на увеличение |

|||

0 |

0 |

1 |

0/1 |

0 |

Счет на уменьшение |

|||

0 |

0 |

0 |

X |

X |

Хранение |

|||

164

Рис. П.1.42. Внутренняя структура счетчика СВ2СLЕD