- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

Функция EXT добавляет к операнду типа std_logic_vector слева столько нулей, чтобы в результирующем векторе было общее число разрядов, равное второму операнду типа integer. Аналогично функция SXT добавляет слева разряды, равные старшему — знаковому разряду операнда. Например:

ЕХТ("10",5) = "00010", |

SXT("10",5) = "11110" |

Пакеты std_logic_signed и std_logic_unsigned

включают, в основном, такие же функции, как и пакет std_logic_arith, но относящиеся к операндам типа signed и unsigned соответственно. Но другим операндом функции двух аргументов может быть операнд типа std_logic_vector. Эти пакеты обычно применяют в тех объектах проекта, в которых используется или тип signed или тип unsigned.

Библиотеки и пакеты

VHDL-библиотека (library) — место, где компилятор VHDL хранит информацию об отдельном варианте проекта, включая промежуточные файлы, используемые при анализе, моделировании и синтезе в рамках данной разработки. Место библиотеки в файловой системе компьютера зависит от реализации. Для очередного VHDL-проекта компилятор автоматически создает библиотеку под именем "work" и использует ее.

У законченного VHDL-проекта обычно бывает много файлов, каждый из которых содержит различные компоненты проекта, включая объекты и архитектуры. Анализируя отдельные файлы, компилятор помещает результаты в библиотеку "work", а также ищет в этой библиотеке необходимые определения, например другие объекты. С учетом этого большой проект можно разбить на несколько файлов; компилятор найдет все, что нужно, по внешним указателям.

Но не вся необходимая информация может находиться в библиотеке "work". Например, разработчик может опираться на определения и функциональные модули, общие для некоторого семейства различных проектов. У каждого проекта есть своя собственная библиотека "work" (обычно это подкаталог внутри всего каталога, относящегося к данному проекту), но в нем должны быть ссылки на общую библиотеку, содержащую совместно используемые определения. Даже в малых проектах может использоваться библио-

134

тека, которая содержит, например, стандартные определения IEEE. Разработчик может присвоить имя такой библиотеке с помощью предложения library (library clause) в начале соответствующего файла. Например, библиотеку IEEE можно задать фразой:

library ieee;

Предложение "library work;" помещается в начале каждого файла VHDL-проекта неявно.

Присвоение имен библиотекам проекта обеспечивает доступ к любым ранее проанализированным и запомненным объектам и архитектурам, но не к определениям типов и тому подобному. Эту функцию выполняют «пакеты» и «предложения use».

VHDL-пакет (package) — файл, содержащий определения элементов, которые могут быть использованы другими программами. В пакет можно включить элементы такого рода, как сигнал, тип, константа, функция, процедура и объявления компонентов.

Помещенные в пакет сигналы являются «глобальными» и доступны любому VHDL-объекту, использующему этот пакет. Типы и константы, упомянутые в пакете, известны в любом файле, использующем этот пакет. Аналогично, из файлов, использующих данный пакет, можно вызвать перечисленные в нем функции и процедуры, а архитектуры, опирающиеся на этот пакет, могут «обрабатывать» включенные в него компоненты, описываемые в следующем разделе.

Проект может «использовать» тот или иной пакет, если в начало файла, относящегося к данному проекту, помещено предложение use (use clause). Например, чтобы воспользоваться всеми определениями пакета, содержащего стандарт IEEE 1164, следует написать:

use ieee.std_logic_1164.all;

Здесь "ieee" — имя библиотеки, ранее введенное предложением library. В этой библиотеке файл с именем "std_logic_l164" содержит желаемые определения. Приставка "all" велит компилятору использовать все определения этого файла. Вместо "all" можно написать имя какого-то одного элемента, когда необходимо использовать только его определение, например:

use ieee.std_logic_1164.std_ulogic;

Эта фраза обеспечит доступ только к определению типа std_ulogic, без учета всех других родственных типов и функций. Однако, записывая подряд несколько предложений "use", можно добавить использование и других определений.

135

Приложение 1

БИБЛИОТЕЧНЫЕ ЭЛЕМЕНТЫ СХЕМНОГО РЕДАКТОРА

Данное приложение содержит краткие сведения по тем функциональным группам библиотечных элементов, которые используются при выполнении технического задания на проектирование процессора.

Библиотечные элементы схемного редактора САПР XILINX FOUNDATION разбиты на следующие основные группы (см.

рис. 10):

Gate — логические элементы; Flip-Flop/Latch — триггеры/защелки; MUX/DMUX — мультиплексоры; Coder/Decoder — дешифраторы;

Arithmetic Circuit — арифметические устройства; Counter — счетчики;

Register — регистры; Memory — память.

Элементы, включенные в библиотеку, являются либо базовыми элементами, либо макроэлементами. Базовый элемент (Primitive) — такой элемент, который не может быть разбит на меньшие компоненты. Макроэлемент (Macro) — элемент, имеющий внутреннюю структуру, состоящую из базовых элементов. Внутреннюю структуру макроэлемента всегда можно увидеть в схемном редакторе, используя команду Hierarchy Push/Pop.

Рассмотрим отдельные элементы, входящие в состав указанных групп. Как правило, в состав каждой группы входят элементы одного типа, различающиеся разрядностью или количеством входов. Разрядность указывается цифрой в обозначении компонента.

Логические элементы

Группа Gate содержит следующий набор логических элементов:

•инвертор НЕ (INV);

•элементы И (конъюнктор, AND) с инверсными и не инверсными входами от 2 до 9;

136

•элементы ИЛИ (дизъюнктор, OR) с инверсными и не инверсными входами от 2 до 9;

•элементы ИНЕ (NAND) с инверсными и не инверсными входами от 2 до 9;

•элементы ИЛИНЕ (NOR) с инверсными и не инверсными входами от 2 до 9;

•элементы “Исключающее ИЛИ” (сложение по модулю 2, XOR) с числом входов от 2 до 9;

•элементы, выполняющие функцию логическая равнозначность (XNOR) с числом входов от 2 до 9;

•элементы 2-2И-2ИЛИ (SOP4) с инверсными и не инверсными входами;

•элементы 1-2И-2ИЛИ (SOP3) с инверсными и не инверсными входами.

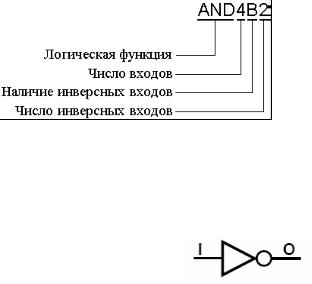

Расшифровка обозначений эементов этой группы достаточно проста, поскольку тип элемента явно указан в его названии, а число обозначает количество входов. Кроме того, у элементов некоторые входы могут быть проинвертированы, что отмечается символом B в обозначении элемента. Пример соглашения, принятого для обозначения логических элементов, приведен на рис. П.1.1.

Рис. П.1.1. Обозначение логических элементов

Инвертор НЕ (INV)

Условное графическое обозначение инвертора, приведено на рис. П.1.2. Инвертор является базовым элементом.

Рис. П.1.2. Условное графическое обозначение инвертора

137

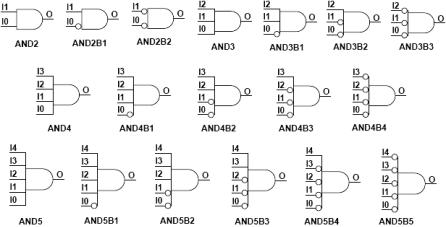

Элементы И (AND)

Условные графические обозначения элементов AND приведены на рис. П.1.3. Элементы AND до 5 входов включительно являются базовыми элементами и могут иметь инверсные входы в любой комбинации (см. рис. П.1.3).

Рис. П.1.3. Условное графическое обозначение элементов AND

Элементы AND с числом входов от 6 до 9 не имеют инверсных входов и являются макроэлементами.

Элементы ИЛИ (OR)

Условные графические обозначения элементов OR приведены на рис. П.1.4. Элементы OR до 5 входов включительно являются базовыми элементами и могут иметь инверсные входы в любой комбинации (см. рис. П.1.4).

Элементы OR с числом входов от 6 до 9 не имеют инверсных входов и являются макроэлементами.

138

Рис. П.1.4. Условное графическое обозначение элементов OR

Элементы ИНЕ (NAND)

Условные графические обозначения элементов NAND приведены на рис. П.1.5. Элементы NAND до 5 входов включительно являются базовыми элементами и могут иметь инверсные входы в любой комбинации.

Рис. П.1.5. Условное графическое обозначение элементов NAND

Элементы ИЛИНЕ (NOR)

Условные графические обозначения элементов NOR приведены на рис. П.1.6. Элементы NOR до 5 входов включительно являются

139

базовыми элементами и могут иметь инверсные входы в любой комбинации (см. рис. П.1.6). Элементы NOR с числом входов от 6 до 9 не имеют инверсных входов и являются макроэлементами.

Рис. П.1.6. Условное графическое обозначение элементов NOR

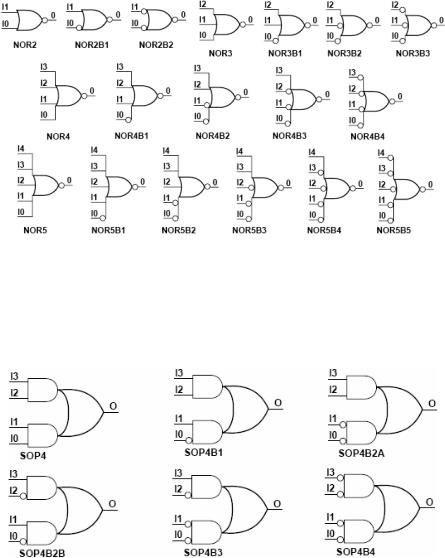

Элементы 2-2И-2ИЛИ (SOP4)

Условные графические обозначения элементов SOP4 приведены на рис. П.1.7. Элементы SOP4 являются макроэлементами и могут иметь инверсные входы в любой комбинации (см. рис. П.1.7).

Рис. П.1.7. Условное графическое обозначение элементов SOP4

140

Элементы 1-2И-2ИЛИ (SOP3)

Условные графические обозначения элементов SOP3 приведены на рис. П.1.8. Элементы SOP3 являются макроэлементами и могут иметь инверсные входы в любой комбинации (см. рис. П.1.8).

Рис. П.1.8. Условное графическое обозначение элементов SOP3

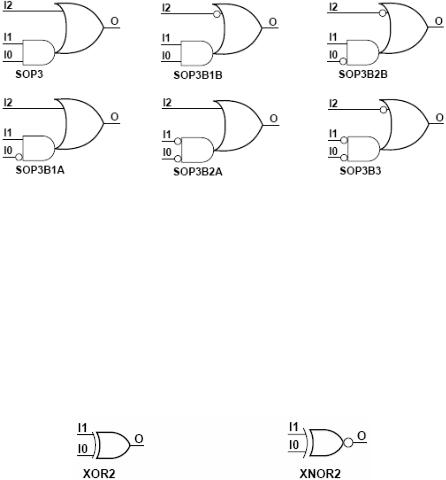

ЭлементыИСКЛЮЧАЮЩЕЕИЛИ(XOR)

иИСКЛЮЧАЮЩЕЕИЛИ-НЕ(XNOR)

Вбиблиотеке элементы «Исключающее ИЛИ» (сложение по модулю 2, XOR) и элементы «Исключающее ИЛИ-НЕ» (логическая равнозначность, XNOR) имеют число входов от 2 до 9.

Условное графическое обозначение элементов XOR2, XNOR2 с двумя входами приведено на рис. П.1.9, а их таблица истинности представлена табл. П.1.1.

Рис. П.1.9. Условное графическое обозначение элементов XOR и XNOR

141