- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

4. Выделите соответствующий файл и нажмите кнопку «Открыть». После чего в окне редактора HDL Editor появится текст описания.

Синтез макроэлемента

После того как описание макроэлемента успешно проанализировано, можно переходить к синтезу проекта. Синтез (или компиляция) представляет собой процесс перевода VHDL-файла в описание на уровне вентилей.

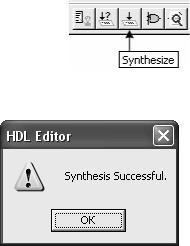

Для того чтобы начать процесс синтеза выберите пункт

Synthesize из меню Synthesis в

окне HDL Editor или нажмите пиктограмму Synthesize на панели инструментов.

При отсутствии ошибок будет выдано сообщение Synthesis successful (рис. 52).

Если по какой-либо причине компиляция невозможна, то соответствующее сообщение об ошибках будет помещено в окне ошибок в той же форме, что и при проверке синтаксиса.

Создание VHDL-макроса

VHDL-макрос (макроопределение) — макроэлемент, имеющий условное графическое обозначение. Его создание необходимо для выполнения моделирования с целью отладки описания и использования как элемента в составе устройства.

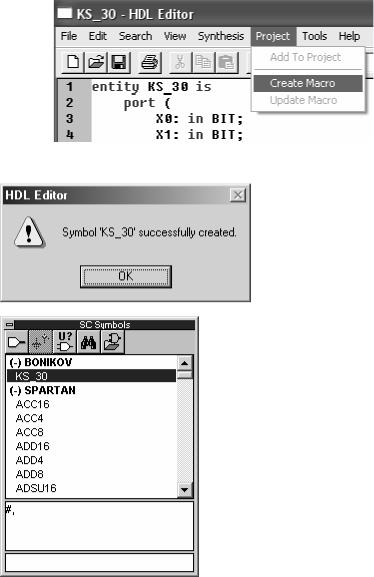

Для создания макроса выберите Create Macro из меню Project в окне редактора HDL Editor (рис. 53). Успешное завершение процедуры сопровождается выводом соответствующего сообщения (рис. 54). Макроэлемент с тем же именем, что и VHDL-файл, будет помещен в рабочую библиотеку проекта.

53

Рис. 53. Выбор команды Create Macro

Рис. 54. Сообщение об успешном завершении

процедуры создания макроса

Рис. 55. Выбор макроэлемента

вбиблиотеке элементов схемного редактора

После создания макроса команда Create Macro автоматически заменяется на команду

Update Macro.

Выбор макроса из библиотеки

Извлечение созданного макроса ничем не отличается от выбора в редакторе схем любого другого элемента (рис. 55).

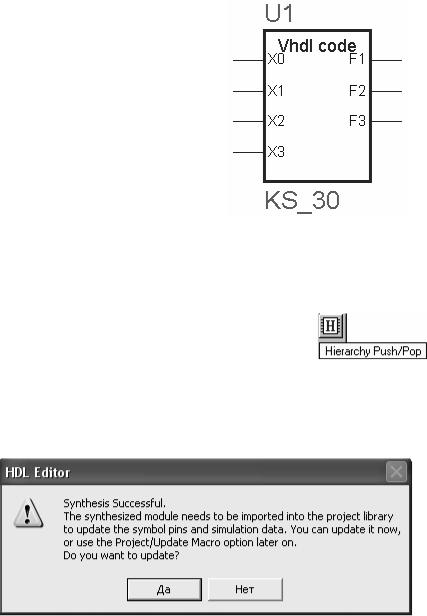

Редактирование УГО макроэлемента

Извлеченное изображение выбранного макроэлемента создано автоматически системой (рис. 56). Его целесообразно отредактировать.

54

Рис. 56. Условное графическое обозначение

Изменение условного графического изображения макроэлемента было изложено ранее (см.

с. 38).

Коррекция VHDL-описания макроэлемента

При необходимости коррекцию VHDL-описания макроэлемента можно выполнить, не выходя из редактора схем Schematic Editor.

1.Нажмите пиктограмму Hierarchy Push/Pop на вертикальной панели инструментов редактора схем и затем дважды щелкните мышью на изображении макроэлемента. Появится окно редактора HDL Editor с текстом модели.

2.Выполните необходимые исправления и после закройте окно редактора HDL Editor. Появится запрос на обновление макроса (рис. 57). Нажмите кнопку «Да». После чего произойдет автоматическое обновление макроса.

Рис. 57. Запрос на обновление макроса

55

ГРАФИЧЕСКИЙ ДИАЛОГОВЫЙ ИНСТРУМЕНТ СОЗДАНИЯ ЭЛЕМЕНТА LOGIBLOX

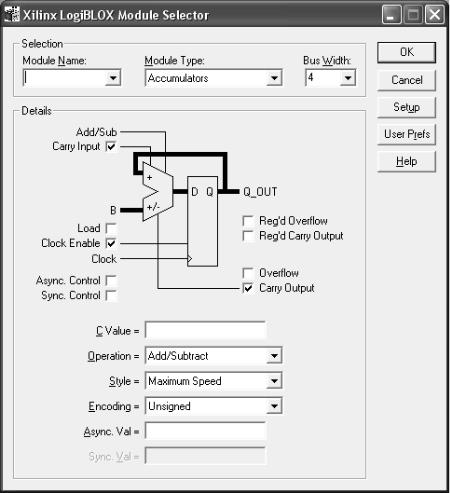

LogiBLOX — графическое средство создания параметризованных и оптимизированных под конкретную архитектуру разнообразных элементов (счетчики, память, регистры, мультиплексоры и т.д.).

Рассмотрение этого инструмента проведем на примере создания и использования синхронной оперативной памяти емкостью 16×8 слов. При проектировании цифровой аппаратуры на ПЛИС пользователь может создавать и использовать постоянную (ROM) и оперативную (RАМ) память непосредственно на кристалле ПЛИС.

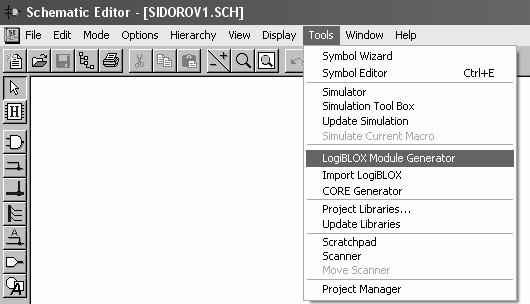

Автоматическое создание модели памяти

1.Выполните команду Tools/LogiBLOX Module Generator из ме-

ню редактора схем (рис. 58). Откроется диалоговое окно LogiBLOX Module Selector (рис. 59).

2.Откройте список типов синтезируемых элементов, щелкнув кнопку открытия в поле Module Type окна LogiBLOX Module Selector (см. рис. 59). Появится перечень названий типов элементов, модели которых могут быть автоматически созданы системой

(рис. 60).

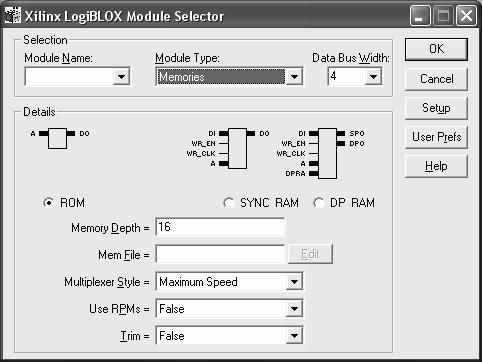

3.Выберите в этом списке группу Memories. В окне LogiBLOX Module Selector появится УГО различных типов памяти вместе с параметрами (рис. 61), которые необходимо уточнить.

4.В этом окне необходимо:

•в поле Module Name задать желаемое имя создаваемой па-

мяти;

•в поле Bus Width задать разрядность шины данных;

•в разделе Details задать:

тип памяти (для нашего примера — SYNC_RAN);

вполе Memory Dept емкость памяти в словах (емкость должна быть кратна 16, диапазон емкости от 16 до 256 слов, значение по умолчанию — 16);

вполе Mem File имя файла, в котором надо будет задать начальное состояние памяти;

остальные поля в этом разделе оставим без изменения.

56

Рис. 58. Выбор команды Tools/LogiBLOX Module Generator

Рис. 59. Окно выбора и настройки синтезируемой модели элемента

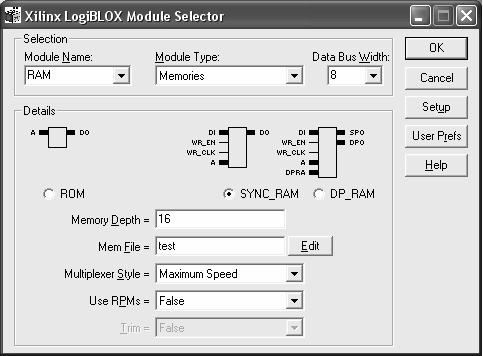

Вид окна с заданными параметрами памяти приведен на рис. 62. Для задания начального состояния памяти нажмите кнопку Edit (см. рис. 62). Появится окно текстового редактора, которое будет содержать заготовку содержимого файла задания начального со-

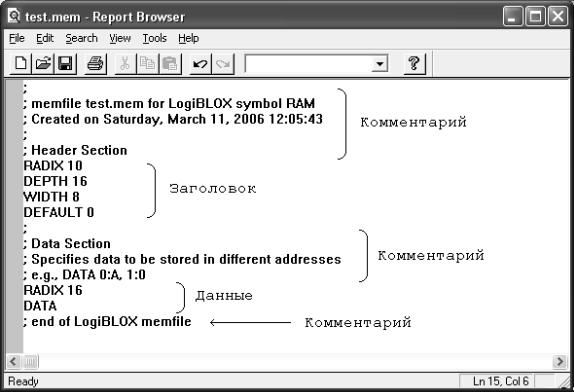

стояния памяти (рис. 63).

58

Рис. 60. Список типов синтезируемых элементов

5. Укажите в этой заготовке начальное состояние памяти. Состояние памяти задается после ключевого слова DATA, начиная с нулевого адреса, через запятую или пробел в шестнадцатеричной системе счисления.

59

Рис. 61. Окно выбора памяти

Рис. 62. Окно выбора памяти с заданными параметрами

Рис. 63. Структура файла задания начального состояния памяти

Например, необходимо следующим образом определить состояние памяти:

0C, A9, 42, 80, 00, 00, 00, 00, 00, 32, 30, 08, 0A, 00, 00, 00.

Запись в поле данных будет выглядеть так:

DATA 0C, A9, 42, 80,00, 00, 00, 00, 00, 32, 30, 08, 0A, 00, 00, 00

Возможна сокращенная запись начального состояния памяти, если состояние большинства ячеек памяти одинаково. В нашем примере это состояние равно 0 и оно определено по умолчанию (см. рис. 63). В таком случае достаточно задать состояние только тех ячеек, состояние которых отличается от 0 (наш случай). Для этого необходимо указать адрес соответствующей ячейки, затем после двоеточия ее состояние.

Сокращенная запись для нашего примера будет выглядеть так:

DATA 0C,A9,42,80, 9: 32,30,08,0A

Сформированный файл задания начального состояния памяти показан на рис. 64.

6. Сохранив набранный текст, закройте данное окно.

Примечание. Задание состояния памяти не является обязательной операцией на данном этапе. Формирование начального состояния памяти можно выполнить на любой стадии работы над проектом.

7. Нажмите кнопку OK в окне LogiBLOX Module Selector (см.

рис. 62) для завершения операции создания модели элемента. Успешное создание будет завершено соответствующим сообщением

(рис. 65).

Примечание. Элемент, созданный с использованием механизма LogiBlox, рассматривается системой как базовый элемент, т.е. вы не можете увидеть его внутреннюю структуру.

63