- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

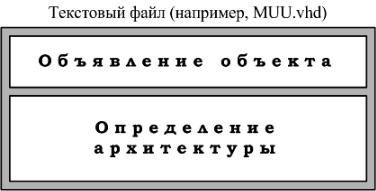

Рис. 109. Общий вид файла программы на языке VHDL

Объявление объекта в языке VHDL можно считать «оболочкой» архитектуры, скрывающей детали того, что находится внутри, но обеспечивающей «зацепки» для других модулей, использующих данный модуль. Эта идея служит основой иерархического подхода к проектированию систем: архитектура верхнего уровня может использовать (или «обрабатывать») другие объекты, оставляя архитектурные детали объектов нижнего уровня скрытыми от объектов более высокого уровня.

Интерфейс объекта проекта

Синтаксис

В листинге 3 представлен синтаксис объявления объекта. Целью объявления объекта, помимо присвоения объекту имени, является определение сигналов внешнего интерфейса или портов (ports) в части объявления объекта, которая называется объявлением портов

(port declaration).

Обратите внимание, что после заключительного signal-type нет точки с запятой; изменение порядка следования закрывающей скобки и точки с запятой после нее — типичная синтаксическая ошибка программиста, начинающего писать на языке VHDL.

103

Листинг 3. Синтаксис объявления объекта на языке VHDL

entity entity-name is

port (signal-names : mode signal-type; signal-names : mode signal-type;

. . .

signal-names : mode signal-type); end entity-name;

Кроме ключевых слов entity, is, port и end, объявление объекта содержит следующие элементы:

entity-name — выбираемое пользователем имя объекта; signal-names — список выбираемых пользователем имен

сигналов внешнего интерфейса, состоящий из одного имени или из большего числа имен, разделенных запятой;

— одно из четырех зарезервированных слов, определяющих направление передачи сигнала:

— сигнал на входе объекта;

— сигнал на выходе объекта; заметьте, что значение такого сигнала нельзя «прочитать» внутри структуры объекта; он доступен только объектам, использующим данный объект;

— сигнал на выходе объекта; в отличие от сигнала out его значение можно читать также внутри структуры данного объекта;

— сигнал, который может быть входным или выходным для данного объекта; обычно этот режим используется применительно к входам/выходам схем с тремя состояниями;

— встроенный или определенный пользователем тип сигнала.

104

Тип сигнала

Каждому сигналу (а также переменной и константе) в программе на языке VHDL необходимо поставить в соответствие тип (type). Типом определяется множество или диапазон значений, которые может принимать данный элемент, и обычно имеется набор таких операторов, как сложение, логическое ИЛИ и т.д., связываемых с данным типом.

Поскольку язык VHDL используется для представления аппаратных проектов в самых разных вариантах, средства типизации данных приобретают здесь особо важное значение. Например, они дают разработчику возможность представить группу проводников шины в виде:

•массива битов;

•целого числа.

Вязыке VHDL есть несколько предопределенных типов

(predefined types), которые поддерживают программы синтеза:

bit |

boolean |

character |

bit_vector |

integer |

|

В дальнейшем будут использованы только следующие предопреде-

ленные типы: bit, bit_vector и integer.

Тип integer определяет диапазон значений целых чисел, который простирается от –231 до +231 – 1. Данные типа bit принимают значения из множества {'0', '1'}. Битовое представление может быть громоздким, поэтому в ряде случаев целесообразно использовать векторное представление bit_vector.

Встроенные операторы для типов integer и bit приведены в табл. 1.

Таблица 1

Предопределенные операторы для типов integer и bit в языкe VHDL

|

Операторы для типа integer |

|

Операторы для типа bit |

+ |

— сложение |

not |

— инверсия |

- |

— вычитание |

and |

— И |

* |

— умножение |

or |

— ИЛИ |

/ |

— деление |

nand |

— И-НЕ |

mod |

— деление по модулю |

nor |

— ИЛИ-НЕ |

rem |

— остаток от деления по модулю |

хоr |

— ИСКЛЮЧАЮЩЕЕ ИЛИ |

abs |

— абсолютное значение |

хпоr |

— ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ |

** |

— возведение в степень |

|

|

105

В языке VHDL реализована строгая типизация. Это означает, что смешение различных типов в одной операции является ошибкой. Средства строгого контроля типов играют ответственную роль, поскольку позволяют уточнить намерения разработчика.

Пример. Текст объявления объекта на языке VHDL для структуры приведен в листинге 4.

Заметьте, что порядок следования значений в указываемом диапазоне может быть в сторону возрастания или в сторону убывания в зависимости от того, какое из ключевых слов to или downto употреблено.

Листинг 4. Объявление объекта

entity MUU_125 is port (

R, CLK, KOP, SNO: in BIT; F: in BIT_VECTOR (1 to 3); Y: out BIT_VECTOR (1 to 10);

P: out BIT_VECTOR (3 downto 0); CS: out INTEGER range 0 to 3; SKO, TPO: out BIT

);

end MUU_125;

О правилах записи программы

Как и в других языках программирования, в языке VHDL пробелы и переходы с одной строки на другую в общем случае игнорируются, и для удобства чтения их можно вставлять как угодно.

Комментарии начинаются с двух дефисов (--) и заканчиваются концом строки.

В языке VHDL определено много специальных строк символов,

называемых зарезервированными словами или ключевыми словами.

В приведенном примере имеется несколько ключевых слов: entity, port, is, in, out, to, downto, range, end. Здесь и далее зарезервированные слова выделяются жирным шрифтом.

106